# A Design of Analog Front-End with DBPSK Demodulator for Magnetic Field Wireless Network Sensors

S. Ali Hosseini Asl <sup>1</sup>, Behnam S. Rikan <sup>1,2</sup>, Arash Hejazi <sup>1,2</sup>, YoungGun Pu <sup>1,2</sup>, Hyungki Huh <sup>1,2</sup>, Yeonjae Jung <sup>1,2</sup>, Keum Cheol Hwang <sup>1</sup>, Youngoo Yang <sup>1</sup> and Kang-Yoon Lee <sup>1,2,\*</sup>

- <sup>1</sup> Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon 16419, Korea

- <sup>2</sup> SKAIChips Co., Ltd., Suwon 16419, Korea

- \* Correspondence: klee@skku.edu; Tel.: +82-31-299-4954

Abstract: This paper presents an on-chip fully integrated analog front-end (AFE) with a non-coherent digital binary phase-shift keying (DBPSK) demodulator suitable for short-range magnetic field wireless communication applications. The proposed non-coherent DBPSK demodulator is designed based on using comparators to digitize the received differential analog BPSK signal. The DBPSK demodulator does not need any phase-lock loop (PLL) to detect the data and recover the clock. Moreover, the proposed demodulator provides the detected data and the recovered clock simultaneously. Even though previous studies have offered the basic structure of the AFEs, this work tries to amplify and generate the required differential BPSK signal without missing data and clock throughout the AFE, while a low voltage level signal is received at the input of the AFE. A DC-offset cancellation (DCOC), a cascaded variable gain amplifier (VGA), and a single-to-differential (STOD) converter are employed to construct the implemented AFE. The simulation results indicate that the AFE provides a dynamic range of 0 dB to 40 dB power gain with 2 dB resolution. Measurement results show the minimum detectable voltage at the input of AFE is obtained at 20 mV peak-to-peak. The AFE and the proposed DBSPK demodulator are analyzed and fabricated in a 130 nm Bipolar-CMOS-DMOS (BCD) technology to recover the maximum data rate of 32 kbps where the carrier frequency is 128 kHz. The implemented DCOC, cascaded VGA, STOD, and the demodulator occupy 0.15 mm<sup>2</sup>, 0.063 mm<sup>2</sup>, 0.045 mm<sup>2</sup>, and 0.03 mm<sup>2</sup> of area, respectively. The AFE and the demodulator consume 2.9 mA and 0.15 mA of current from an external 5 V power supply, respectively.

Keywords: DBPSK; demodulator; AFE; magnetic field communication; wireless network sensors

# 1. Introduction

The development of wireless communication devices to monitor difficult-to-access areas (e.g., when a wireless sensor is used underground or underwater to monitor the fluency of oil, gas, etc.) has increased. The challenges of power consumption, noise, gain, linearity, and high-cost fabrication in radio frequency integrated circuit (RF IC) design led to the design of magnetic field wireless sensor networks (WSNs) as one of the alternative applications in short-range wireless communications [1–3].

Amplitude-shift keying (ASK) [4], on-off keying (OOK) [5], and phase-shift keying (PSK) [6] are some of the conventional data modulation techniques for wireless data transfer. In an ASK modulation technique, the data are carried by the amplitude. Therefore, the sensitivity of carrier amplitude to noise causes missing data in short-range applications when the input amplitude is very low. In other words, while the distance between transmitter (TX) and receiver (RX) is not very short, due to the attenuation of signal and sensitivity of carrier amplitude to noise, data would be missed. Hence, the ASK modulation technique is not recommended in this application.

To detect the data in a conventional coherent binary phase-shift keying (BPSK) demodulator, the clock first needs to be recovered to resample the BPSK signal [7]. In general,

Citation: Asl, S.A.H.; Rikan, B.S.; Hejazi, A.; Pu, Y.; Huh, H.; Jung, Y.; Hwang, K.C.; Yang, Y.; Lee, K.-Y. A Design of Analog Front-End with DBPSK Demodulator for Magnetic Field Wireless Network Sensors. *Sensors* **2022**, *22*, 7217. https:// doi.org/10.3390/s22197217

Academic Editor: Haruo Kobayashi

Received: 26 August 2022 Accepted: 21 September 2022 Published: 23 September 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). Costas loops, squaring loops, and demodulators are employed to adopt phase-lock loops (PLLs) to recover the required clock [8]. Hence, a considerable silicon die and power consumption have to be devoted to the PLL. Moreover, PLLs need a significant settling time to generate the operational clock. The proposed non-coherent DBPSK demodulator is designed based on using comparators and delay cells to digitalize input signals. In the proposed structure, there is no implemented PLL to detect data and recover clock. Furthermore, the detected data and recovered clock are generated at the same time.

Since the received analog BPSK signal at the input of the demodulator might not be large enough to guarantee the operation of the comparators (e.g., in the case of using the sensors underground or underwater), the received analog BPSK signal has to be amplified without any change in the shape of the signal. Moreover, in the proposed DBPSK demodulator, to detect the data and recover the clock, the inverted analog BPSK signal is required. Consequently, employing an analog front-end (AFE) to amplify and provide the differential analog signal is inevitable. At the interface of the architecture to the analog BPSK signal, the DC voltage of the input signal is adjusted to half of the supply voltage (VDD/2) by a DC-offset cancellation (DCOC), which is located at the first stage of the AFE. A cascaded variable gain amplifier (VGA) offers 0 dB to 40 dB of power gain to amplify the input analog signal. This variation in power gain guarantees coverage of a wide dynamic range of input voltage levels. A single-to-differential (STOD) converter is placed at the last stage of the AFE to generate the required differential analog BPSK signal.

### 2. Overall Architecture and Building Blocks

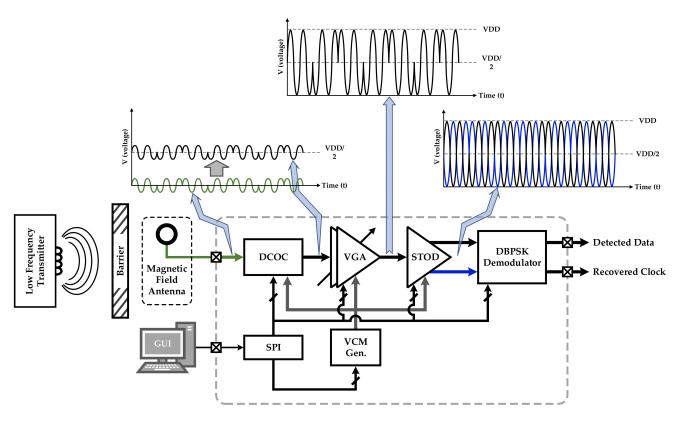

Figure 1 illustrates the overall architecture of the proposed RX, which consists of a DCOC, a cascaded VGA, a STOD, a conventional common-mode voltage generator (VCM Gen.), and a serial peripheral interface (SPI).

Figure 1. Architecture of the proposed RX.

In the proposed architecture, an external magnetic field antenna receives the transmitted analog BPSK signal from a low-frequency (LF) TX as stated in Figure 1. Depending on the distance and the barriers between the LF TX and the antenna, the attenuation of

3 of 10

the transmitted analog BPSK signal cannot be constant. In other words, the amplitude of the received signal at the antenna is variable. Therefore, a reconfigurable gain amplifier is required to provide a dynamic range of amplification of the input signal from low to high voltage levels.

As indicated in Figure 1, the DCOC is employed at the first stage to adjust the DC voltage level of the input signal to the desired VCM (VDD/2) for the subsequence stage (VGA) where operational amplifiers (Op-amps) need to offer their best performance. The required VCM of 2.5 V (VDD/2) is provided by VCM Gen. To digitalize the input analog BPSK signal through the proposed DBPSK demodulator, the amplified input analog signal and its invert are required. The STOD circuit converts the single input analog signal to the required differential signal [9]. Through the SPI, a graphic user interface (GUI) programmer on a computer controls the RX's digital controller.

# 3. Hysteresis Comparator Analysis

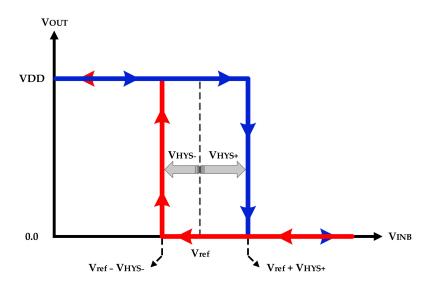

Comparators are basic circuits to convert an analog signal to its digital format. To switch the output of a comparator from 0 to VDD and vice versa, a hysteresis comparator offers the possibility of having different down ( $V_{HYS-}$ ) and up ( $V_{HYS+}$ ) threshold voltages. The loop characteristics of an inverting comparator are illustrated in Figure 2.

Figure 2. Loop characteristics of an inverting comparator.

The operation of the inverting comparator would be described in two scenarios: (1) an analog signal is applied to the negative input of the comparator, while the positive input is connected to a reference voltage ( $V_{ref}$ ). In this case, the input signal is compared with  $V_{ref}$ , and the output shows the inverted digitalized signal. (2) A differential analog sinewave signal with a DC level: in this scenario, the negative input is compared with the DC level, which can be assumed as  $V_{ref}$ . The output voltage of the inverting comparator can be described by the following expression:

$$\begin{cases} V_{INB} > V_{ref} - V_{HYS-}; V_{OUT} = 0\\ V_{INB} < V_{ref} + V_{HYS+}; V_{OUT} = VDD \end{cases}$$

(1)

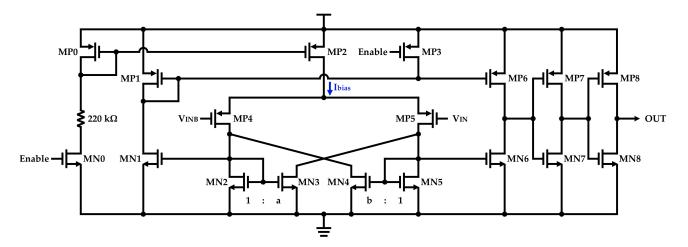

The structure of a hysteresis comparator is stated in Figure 3. In this structure,  $V_{HYS-}$  and  $V_{HYS+}$  can be defined by MN3 and MN4 [10].  $V_{HYS-}$  and  $V_{HYS+}$  can be calculated by the following expressions [10]:

$$V_{HYS-} = \sqrt{\frac{2I_{bias}}{\mu C_{ox} \left(\frac{W}{L}\right)_{4,5}}} \times \frac{\sqrt{b} - 1}{\sqrt{b+1}}$$

(2)

$$V_{HYS+} = \sqrt{\frac{2I_{bias}}{\mu C_{ox} \left(\frac{W}{L}\right)_{4,5}}} \times \frac{\sqrt{a} - 1}{\sqrt{a+1}}$$

(3)

where *a* and *b* are greater than 1 and described by the *W* ratio of MN3 with MN2 and MN4 with MN5, respectively. It is worth mentioning that the output voltage of the hysteresis comparator is dependent on the values of the input voltage at the same time and its passed time.

Figure 3. Structure of the implemented hysteresis comparator.

# 4. DBPSK Demodulator

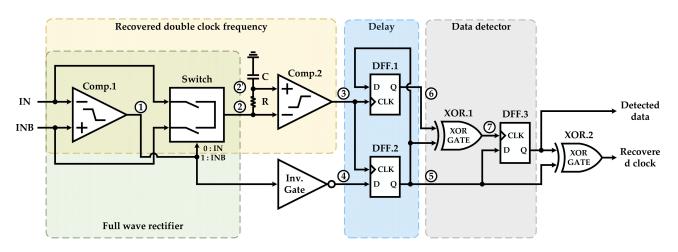

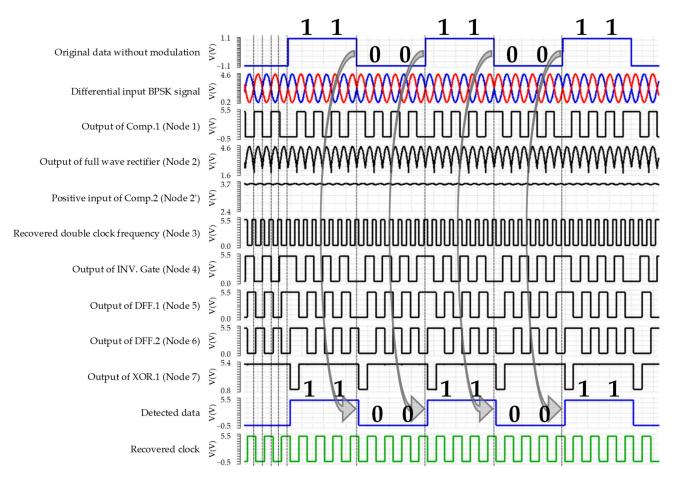

The structure of the proposed DBPSK demodulator is illustrated in Figure 4. Two hysteresis comparators, three dynamic flip-flips (DFFs), two XOR gates, and an inverter gate are formed as the building blocks of the proposed DBPSK demodulator to detect the data and recover the clock. Figure 5 depicts the simulation results of the proposed DBPSK demodulator. To detect the data and recover the clock, a double clock frequency from the differential BPSK signal is recovered by employing a full wave rectifier and a comparator (Comp.2).

Figure 4. Structure of the proposed DBPSK demodulator.

Figure 5. Simulated timing diagram of the proposed non-coherent DBPSK demodulator.

The specified full-wave rectifier in Figure 4 consists of a comparator (Comp.1) and a switch that is controlled by the output of Comp.1. The operating principles of the proposed full-wave rectifier are as follows: when the input voltage level of the negative input (IN) is greater than  $(VDD/2) + V_{HYS+}$ , the output of Comp.1 (Node 1) is 0. In this case, the switch connects the IN to the negative input of Comp.2, while if the voltage level of the negative of the comparator is VDD; hence, INB appears at the input of Comp.2 through the switch. Consequently, the output of the switch (Node 2) presents the full-wave rectified signal with DC level of VDD/2 as shown in Figure 3. The provided low-path filter (LPF) by (R = 1 M $\Omega$ ) and (C = 20 pF) at the inputs of Comp.2 ensures the voltage difference of  $\Delta V$  between the inputs of Comp.2. As the negative input swings, the Comp.2 recovers the double frequency clock with respect to crossing points (Node 3).

The implemented DBPSK demodulator using delay and a data detector monitors the location of rising and falling edges of the unmodulated data where the pulse width of the output of Comp.1 lasts longer, and some unmodulated edges are skipped. Since the double frequency clock is used to sample the BPSK signal to detect the data, the recovered clock and detected data are generated synchronously. To simulate the operation of the proposed DBSPK demodulator, the data signal is multiplied with a sinewave signal (carrier signal) to provide the required modulated signal, where the amplitude of the modulated BPSK signal is defined by the amplitude of the carrier signal. Figure 5 shows the original data signal without modulation, the differential modulated BPSK signal, the internal digitalized signals of the demodulation, the detected data, and the recovered clock.

# 5. Analog Front-End

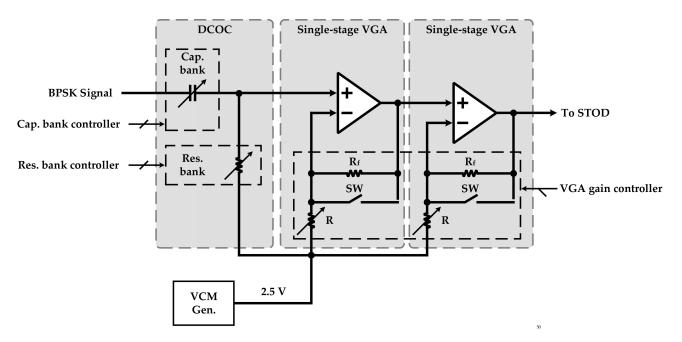

The DCOC circuit is located at the interface of the AFE to regulate the DC voltage level of the received analog BPSK signal to the desirable VCM of 2.5 V, which is generated by the conventional VCM Gen. As indicated in Figure 6, the DCOC Cap. bank (10–90 pF) blocks the DC level voltage of the input signal and adjusts the DC level voltage to 2.5 V through the DCOC Res. Bank (1–3.3 M $\Omega$ ).

Two single-stage VGAs are implemented to construct the cascaded VGA block as depicted in Figure 6. The provided power gain of a single-stage VGA by using  $R_f$  and R in the feedback is given by the following expression:

$$\frac{V_{out}}{V_{in}} = 1 + \frac{R_f}{R} \tag{4}$$

Therefore, by using a reconfigurable resistor (*R*) in the feedback path, as indicated in Figure 6, a dynamic range of power gain from 0 dB to 20 dB with 2 dB resolution is obtained. It is noteworthy that 0 dB gain is achieved when the switch (SW) connects the output of the operational amplifier (Op-Amp) to its negative input; in this condition, the VGA operates as an analog buffer. Thus, the total dynamic range of amplification from 0 dB to 40 dB of power gain is provided by the cascaded VGA to amplify the received BPSK signal. It should be noted that the cutoff frequency of DCOC and the gain of cascaded VGA are controlled through the SPI part.

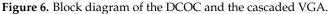

As discussed in the DBPSK demodulator section, to detect the data and recover the clock, the differential signal of the analog BPSK signal is required. The STOD consists of two analog buffers and an analog inverter to convert the single BPSK signal to its differential form as illustrated in Figure 7. The gain of the analog inverter can be written by following equation:

$$\frac{V_{out}}{V_{in}} = -\frac{R_1}{R_2} \tag{5}$$

Since the gain of the analog invert should be -1,  $R_1$  and  $R_2$  are equal. It should be noted that the required VCM for operation of the analog inverter circuit is provided by VCM Gen.

Figure 7. Block diagram of the STOD.

### 6. Experimental Results

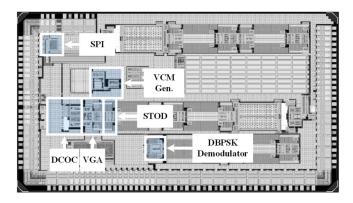

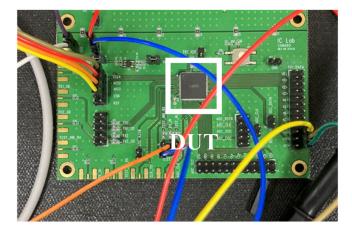

The proposed fully integrated AFE with the DBPSK demodulator for short-range magnetic field WSN is fabricated in a 130 nm Bipolar-CMOS-DMOS (BCD) technology with an active area of 0.67 mm<sup>2</sup> and 0.03 mm<sup>2</sup>, respectively. The proposed DBPSK demodulator offers 25% data-rate-to-carrier frequency (DRCF). Figure 8 indicates the location of AFE, DBPSK demodulator, SPI, and VCM Gen. in the top layout. The print circuit board (PCB) and the device under test (DUT) for measurement is stated in Figure 9. The required supply voltage is offered by an external 5 V power supply to measure the performance of the AFE and the DBPSK demodulator. The modulated BPSK signal is provided by multiplying a sinewave (carrier signal) and a pulse (data signal).

Figure 8. The top layout of the chip and location of AFE, DBPSK demodulator, SPI, and VCM Gen.

Figure 9. PCB and the device under test of the proposed architecture.

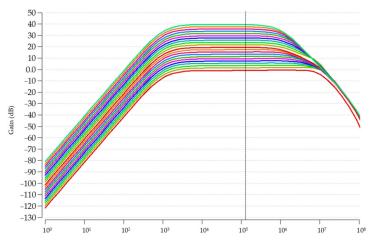

Figure 10 indicates the post-layout simulation results of the gain performance throughout the AFE, which is provided by the cascaded VGA. AFE can offer a wide range of power gain from 0 dB to 40 dB with 2 dB resolution.

Figure 10. Post-layout simulation results of the provided power gain by AFE.

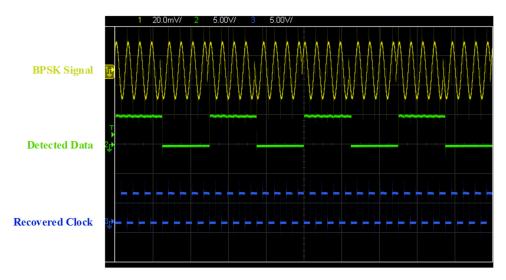

Figure 11 illustrates the measurement results of the detected data and recovered clock with 50% duty cycle. The measurement results show the received BPSK signal is successfully amplified by AFE and demodulated through the proposed DBPSK demodulator.

Figure 11. Measurement results of the device under test.

To compare the performance of the proposed DBPSK demodulator with previous structures, two figure of merits (FoMs) are suggested [11,12]. The maximum DRCF, power consumption, and occupied area are the most important factors to summarize the performance of a demodulator. Therefore, the suggested  $FoM_1$  and  $FoM_2$  can be written by following expressions [11,12]:

$$FoM_1 = \frac{DRCF}{Power(mW)} \tag{6}$$

$$FoM_2 = \frac{FoM_1}{A(\mathrm{mm}^2)} \tag{7}$$

The summarized performance of the proposed DBPSK demodulator and comparison with other studies are reported in Table 1. When compared to recent works, the proposed demodulator provides superior DRCF performance while consuming only 0.75 mW of power. Furthermore, Table 1 depicts the FoMs of the proposed DBPSK demodulator and other works for a fair comparison.

| Parameter                      | This Work | [13]   | [14]     | [15]    | [ <mark>16</mark> ] | [17]  | [18]           |

|--------------------------------|-----------|--------|----------|---------|---------------------|-------|----------------|

| Year                           | 2022      | 2013   | 2015     | 2016    | 2018                | 2019  | 2021           |

| Modulation scheme              | DBPSK     | OOK-PM | BPSK     | OOK/ASK | BPSK                | FSK   | OOK/BFSK/DBPSK |

| Tech. (nm)                     | 130 BCD   | 350    | 130 CMOS | 180     | 180                 | 130   | 180            |

| Active area (mm <sup>2</sup> ) | 0.03      | 0.36 * | 0.084    | N.A     | 0.137               | 0.222 | N.A            |

| Power (mW)                     | 0.75      | < 0.4  | 1.4      | 0.184   | 0.217               | 0.184 | 0.054/0.01     |

| Carrier freq. (MHz)            | 0.128     | 1      | 21       | 1       | 13.56               | 405   | 433            |

| Data rate (kbps)               | 32.0      | 25     | 1312.5   | 50.0    | 211                 | 2500  | 200            |

| DRCF (%)                       | 25        | 2.5    | 6.25     | 5       | 1.55                | 0.617 | 0.046          |

| $FoM_1$                        | 33.33     | 6.25   | 4.46     | 27.17   | 7.17                | 3.35  | 0.85/4.6       |

| FoM <sub>2</sub>               | 1111      | 17.36  | 53.09    | N.A     | 52.53               | 15.09 | N.A            |

Table 1. Performance of the proposed DBPSK demodulator and comparison with other studies.

$FoM_1 = \frac{DRCF}{Power(mW)}$ ;  $FoM_2 = \frac{FoM_1}{A(mm^2)}$ ; \* Estimated area occupation from die photo.

# 7. Conclusions

In this article, the fully integrated AFE along with a DPBSK demodulator are implemented in a 130 nm BCD process with a die size of 0.7 mm<sup>2</sup>. The power consumption of the proposed DBPSK demodulator is 0.75 mW to detect the data and recover the clock. Experimental results show the system offers a maximum data rate of 32 kbps where the carrier frequency is 128 kHz.

Author Contributions: Conceptualization, S.A.H.A.; data curation, S.A.H.A.; formal analysis, S.A.H.A. and B.S.R.; investigation, S.A.H.A. and B.S.R.; methodology, S.A.H.A.; resources, S.A.H.A. and B.S.R.; software, S.A.H.A.; supervision, K.-Y.L.; validation, K.-Y.L., Y.P. and H.H.; visualization, S.A.H.A.; writing original draft, S.A.H.A., B.S.R. and K.-Y.L.; writing—review and editing, B.S.R., A.H., Y.J., K.C.H., Y.Y. and K.-Y.L. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

Acknowledgments: This paper was supported by Korea Institute for Advancement of Technology (KIAT) grant funded by the Korea Government (MOTIE) (P0012451, The Competency Development Program for Industry Specialist).

Conflicts of Interest: The authors declare no conflict of interest.

# References

- 1. Razavi, B. RF Microelectronics (Prentice-Hall Communications Engineering and Emerging Technologies Series). 2011. Available online: https://www.informit.com/imprint/series\_detail.aspx?ser=4268879 (accessed on 5 May 2022).

- Asl, S.A.H.; Rad, R.E.; Rikan, B.S.; Pu, Y.; Hwang, K.C.; Yang, Y.; Lee, K.-Y. A 1.8–2.7 GHz Triple-Band Low Noise Amplifier with 31.5 dB Dynamic Range of Power Gain and Adaptive Power Consumption for LTE Application. *Sensors* 2022, 22, 4039. [CrossRef] [PubMed]

- Ryu, S.; Kim, K.; Kim, J.; Cho, I.; Kim, H.; Ahn, J.; Choi, J.; Ahn, S. Design and Analysis of a Magnetic Field Communication System Using a Giant Magneto-Impedance Sensor. *IEEE Access* 2022, 10, 56961–56973. [CrossRef]

- 4. Feng, T.; Lajnef, N.; Chakrabartty, S. Design of a CMOS System-on-Chip for Passive, Near-Field Ultrasonic Energy Harvesting and Back-Telemetry. *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.* **2016**, *24*, 544–554. [CrossRef]

- Sonmezoglu, S.; Fineman, J.R.; Maltepe, E.; Maharbiz, M.M. Monitoring deep-tissue oxygenation with a millimeter-scale ultrasonic implant. *Nat. Biotechnol.* 2021, 39, 855–864. [CrossRef] [PubMed]

- 6. Wilkerson, B.P.; Kang, J. A low power BPSK demodulator for wireless implantable biomedical devices. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Beijing, China, 19–23 May 2013; pp. 626–629. [CrossRef]

- Lo, C.-Y.; Hong, H.-C. A 0.9 pJ/b, Reference Clock Free, Delay-Based, All-Digital Coherent BPSK Demodulator. *IEEE Solid State Circuits Lett.* 2020, *3*, 498–501. [CrossRef]

- Chen, K.; Yang, Z.; Hoang, L.; Weiland, J.; Humayun, M.; Liu, W. An Integrated 256-Channel Epiretinal Prosthesis. *IEEE J. Solid State Circuits* 2010, 45, 1946–1956. [CrossRef]

- Rad, R.E.; Hejazi, A.; Asl, S.-A.H.; Shehzad, K.; Verma, D.; Kim, S.; Rikan, B.S.; Pu, Y.; Kim, J.T.; Hwang, K.C.; et al. A 77-dB Dynamic-Range Analog Front-End for Fine-Dust Detection Systems with Dual-Mode Ultra-Low Noise TIA. *Sensors* 2021, 21, 6360. [CrossRef] [PubMed]

- Qian, X.; Teo, T.H. A low-power comparator with programmable hysteresis level for blood pressure peak detection. In Proceedings of the TENCON 2009—2009 IEEE Region 10 Conference, Singapore, 23–26 January 2009; pp. 1–4. [CrossRef]

- Ghazi, M.; Maghami, M.H.; Amiri, P.; Hamedi-Hagh, S. An Ultra-Low-Power Area-Efficient Non-Coherent Binary Phase-Shift Keying Demodulator for Implantable Biomedical Microsystems. *Electronics* 2020, 9, 1123. [CrossRef]

- Ballo, A.; Grasso, A.D.; Privitera, M. A 28 nm Bulk CMOS Fully Digital BPSK Demodulator for US-Powered IMDs Downlink Communications. *Electronics* 2022, 11, 698. [CrossRef]

- Luo, Y.S.; Wang, J.R.; Huang, W.J.; Tsai, J.Y.; Liao, Y.F.; Tseng, W.T.; Yen, C.T.; Li, P.C.; Liu, S.I. Ultrasonic Power/Data Telemetry and Neural Stimulator With OOK-PM Signaling. *IEEE Trans. Circuits Syst. II Express Briefs* 2013, 60, 827–831. [CrossRef]

- 14. Cho, H.; Lee, H.; Bae, J.; Yoo, H.-J. A 5.2 mW IEEE 802.15.6 HBC Standard Compatible Transceiver with Power Efficient Delay-Locked-Loop Based BPSK Demodulator. *IEEE J. Solid State Circuits* 2015, *50*, 2549–2559. [CrossRef]

- 15. Mazzilli, F.; Dehollain, C. 184 μW ultrasonic on–off keying/amplitude-shift keying demodulator for downlink communication in deep implanted medical devices. *IET Electron. Lett.* **2016**, *52*, 502–504. [CrossRef]

- Cheng, C.-H.; Tsai, P.-Y.; Yang, T.-Y.; Cheng, W.-H.; Yen, T.-Y.; Luo, Z.; Qian, X.-H.; Chen, Z.-X.; Lin, T.-H.; Chen, W.-H.; et al. A Fully Integrated 16-Channel Closed-Loop Neural-Prosthetic CMOS SoC With Wireless Power and Bidirectional Data Telemetry for Real-Time Efficient Human Epileptic Seizure Control. *IEEE J. Solid State Circuits* 2018, 53, 3314–3326. [CrossRef]

- 17. Shang, Z.; Zhao, Y.; Lian, Y. A Low Power Frequency Tunable FSK Receiver Based on the N-Path Filter. *IEEE Trans. Circuits Syst. II Express Briefs* **2019**, *66*, 1708–1712. [CrossRef]

- Cheng, K.-W.; Chen, S.-E. An Ultralow-Power OOK/BFSK/DBPSK Wake-Up Receiver Based on Injection-Locked Oscillator. *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.* 2021, 29, 1379–1391. [CrossRef]