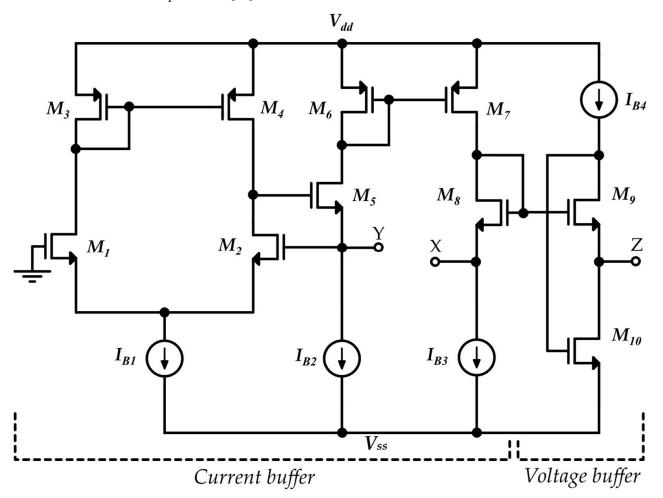

# **A Review on VCII Applications in Signal Conditioning for Sensors and Bioelectrical Signals: New Opportunities**

Leila Safari, Gianluca Barile 🔍, Vincenzo Stornelli \* 🗅 and Giuseppe Ferri 🔎

Department of Industrial and Information Engineering and Economics, University of L'Aquila, 67100 L'Aquila, Italy; leilasafari@yahoo.com (L.S.); gianluca.barile@univaq.it (G.B.); giuseppe.ferri@univaq.it (G.F.)

\* Correspondence: vincenzo.stornelli@univaq.it

Abstract: This study reviews second-generation voltage conveyor (VCII)-based read-out circuits for sensors and bioelectrical signal conditioning from existing literature. VCII is the dual circuit of a second-generation current conveyor (CCII), which provides the possibility of processing signals in the current domain while providing output signals in the voltage form. The scope of this paper is to discuss the benefits and opportunities of new VCII-based read-out circuits over traditional ones and bioelectrical signals. The achieved main benefits compared to conventional circuits are the simpler read-out circuits, producing an output signal in a voltage form that can be directly used, improved accuracy, possibility of gain adjustment using a single grounded resistor, and the possibility of connecting several SiPM sensors to the readout circuit. The circuits studied in this paper include VCII-based read-out circuits suitable for all types of sensors configured in the current-mode Wheatstone bridge (CMWB) topology, the VCII-based read-out circuits solutions reported for silicon photomultiplier, spiral-shaped ultrasonic PVDF and differential capacitive sensors, and, finally, a simple readout circuitry for sensing bioelectrical signals. There are still not many VCII-based readout circuits, and we hope that the outcome of this study will enhance this area of research and inspire new ideas.

# 1. Introduction

Nowadays, the signal conditioning of sensors and bioelectrical signals play a vital role in many areas, such as in infrastructure and environmental monitoring, healthcare, and many other applications [1-7]. Various types of sensors are widely used in monitoring and sensing different parameters, such as pressure, temperature, force, position, etc., thanks to the recent advances in CMOS technology, which permits integrating different types of sensors and the interface circuits into a single chip. This is definitely considered a great step toward the development of smart sensors and smart healthcare. The operations performed by the signal conditioning circuit in smart sensors and healthcare are the sensing and amplification of the sensor output/bioelectrical signal, analog-to-digital and digital-toanalog conversion, signal sampling and quantization, data processing, calibration, selftesting, and diagnosing. The first part of this system is the analog read-out circuitry, which produces an output signal dependent on the bioelectrical signals or parameters measured by the sensor. As the output of read-out circuitry is fed to the rest of the circuit for further processing, it can be viewed as the most important part due to its high impact on the overall accuracy of interface circuitry. Some of the sensor applications are categorized in the field of hand-held or portable applications, which demand low-voltage low-power operation.

Capacitive sensors, temperature sensors, pressure sensors, and silicon photo multipliers (SiPMs) are examples of the most widely used sensor types. Various approaches

Citation: Safari, L.; Barile, G.; Stornelli, V.; Ferri, G. A Review on VCII Applications in Signal Conditioning for Sensors and Bioelectrical Signals: New Opportunities. *Sensors* **2022**, *22*, 3578. https://doi.org/10.3390/s22093578

Academic Editor: Youfan Hu

Received: 31 March 2022 Accepted: 6 May 2022 Published: 8 May 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). have been reported in the literature for the read-out circuitry of these sensors [8–23]. Traditional reported voltage-mode methods in designing read-out circuits suffer from several drawbacks. Such as high power consumption, complexity, and low-frequency operation. For example, in [17,18], read-out circuitries for differential capacitive sensors configured in the voltage-mode Wheatstone bridge (VMWB) were reported containing several different components. The complexity, large chip area, and high power consumption were their main drawbacks. Although the solution based on the current-mode approach offers circuits with less power consumption, simplicity, and higher-frequency performance, it mainly suffers from a common weakness. As most current-mode active building blocks lack a low impedance voltage output port, the existing current-mode read-out circuits do not provide an output signal in the voltage form, or they require an extra voltage buffer at output. For example, we can mention second-generation current conveyor (CCII)-based read-out circuitry as some sensor interfaces reported in [19,20].

Recently, using the duality concept, a new active building block called second-generation voltage conveyor (VCII) as the dual circuit of CCII received a boost of attention [9,11–13,24–45]. Similar to CCII, the operation of VCII is based on current-mode signal processing; thus, it offers all of the interesting advantages given by the CCII. Unlike CCII, VCII has a low impedance voltage output port, which offers more flexibility in applications requiring an output signal in the voltage form. Studies have been reported on VCII design and application in different areas, such as impedance simulators [30-32,38], filters [29,33,35,43], rectifiers [40,45], oscillators [42], etc. The reported VCII-based circuits have revealed fruitful outcomes in facing the shortcomings of traditional circuits, which have been a great motivation in utilizing VCII in the aforementioned areas. There has also been a handful of research targeting VCII-based read-out circuitries for various types of sensors and bioelectrical signals. Due to the importance of sensor and bioelectrical signal conditioning in life and healthcare today, the aim of this paper is to present a review of the research conducted on the design of VCII-based read-out circuits. We hope that this study will speed up this research area by highlighting the benefits and advantages achieved using VCII in signal-conditioning circuits. The reported VCII-based circuits for the signal conditioning of various sensors configured in current-mode Wheatstone bridge (CMWB), silicon photo multipliers (SiPMs), spiral-shaped PVDF ultrasonic sensors, differential capacitive sensors, and bioelectrical signal sensing are discussed.

Since the VCII is a novel device, the presented work, for the first time, has the research meaning of giving a review of all of the reported read-out circuit solutions using this block. The result of this study provides an easy comparison between the old solutions and the new opportunities provided by VCII. It highlights the main achieved benefits and novelties. It helps new solutions in mitigating shortcomings of conventional solutions in designing read-out circuits. The organization of this paper is as follows. In Section 2, an introduction of VCII features and implementation is presented. In Section 3, reported VCII-based signal conditioning circuits for different types of sensors and bioelectrical signals are presented. In Section 4, comparisons and future prospects are presented. Finally, Section 5 concludes this paper.

## 2. Overview of VCII: Features and Implementation

Applying the duality concept to well-known CCII, a new active building block was found, called the second-generation voltage conveyor (VCII) [27], which was also recently compared to operational amplifiers [28].

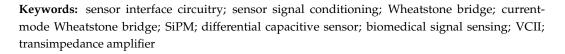

Figure 1 shows the symbol and internal structure of the VCII. According to this duality, in the VCII, there is a current buffer between the Y and X terminals, while in CCII, there is a voltage buffer between the Y and X terminals. Therefore, in the VCII, Y is a low-impedance current input port and X is a high-impedance current output port, while in CCII, Y is high-impedance voltage input port and X is low-impedance voltage output port. There is a voltage buffer between the X and Z ports of VCII, while there is a current buffer between the

X and Z ports in CCII. Figure 2 shows the symbolic representation of VCII. The operation matrix of VCII is:

$$\begin{bmatrix} I_X \\ V_Z \\ V_Y \end{bmatrix} = \begin{bmatrix} \pm \beta & 0 & 0 \\ 0 & \alpha & 0 \\ 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} I_Y \\ V_X \\ I_Z \end{bmatrix}$$

(1)

where  $\beta$  and  $\alpha$  are the current gain between the Y and X ports and voltage gain between the X and Z ports, respectively, with ideal values of unity.  $V_x$  and  $V_z$  are the voltages at the X and Z ports, respectively.  $I_Y$  and  $I_X$  are the input current to the Y port and output current at the X port, respectively. For  $+\beta$ , we have VCII<sup>+</sup>, and for  $-\beta$ , we have VCII<sup>-</sup>. In addition to three-port VCII, there is another version with a five-port VCII, shown by VCII<sup>±</sup>, which has two X ports, two Z ports, and one Y port [38]. The extra ports provide more flexibility and freedom in some applications.

Figure 1. (a) Symbolic representation and (b) internal structure [27].

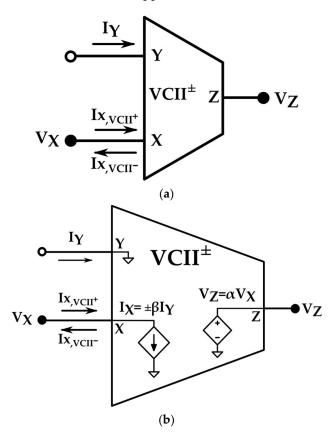

Figure 2. Noise model of VCII [36].

In [36], a noise model of VCII was derived, as reported in Figure 2. As shown, there are equivalent current noise and equivalent voltage noise at each port. Based on the application and port connection, some of these noise sources play important roles, while others may have a negligible effect on the circuit performance. For example, in applications where the Y port is connected to a high-impedance node, such as SiPM read-out circuits, the effect of voltage noise at the Y port ( $\overline{dv_{Yneq}^2}$ ) becomes insignificant, while the equivalent current noise at the Y port i.e.,  $\overline{di_{Yneq}^2}$  must be considered in the circuit performance because it completely concerns the Y port and operates as an input signal. Therefore, for each specific application, the designer can consider the critical noise source and minimize its value to achieve the best performance.

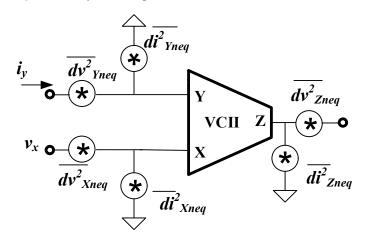

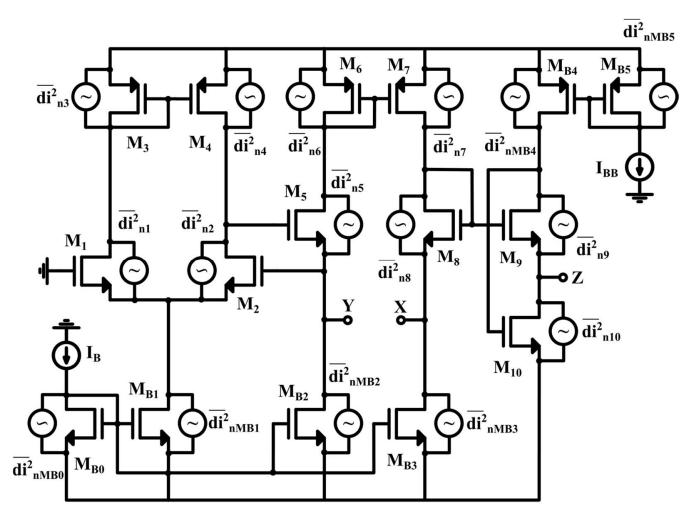

A basic CMOS realization of VCII<sup>+</sup> is shown in Figure 3 [36], at the transistor level and in a simplified form. Here, transistors  $M_1$ – $M_7$  form the current buffer between the Y and X terminals, and transistors  $M_9$ – $M_{10}$  form the voltage buffer between the X and Z ports. Figure 4 shows the complete VCII schematic, also showing the equivalent output current noise produced by each transistor. The equivalent noise at each port can be achieved by analyzing the effect of each transistor's noise. The designer can then choose the optimized size and bias current of each transistor in order to minimize its noise contribution, as explained in [36].

Figure 3. A possible simplified MOS implementation of VCII<sup>+</sup> [36].

Figure 4. Complete VCII schematic with noise sources [36].

Various VCII designs have been reported. For example, a translinear-based VCII realization was presented in [34], which provides temperature-insensitive operation. In [37], a low-voltage high-drive VCII was introduced, which offers high current drive capability at X port. In [40], a rail-to-rail VCII was designed, which has a full voltage swing at the X and Z ports.

#### 3. VCII in Sensor and Bioelectrical Signal Conditioning

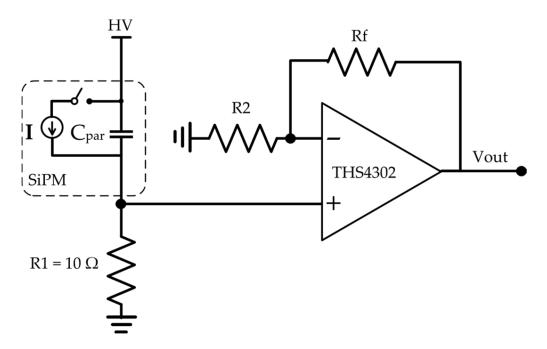

3.1. Application of VCII in Current-Mode Wheatstone Bridges

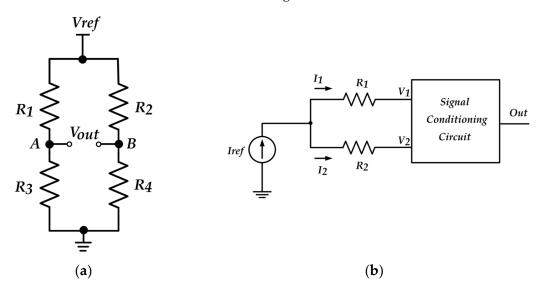

The conventional voltage-mode Wheatstone bridge (VMVB) shown in Figure 5a is a network of four resistors that has wide applications in temperature, pressure, and resistive sensor signal conditioning circuits. One or some of these resistances represent sensors by the value equal to  $R = R_0 \pm \Delta R$ . A reference voltage is applied to the resistor network and an output voltage is produced in response to any change in the value of the sensor resistors. The produced output signal is processed by a voltage-handling interface circuit. Applying the duality concept, a so-called current-mode Wheatstone bridge (CMWB) was introduced based on only two resistors (Figure 5b) [8]. Compared to VMWB, the CMWB has a smaller number of resistors. In addition, the exciting signal is the current; therefore, a current-mode signal-conditioning circuit is used to process the produced signals, which enjoys the intrinsic advantages of current-mode signal processing, such as high-frequency operation. Various current-mode signal-conditioning circuits have been reported using active building blocks. such as CCII, operational floating current conveyors (OFCCs), and CDTA [8,10]. However, the reported current-mode signal-conditioning circuits suffer from some major

disadvantages, such as the large number of active building blocks used in [8], which resulted in circuit complexity and high power consumption. The circuit reported in [8] consisted of three OFCCs and four resistors. Therefore, it requires high power consumption and a large chip area. The circuit reported in [10] required an extra voltage buffer at output for practical applications. In [8,10], in the case of one-sensor applications, the output signal is the non-linear function of  $\Delta R$ . Therefore, special linearization techniques are required to produce an output signal proportional to  $\Delta R$ . An offset canceling circuit is required to eliminate the large-value offset current, which is equal to  $I_{ref}/2$ . In [10], the output signal is in the current form, and there is no control on gain.

Figure 5. (a) Voltage-mode Wheatstone bridge and (b) current mode Wheatstone bridge [9].

In [9], a VCII-based interface circuit for CMWB was reported, proving the high potential of VCII in eliminating the above-mentioned drawbacks. VCII-based interface circuits for both two-sensor and one-sensor applications are shown in Figure 6. In Figure 6a,  $R_1$ and  $R_2$  represent the used sensors' equivalent circuit. Due to the very low value of parasitic resistance at the Y port of VCII, which is ideally zero, the Y ports of VCII<sub>1</sub> and VCII<sub>2</sub> were assumed at ground. Therefore,  $I_{ref}$  was divided between  $R_1$  and  $R_2$  (producing  $I_1$  and  $I_2$ , respectively) based on their value. The current  $I_2$ , which enters the Y port of VCII<sub>2</sub>, is transferred to its X port due to the current buffering action between the Y and X ports with the gain of  $\beta_2$  with a value close to unity, producing  $\beta_2 I_2$  at the X port of VCII<sub>2</sub>. A current subtraction between I<sub>1</sub> and  $\beta_2 I_2$  is performed at the Y port of VCII1. The resulting current enters the Y port of VCII1, which is then transferred to its X port by gain of  $\beta_1$  (the current gain between the Y and X ports of VCII1), where it is converted to the proportional voltage by  $R_3$ . Due to the voltage-buffering action between the X and Z ports, the produced voltage is transferred to the Z port of VCII1 with the gain of  $\alpha_1$  (the voltage gain between the X and Z ports of VCII<sub>1</sub>). To follow the given explanations, the related current and voltage signals are shown in Figure 6a. In the case of a single sensor, which is shown in Figure 6b,  $R_1$  is the used sensor and  $R_2$  is a resistor with a value equal to  $R_0$  of the used sensor. Here,  $I_{ref}$  enters the Y port of VCII1, which is transferred to its X port and converted to voltage by  $R_1$ . The produced voltage is transferred to VCII<sub>1</sub>'s Z port by the gain of  $\alpha_1$ , where it is converted to a current by  $R_2$ . The current subtraction performed at the Y port of VCII<sub>2</sub> removes the DC part of the current signal entering the Y port of VCII<sub>2</sub>. The gain-controlling resistor  $R_3$ produces an output signal proportional to  $\Delta R$ . The circuits are intrinsically linear for both two-sensor (Equation (2)) and one-sensor (Equation (3)) cases:

$$V_{out} \approx \frac{\pm \Delta R}{R_0} \alpha_1 R_3 I_{ref} \tag{2}$$

Figure 6. VCII-based interface circuit for CMWB [9] for (a) two-sensor and (b) one-sensor applications.

The first advantage of VCII-based signal-conditioning circuits is that the output signal is in the voltage form produced at the low impedance Z port of VCII. Therefore, for practical applications, no extra voltage buffer is required. Fortunately, the need for offset cancelation circuits is also alleviated here. A simple KCL analysis shows that the DC offset current is intrinsically eliminated at the Y port of VCII1 in Figure 6a. In Figure 6b, the offset current is simply eliminated by adding I<sub>ref</sub> to the Y port of VCII2, where, for *i* = 1,2,  $\alpha_i$  and  $\beta_i$  are the voltage gain and current gain of the ith VCII, respectively, with both values close to unity. The conditions  $\alpha_1 \approx 1$  and  $\beta_2 \alpha_2 \approx 1$  must be satisfied for Equation (2) and Equation (3), respectively. Fortunately, as the values of  $\alpha$  and  $\beta$  are very close to unity, these conditions are usually met. The gain of circuit can also be simply adjusted by the value of  $R_3$ . In [9], using an electronically variable resistor for  $R_3$ , the gain is electronically varied using a control voltage.

## 3.2. Application of VCII in Silicon Photo Multipliers

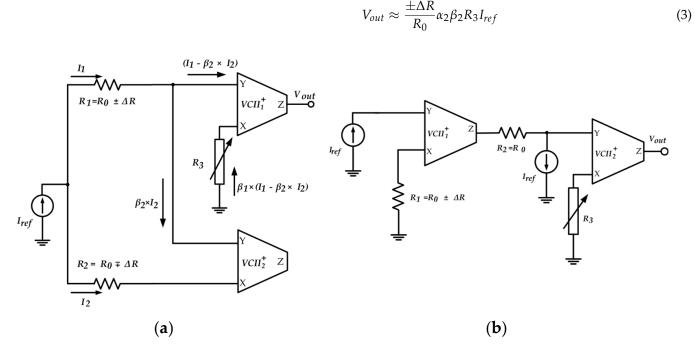

Recently, large-current-gain silicon photo multipliers (SiPM) have made them the best choice for photo sensors [11-15]. It may seem that measuring the incident photons using large-gain SiPMs is easy. However, the main challenge in designing an efficient read-out circuitry for SiPMs is dealing with their large output capacitance ( $C_{par}$ ). In particular, for an array of N SiPMs connected in parallel, the output capacitance becomes even larger  $(C_{ToT} = NC_{par})$ , with values up to thousands of pF. On the other hand, the SiPM read-out circuitry must fulfill other requirements, such as a fast response time, high linearity, low added noise, and sufficient gain. These features are mandatory for the proper acquisition of incoming signals. To mitigate the effect of large input capacitance, low input impedance is required for read-out circuitry. The conventional methods of designing SiPM read-out circuitry are common-gate (CG)-common-base (CB) amplifiers, operational amplifierbased voltage amplifiers (VAs), and operational amplifier-based transimpedance amplifiers (TIAs) [14]. All of these solutions provide low input impedance to reduce the effect of the large parasitic capacitance of SiPMs. Unfortunately, the CG and CB amplifiers suffer from inappropriate output impedance. In fact, they require an extra voltage buffer at output. In addition, the gain-dependent bandwidth of OA-based VAs and TIMAs makes these structures unattractive. Let us consider OA-based VAs in more detail, which is shown in Figure 7 [14].

Figure 7. Conventional OA-based VA as readout circuitry for SiPM [14].

Here, the current signal from SiPM is converted to voltage by  $R_1$  at first. The produced voltage is amplified by the OA configured in a negative feedback loop. The main weakness of this circuit is its constant-gain bandwidth product. Therefore, by increasing the gain value, the bandwidth reduces. On the other hand, the value of  $R_1$  must be small enough to reduce the effect of  $C_{par}$ . This indicates that the produced input voltage is very small and very prone to the input noise of OA.

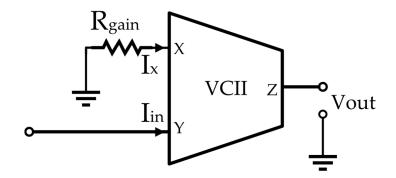

A helpful solution in providing high-frequency performance is using the current-mode signal-processing technique. For minimum possible additive noise, the straightforward solution is adopting a very simple structure with a smaller number of components, having low input impedance at the Y port and a very simple internal structure that includes only a simple current buffer, and the voltage buffer makes VCII a very suitable candidate for SiPM read-out applications. In addition, as signal processing in VCII is performed in the current domain, a fast response time and high frequency performance are ensured. Interestingly, as shown in Figure 8 [11–13], by connecting the X port to a resistor  $R_g$ , VCII operates as a transimpedance amplifier between the Y and Z nodes with gain equal to:

$$\frac{V_{out}}{I_{in}} = \alpha \beta R_{gain} \tag{4}$$

where  $\alpha$  and  $\beta$  are the voltage gain and current gain of VCII. For Equation (4), we must have  $R_g \ll r_X$ .  $I_{in}$  is the input signal to the circuit and  $V_{out}$  is the produced output signal. The value of  $r_X$  is usually larger than 100 k $\Omega$ , as reported in [29–32,34,35,42–44]. Therefore, by adopting the value of  $R_{gain}$  at 10 k $\Omega$ , large values of gain up to 80 dB are achievable. Importantly, the achieved gain is independent of bandwidth because the VCII is not configured in a negative feedback loop. The incoming input current signal is detected and converted to a proportional voltage signal, which is available at the low-impedance Z port of VCII. Therefore, the output signal can be directly used without any need for extra voltage buffers.

Figure 8. VCII as a transimpedance amplifier [11–13].

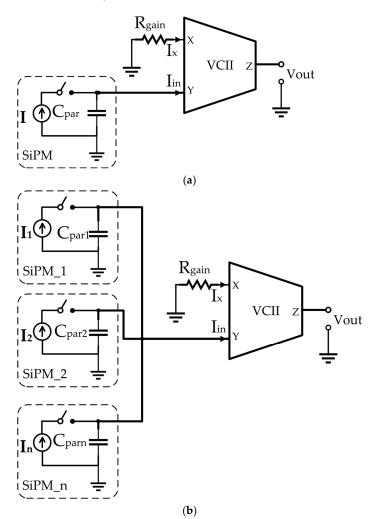

Figure 9a,b show the SiPM read-out circuitry for a single SiPM and an array of *n* SiPMs. In Figure 9a,  $C_{par}$  is the parasitic capacitance and  $I_1$  is the output current of the SiPM sensor, respectively. In Figure 9b, for i = 1 - n,  $C_{par,i}$  and  $I_i$  are the practice capacitance and output current of the nth SiPM, respectively. In Figure 9b, by connecting the *i*th switch, the related SiPM is connected to the VCII-based transimpedance amplifier Y node. Then, the sensors' output current is converted to the proportional voltage by VCII. A comprehensive study on the VCII internal noise reduction and optimization techniques was reported in [36], which must be considered in the design of VCII's internal structure intended to be used in SiPM interface circuitry.

Figure 9. VCII-based readout circuitry for (a) a single SiPM and (b) an array of *n* SiPMs [13].

## 3.3. Application of VCII in an Ultrasonic PVDF Interface Circuit

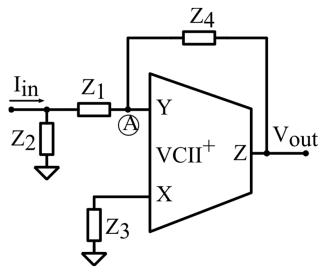

Piezoelectric sensors are widely used for the generation and reception of ultrasounds in different fields, such as echolocation and communication systems, medical treatment, etc. As an example, in [25], the VCII-based trans-impedance configuration reported in Figure 6 was used as the first solution for the interface circuitry of ultrasonic PVDF sensors. The low impedance at the Y port of VCII allowed directly connecting the spiral-shaped PVDF sensor to a preamplifier. Traditionally, OAs are used as preamplifiers in ultrasonic PVDF sensors, which are constrained by the gain-dependent bandwidth, high complexity, high power consumption, etc. The second solution for ultrasonic PVDF sensors proposed in [25] shown in Figure 8 is a configurable VCII-based low-pass or band-pass filter which performs a filtering action on the incoming signal. Measurement results obtained using a discrete prototype are also reported in [25].

The transfer function between  $I_{in}$  and  $V_{out}$  is:

$$\frac{V_{out}}{I_{in}} = \frac{Z_2 Z_3 Z_4}{(Z_1 + Z_2)(Z_3 + Z_4)}$$

(5)

For  $Z_1 = 1/sC_1$ ,  $Z_2 = R_2$ ,  $Z_3 = 1/sC_3$ , and  $Z_4 = R_4$ , Equation (5) transforms into a second order bandpass transfer function as:

$$\frac{V_{out}}{I_{in}} = \frac{sC_1R_2R_4}{1 + s(C_1R_2 + C_3R_4) + s^2C_1C_3R_2R_4}$$

(6)

For  $Z_1 = R_1$ ,  $Z_2 = 1/sC_2$ ,  $Z_3 = R_3$ , and  $Z_4 = 1/sC_4$ , Equation (5) is a second-order low-pass transfer function:

$$\frac{V_{out}}{I_{in}} = \frac{sC_1R_2R_4}{1 + s(C_2R_1 + C_4R_3) + s^2C_2C_4R_1R_3}$$

(7)

Therefore, using the circuit in Figure 10, the noise associated with the input signal is eliminated by choosing the appropriate filter function and the purified input signal is transferred to an appropriate voltage single output, which is available at the Z port of the VCII.

Figure 10. VCII-based reconfigurable low-pass band-pass filter for ultrasonic PVDF sensors [25].

## 3.4. Application of VCII in Differential Capacitive Sensors

Capacitive sensors are an essential part of many sensing systems, such as accelerometers, pressure sensors, position sensors, etc. [16–23]. Differential capacitive sensors intrinsically mitigate the effect of unwanted common-mode signals and parasitic effects; therefore, they make it possible to use low-cost and simple read-out circuitry. The difcircuitry. The conventional read-out circuits for differential capacitive sensors suffer from extra complexity, which fails to fulfill the easy integration, low power consumption, and low chip area requirements. For example, in [16–24], bridge-based read-out circuitry was based on the modulation–demodulation technique, which consists of various blocks as the multiplier, differential amplifier, PI controller, and filter. To be more specific, the used differential amplifier itself consists of three OTAs and six high large-value resistors, in addition to a separate reference voltage. For proper operation, strict matching between six resistors is mandatory. The large requirement for chip area and high power consumption are the main problems of this solution. In the conventional solutions reported in [16–23], a large number of switches are employed requiring additional controlling clock signals. This solution suffers from limited achievable accuracy due to the problems caused by the clock feedthrough and charge injection errors of switches.

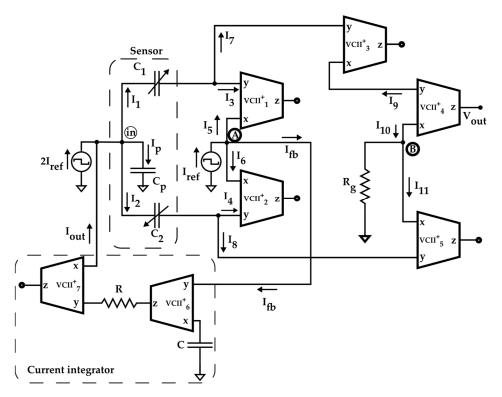

In [24], for the first time, read-out circuitry for differential capacitive sensors using VCII is reported. The circuit is shown in Figure 11. It operates based on capacitance to voltage conversion.  $C_p$  is the parasitic capacitance associated with the sensor. The sensor's capacitors  $C_1$  and  $C_2$  are excited by a square-wave current signal; therefore, they are automatically charged and discharged without any need for switches. The circuit is designed in a way that the current wasted by  $C_p$  is measured and compensated. The used VCII<sub>1</sub>-VCII<sub>2</sub> forms a current summation/subtraction. Therefore, the sum of the currents at  $C_1$  and  $C_2$  is produced at node A, where is it subtracted from  $I_{ref}$ . By this, the amount of current stolen by  $C_p$  is produced as  $I_{fb}$ , which is fed back to the input node by the VCII-based current integrator composed of VCII<sub>6</sub>-VCII<sub>7</sub>. After compensating for the effect of  $C_p$ , the sensor's current is subtracted at node B by VCII<sub>4</sub>-VCII<sub>5</sub>. VCII<sub>3</sub> is used to invert the  $C_1$  current needed for current subtraction. The resulting signal is converted to a proportional voltage by  $R_g$ , which is transferred to the output node by VCII<sub>4</sub>.

Figure 11. VCII-based readout circuit for differential capacitive sensors [24].

The operation is completed by only seven VCIIs, two low-value resistors, and one capacitor. The main feature of this solution is that signal processing is completely performed in the current domain, granting the read-out circuitry a fast response time. In addition,

using only one type of active building block, the circuit enjoys extreme simplicity and very easy integration requiring a low chip area because each VCII is composed of only 10 MOS transistors, and the used resistors are of low values. The other distinguishing feature is that the effect of parasitic capacitance is effectively reduced using a simple VCII-based integrator in the negative feedback loop. To provide high accuracy and avoid the problems caused by switches, the sensors are excited by a square-wave signal.

The simulation and experimental results reported in [24] prove the high potential of VCII for use in low-cost, highly accurate, and fully integrated read-out circuitry for differential capacitive sensors. In the traditional method reported in [23], parasitic capacitance is compensated using three instrumentation amplifiers, an integrator, low-pass filter, and a voltage-controlled negative impedance convertor. Comparing the solution in [23] and the VCII-based method of [24], we find that the VCII offers a much simpler solution compared to previous methods using conventional building blocks.

#### 3.5. Application of VCII in Biomedical Sensors

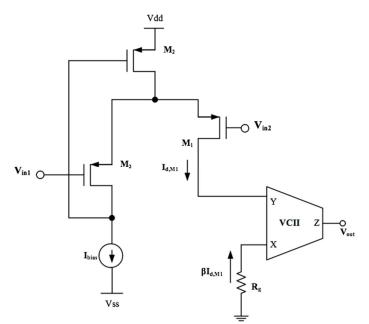

A general electrical biosignal is characterized by a low amplitude value of up to 1 mV and frequency of 0.5 Hz–10 kHz [26,46]. The challenging part is that this weak signal is accompanied by a large noise signal. For the read-out circuitry, it is required to detect and distinguish the low-value signals from unwanted noise. For portable applications, low power consumption and a small size are also fundamental features. In [26], a read-out circuit was reported using a fully differential transconductance amplifier, two pseudo resistors, two switches, four capacitors, and a standard instrumentation amplifier (IA), including a differential amplifier and three resistors. Evidently, the matching between resistors in IA highly affected the overall accuracy of the read-out circuit. The difficulty in integration is the direct result of the large number of used components. Fortunately, in this area, VCII provides a very simple solution. The results of the study reported in [26] reveal a very simple and effective VCII-based read-out circuit for biosignals. The circuit, shown in Figure 12, employs a differential floating voltage flower (FVF) (formed by  $M_1$ – $M_3$ ), a VCII, and a single grounded resistor  $R_g$ . Two small-size capacitors are also used at the inputs to block the DC signals. Analysis of this circuit shows that the drain current of  $M_1$  is expressed as:

$$I_{d,M1} = \frac{1}{2} \mu_p C_{ox,p} \left(\frac{W}{L}\right)_{M1,M2} (V_{in1} - V_{in2})^2$$

(8)

Figure 12. VCII-based readout circuit for bioelectrical sensing [26].

Due to the existence of a current buffer between the Y and X terminals of VCII,  $I_{d,M1}$  is transferred to the X terminal, which is terminated to resistor  $R_g$ . A voltage proportional to  $I_{d,M1}$  is produced at the X terminal, which is copied to the Z terminal by means of the internal voltage buffer between the X and Z terminals. The produced output voltage is:

$$V_{z} = V_{out} = -\alpha \beta R_{g} I_{d,M1} = -\frac{1}{2} \alpha \beta R_{g} \mu_{p} C_{ox,p} \left(\frac{W}{L}\right)_{M1} (V_{in1} - V_{in2})^{2}$$

(9)

The resistance  $R_g$  acts as a gain-controlling resistor. In [24], using an electronically tunable resistor for  $R_g$ , the possibility of electronically tunable gain was also provided. A total number of 27 MOS transistors was used, indicating a very low required chip area with overall power consumption of only 20  $\mu$ W.

#### 4. Comparison and Future Prospects

In this section, some comparison tables between VCII-based read-out circuits and conventional ones are reported. Starting from Table 1, due to the processing signals in the current domain, the circuit described in [24] achieves comparable or better performances with respect to the other voltage-mode counterparts with a much simpler topology and the need for only one type of active building block. Moreover, if compared to [47], which also processes signals in the current domain, the presence of VCIIs enables designers to disregard switching structures, therefore neglecting the need for clock signals. Table 2 compares VCII-based SiPM interfaces [13] to other available solutions. It is evident that the VCII-based solution allows achieving very high transimpedance gain with the lowest power consumption and an acceptable bandwidth due to the peculiar feature of the VCII that the bandwidth remains constant, regardless of the gain of the amplifier. In addition, the low-impedance current input port allows VCII-based circuits to perform the current summation function very easily. This property is very useful in SiPM read-out circuits to add the required number of sensors to VCII Y nodes while reducing the effect of the parasitic capacitance of the SiPM sensors. In the case of read-out circuitry for CMWBs, the comparison is shown in Table 3. The current summation property of the VCII allows reducing the DC component of the output signal and provides intrinsic linearity for the single-sensor case. Table 4 summarizes the benefits of using VCII read-out stages for ultrasonic sensor applications: as shown, it is possible to achieve a very high gain together with a very large bandwidth [25], enabling the designer to take advantage of the novel and wideband shapes of the ultrasonic transducer. Lastly, Table 5 reports the application of the VCII to implement a biosignal interface circuit [26], comparing it with other techniques available in the literature. It is possible to achieve good power consumption while being able to continuously tune the gain of the amplifier stage. Moreover, the input impedance of the interface can be easily designed to be higher than the  $G\Omega$  in the required frequency band.

**Table 1.** Comparison between a VCII-based read-out circuit for differential capacitive sensors and conventional ones.

| Ref.            | [18]         | [21]       | [22]        | [24] *       | [47]        | [48]       | [49]       |

|-----------------|--------------|------------|-------------|--------------|-------------|------------|------------|

| Approach        | C-V          | C-V        | C-Digital   | Mixed        | C-I         | C-V        | C-V        |

| Variation range | $\pm 100\%$  | $\pm 50\%$ | $\pm 50\%$  | $\pm 100\%$  | $\pm 100\%$ | $\pm 60\%$ | -30%-100%  |

| C <sub>bl</sub> | 140 pF–14 nF | 500 pF     | 400 pF      | 10–200 pF    | 1 pF        | 20 pF      | 400 pF     |

| Linearity error | 0.5-0.8%     | < 0.03%    | <0.2%       | <1.9%/<0.9%  | $\pm 1.5\%$ | <0.1%      | < 0.45%    |

| Sensitivity     | 71 mV/pF     | 5 mV/pF    | 4 counts/pF | 412/21 mV/pF | 50 nA/fF    | 833 mV/pF  | Non linear |

| Typology        | Discrete     | Discrete   | Discrete    | Discrete     | Integrated  | Discrete   | Discrete   |

\* VCII-based circuit.

| Ref.   | Tech.       | Supply | Power   | T-I Gain | BW      | Noise                          |

|--------|-------------|--------|---------|----------|---------|--------------------------------|

| [13] * | CMOS 130 nm | 1.2 V  | 0.34 μW | 100 dB   | 10 MHz  | 27 mV <sub>rms</sub> (output)  |

| [50]   | CMOS 350 nm | 3.3 V  | 0.68 μW | 100 dB   | 50 MHz  | 1300 e-(ENĈ)                   |

| [51]   | CMOS 350 nm | 3.3 V  | 0.68 µW | 500      | 150 MHz | 2 μV <sub>rms</sub> (input)    |

| [52]   | CMOS 350 nm | 3.3 V  | 0.68 µW | /        | /       | 6.9 mV <sub>rms</sub> (output) |

| [53]   | SiGe 130 nm | -3.2 V | 82 µW   | 56 dB    | 45 GHz  | 30.6 pA/√Hz                    |

Table 2. Comparison between a VCII-based SiPM read-out circuit and conventional ones.

\* VCII-based circuit.

Table 3. Comparison between a VCII-based CMWB read-out circuit and conventional ones.

| Ref.  | Active Building Block | #of Active Building Block | #of Resistors | Intrinsic Linearity for<br>One Sensor Case | Output Signal |

|-------|-----------------------|---------------------------|---------------|--------------------------------------------|---------------|

| [8]   | CDTA                  | 1                         | 0             | No                                         | Current       |

| [9] * | VCII                  | 2                         | 1             | Yes                                        | Voltage       |

| [10]  | OFCC                  | 3                         | 5             | No                                         | Current       |

\* VCII-based circuit.

Table 4. Comparison between a VCII-based PVDF sensor read-out circuit and conventional ones.

| Sensor             | Active Device | Number of Processing Stages | Filtering Stage | Gain   | BW (KHz) | Power Consumption (mA) |

|--------------------|---------------|-----------------------------|-----------------|--------|----------|------------------------|

| Cylindrical 40 KHz | MOS stage     | 3                           | Bandpass        | 31 dB  | 100      | 30                     |

| Cylindrical 80 KHz | Op-Amp stage  | 3                           | Bandpass        | 61 dB  | 67       | 12 (estimated)         |

| [25] *             | VCII          | 1                           | None            | 86 dBΩ | >103     | 6                      |

|                    |               |                             |                 |        |          |                        |

\* VCII-based circuit.

Table 5. Comparison between a VCII-based read-out circuit for biosignal conditioning and conventional ones.

| Parameter                           | 2020 [26] *                                              | 2016 [54]                    | 2018 [55]                                 | 2019 [56]                                     | 2019 [57]                                          | 2018 [58]                                  |

|-------------------------------------|----------------------------------------------------------|------------------------------|-------------------------------------------|-----------------------------------------------|----------------------------------------------------|--------------------------------------------|

| CMOS Technology<br>Supply voltage   | LFoundry 150 nm<br>±0.6 V                                | 180 nm<br>1.2 V              | 180 nm<br>1 V                             | 180 nm<br>1.2 V                               | 180 nm<br>1.2 V                                    | 500 nm<br>3.3 V                            |

| Static power<br>consumption         | 20 µW                                                    | 0.9 µW                       | 0.25 μW                                   | 8.1 µW                                        | 2.48/5.46 μW<br>(AP/LFP)                           | 28.05 μW                                   |

| Amplifier gain (dB)                 | 0–33 (continuous<br>Tuning)                              | 30/50                        | 25.6                                      | 26/32/35.6 (Selectable)                       | 40/20 (AP/LFP)                                     | 49.5 (Untunable)                           |

| f <sub>HPF</sub> (Hz)               | $10^{-5}$                                                | 6.3                          | 4                                         | 0.025/0.25/0.5/1.5/<br>32/65/125/260          | -                                                  | 13                                         |

| f <sub>LPF</sub> (kHz)              | 174~3980                                                 | 0.175                        | 10                                        | 1/11.4/125                                    | 100/1000<br>(LFP/AP)                               | 9.8                                        |

| Z <sub>in</sub><br>Z <sub>out</sub> | 3.2 GΩ (@10 kHz)<br>1.2 kΩ (@10 kHz)<br>1.02% (-39.8 dB) | 20 MΩ<br>-                   | 200 MΩ @100 Hz<br>-                       | -                                             | -                                                  | -                                          |

| THD @frequency<br>reference         | @Vin = 2 mVpp,<br>Vctrl = 0 V,<br>10 kHz)                | 0.4%@1 mVpp<br>10 Hz         | -                                         | -                                             | -                                                  | 1% @ 0.7 mVpp,<br>10 kHz                   |

| Noise voltage<br>(input referred)   | 5.4 μV <sub>RMS</sub><br>(0.1 Hz~10 kHz)                 | 2.6 μVRMS<br>(0.5 Hz~400 Hz) | 3.32 μV <sub>RMS</sub><br>(250 Hz~10 kHz) | 6.75 μV <sub>RMS</sub> (0.5~11.4 k,<br>40 dB) | AP: 3.44<br>(0.25 k~10 k) LFP:<br>6.88 (0.025~600) | 1.88 μV <sub>RMS</sub><br>(0.03 Hz~11 kHz) |

| NEF                                 | 8.3                                                      | 6.6                          | 1.07                                      | 7.29                                          | NA                                                 | 2.3                                        |

\* VCII-based circuit.

Although VCII is not yet available as IC, in the measurement results reported so far, it has been implemented simply using two AD844s. However, if VCII is available as a custom integrated circuit chip, better accuracy results, and lower power consumption can be achieved.

## 5. Conclusions

In this paper, VCII-based solutions for read-out circuits of various types of sensors and bioelectrical signals are reviewed and compared with conventional solutions. With respect to other active building blocks, VCII is more flexible due to having a low-impedance current-input Y port, which makes current summation easy, a low-impedance voltageoutput Z port, and processing signals in the current domain. The results of this study show that the following advantages are achieved for different VCII-based read-out circuits: 1—an intrinsically linear very simple read-out circuit for sensors configured in the CMWB configuration with gain-controlling opportunity using a grounded resistor; 2—an improved accuracy with parasitic-insensitive operation for differential capacitive sensor read-out circuitry; 3—a very simple readout circuitry for SiPM sensors with reduced sensitivity to large parasitic capacitance associated with the sensor; 4—a very simple and low-power read-out circuitry for bioelectrical and PVDF sensors. More importantly, in all reported read-out circuits, the produced output signal is in the voltage form, and is available at the low-impedance Z port of the VCII, which can be also cascaded to other circuits directly.

**Author Contributions:** Conceptualization, L.S., G.F., V.S. and G.B.; methodology, L.S. and G.F.; validation, V.S. and G.F.; investigation, L.S. and G.B.; data curation, G.B. and L.S.; writing—original draft preparation, L.S.; writing—review and editing, G.F. and V.S.; visualization, G.B.; supervision, G.F. and V.S.; funding acquisition, V.S. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research has been partially funded by the European co-funded innovation project iRel4.0 ECSEL under grant agreement No. 876659.

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

Data Availability Statement: Not applicable.

**Conflicts of Interest:** The authors declare no conflict of interest.

## References

- Esteve Bosch, R.; Toledo Alarcón, J.F.; Herrero Bosch, V.; Simón Estévez, A.; Monrabal Capilla, F.; Álvarez Puerta, V.; Rodríguez Samaniego, J.; Querol Segura, M.; Ballester Merelo, F. The Event Detection System in the NEXT-White Detector. *Sensors* 2021, 21, 673. [CrossRef] [PubMed]

- Jeon, H.; Choi, I.; Kweon, S.-J.; Je, M. A Power-Efficient Radiation Sensor Interface with a Peak-Triggered Sampling Scheme for Mobile Dosimeters. Sensors 2020, 20, 3255. [CrossRef] [PubMed]

- Kumngern, M.; Aupithak, N.; Khateb, F.; Kulej, T. 0.5 V Fifth-Order Butterworth Low-Pass Filter Using Multiple-Input OTA for ECG Applications. Sensors 2020, 20, 7343. [CrossRef] [PubMed]

- Zamora, I.; Ledesma, E.; Uranga, A.; Barniol, N. Miniaturized 0.13-Mm CMOS Front-End Analog for AlN PMUT Arrays. Sensors 2020, 20, 1205. [CrossRef]

- 5. Stornelli, V.; Ferri, G. A Single Current Conveyor-Based Low Voltage Low Power Bootstrap Circuit for ElectroCardioGraphy and ElectroEncephaloGraphy Acquisition Systems. *Analog Integr. Circuits Signal Process.* **2014**, *79*, 171–175. [CrossRef]

- Kumar, S.S.; Ojha, A.K.; Pant, B.D. Experimental Evaluation of Sensitivity and Non-Linearity in Polysilicon Piezoresistive Pressure Sensors with Different Diaphragm Sizes. *Microsyst. Technol.* 2016, 22, 83–91. [CrossRef]

- Mantenuto, P.; Ferri, G.; De Marcellis, A. Uncalibrated Automatic Bridge-Based CMOS Integrated Interfaces for Wide-Range Resistive Sensors Portable Applications. *Microelectron. J.* 2014, 45, 589–596. [CrossRef]

- Ghallab, Y.H.; Badawy, W. A New Topology for a Current-Mode Wheatstone Bridge. *IEEE Trans. Circuits Syst. II Express Briefs* 2006, 53, 18–22. [CrossRef]

- Safari, L.; Barile, G.; Stornelli, V.; Ferri, G.; Leoni, A. New Current Mode Wheatstone Bridge Topologies with Intrinsic Linearity. In Proceedings of the 2018 14th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Prague, Czech Republic, 2–5 July 2018; pp. 9–12.

- Tanaphatsiri, C.; Jaikla, W.; Siripruchyanun, M. A Current-Mode Wheatstone Bridge Employing Only Single DO-CDTA. In Proceedings of the APCCAS 2008—2008 IEEE Asia Pacific Conference on Circuits and Systems, Macao, China, 30 November–3 December 2008; pp. 1494–1497.

- 11. Pantoli, L.; Barile, G.; Leoni, A.; Muttillo, M.; Stornelli, V. Electronic Interface for Lidar System and Smart Cities Applications. *J. Commun. Softw. Syst.* **2019**, *15*, 118–125. [CrossRef]

- Barile, G.; Leoni, A.; Pantoli, L.; Safari, L.; Stornelli, V. A New VCII Based Low-Power Low-Voltage Front-End for Silicon Photomultipliers. In Proceedings of the 2018 3rd International Conference on Smart and Sustainable Technologies (SpliTech), Split, Croatia, 26–29 June 2018; pp. 1–4.

- 13. Pantoli, L.; Barile, G.; Leoni, A.; Muttillo, M.; Stornelli, V. A Novel Electronic Interface for Micromachined Si-Based Photomultipliers. *Micromachines* 2018, 9, 507. [CrossRef]

- Wang, M.; Wang, Y.; Cao, Q.; Wang, L.; Kuang, J.; Xiao, Y. Comparison of Three Pre-Amplifier Circuits for Time Readout of SiPM in TOF-PET Detectors. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–5.

- Vinayaka, V.; Namboodiri, S.P.; Roy, A.; Baker, R.J. Segmented Digital SiPM. In Proceedings of the 2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS), Dallas, TX, USA, 4–7 August 2019; pp. 1118–1121.

- Barile, G.; Ferri, G.; Parente, F.R.; Stornelli, V.; Depari, A.; Flammini, A.; Sisinni, E. A Standard CMOS Bridge-Based Analog Interface for Differential Capacitive Sensors. In Proceedings of the 2017 13th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Giardini Naxos, Italy, 12–15 June 2017; pp. 281–284.

- 17. Barile, G.; Ferri, G.; Parente, F.R.; Stornelli, V.; Sisinni, E.; Depari, A.; Flammini, A. A CMOS Full-Range Linear Integrated Interface for Differential Capacitive Sensor Readout. *Sens. Actuators A Phys.* **2018**, *281*, 130–140. [CrossRef]

- Depari, A.; Sisinni, E.; Flammini, A.; Ferri, G.; Stornelli, V.; Barile, G.; Parente, F.R. Autobalancing Analog Front End for Full-Range Differential Capacitive Sensing. *IEEE Trans. Instrum. Meas.* 2018, 67, 885–893. [CrossRef]

- 19. De Marcellis, A.; Ferri, G.; Mantenuto, P. A CCII-Based Non-Inverting Schmitt Trigger and Its Application as Astable Multivibrator for Capacitive Sensor Interfacing. *Int. J. Circuit Theory Appl.* **2017**, *45*, 1060–1076. [CrossRef]

- Ferri, G.; Parente, F.R.; Stornelli, V. Current Conveyor-Based Differential Capacitance Analog Interface for Displacement Sensing Application. AEU Int. J. Electron. Commun. 2017, 81, 83–91. [CrossRef]

- George, B.; Kumar, V.J. Switched Capacitor Signal Conditioning for Differential Capacitive Sensors. *IEEE Trans. Instrum. Meas.* 2007, 56, 913–917. [CrossRef]

- Mohan, N.M.; Shet, A.R.; Kedarnath, S.; Kumar, V.J. Digital Converter for Differential Capacitive Sensors. *IEEE Trans. Instrum. Meas.* 2008, 57, 2576–2581. [CrossRef]

- Sisinni, E.; Depari, A.; Flammini, A.; Ferri, G.; Stornelli, V.; Barile, G. Full-Analog Parasitic Capacitance Compensation for AC-Excited Differential Sensors. *IEEE Trans. Instrum. Meas.* 2020, 69, 5890–5899. [CrossRef]

- 24. Barile, G.; Safari, L.; Ferri, G.; Stornelli, V. A VCII-Based Stray Insensitive Analog Interface for Differential Capacitance Sensors. *Sensors* 2019, 19, 3545. [CrossRef]

- Pullano, S.A.; Fiorillo, A.S.; Barile, G.; Stornelli, V.; Ferri, G. A Second-Generation Voltage-Conveyor-Based Interface for Ultrasonic PVDF Sensors. *Micromachines* 2021, 12, 99. [CrossRef]

- Stornelli, V.; Barile, G.; Leoni, A. A Novel General Purpose Combined DFVF/VCII Based Biomedical Amplifier. *Electronics* 2020, 9, 331. [CrossRef]

- 27. Safari, L.; Barile, G.; Stornelli, V.; Ferri, G. An Overview on the Second Generation Voltage Conveyor: Features, Design and Applications. *IEEE Trans. Circuits Syst. II Express Briefs* **2019**, *66*, 547–551. [CrossRef]

- 28. Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. Traditional Op-Amp and New VCII: A Comparison on Analog Circuits Applications. *AEU Int. J. Electron. Commun.* **2019**, *110*, 152845. [CrossRef]

- 29. Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. High Performance Voltage Output Filter Realizations Using Second Generation Voltage Conveyor. *Int. J. RF Microw. Comput.-Aided Eng.* 2018, 28, e21534. [CrossRef]

- Safari, L.; Yuce, E.; Minaei, S.; Ferri, G.; Stornelli, V. A Second-Generation Voltage Conveyor (VCII)–Based Simulated Grounded Inductor. Int. J. Circuit Theory Appl. 2020, 48, 1180–1193. [CrossRef]

- Stornelli, V.; Safari, L.; Barile, G.; Ferri, G. A New VCII Based Grounded Positive/Negative Capacitance Multiplier. AEU Int. J. Electron. Commun. 2021, 137, 153793. [CrossRef]

- 32. Yuce, E.; Safari, L.; Minaei, S.; Ferri, G.; Barile, G.; Stornelli, V. A New Simulated Inductor with Reduced Series Resistor Using a Single VCII±. *Electronics* **2021**, *10*, 1693. [CrossRef]

- 33. Barile, G.; Safari, L.; Pantoli, L.; Stornelli, V.; Ferri, G. Electronically Tunable First Order AP/LP and LP/HP Filter Topologies Using Electronically Controllable Second Generation Voltage Conveyor (CVCII). *Electronics* **2021**, *10*, 822. [CrossRef]

- 34. Stornelli, V.; Safari, L.; Barile, G.; Ferri, G. A New Extremely Low Power Temperature Insensitive Electronically Tunable VCII-Based Grounded Capacitance Multiplier. *IEEE Trans. Circuits Syst. II Express Briefs* **2021**, *68*, 72–76. [CrossRef]

- 35. Safari, L.; Barile, G.; Ferri, G.; Ragnoli, M.; Stornelli, V. A New Realization of Electronically Tunable Multiple-Input Single-Voltage Output Second-Order LP/BP Filter Using VCII. *Electronics* 2022, *11*, 646. [CrossRef]

- 36. Ferri, G.; Safari, L.; Barile, G.; Pantoli, L.; Stornelli, V. Noise Analysis and Optimization of VCII-Based SiPM Interface Circuit. *Analog Integr. Circuits Signal Process.* **2021**, *109*, 1–9. [CrossRef]

- Safari, L.; Barile, G.; Stornelli, V.; Minaei, S.; Ferri, G. Towards Realization of a Low-Voltage Class-AB VCII with High Current Drive Capability. *Electronics* 2021, 10, 2303. [CrossRef]

- 38. Ferri, G.; Safari, L.; Barile, G.; Scarsella, M.; Stornelli, V. New Resistor-Less Electronically Controllable ±C Simulator Employing VCII, DVCC, and a Grounded Capacitor. *Electronics* **2022**, *11*, 286. [CrossRef]

- 39. Barile, G.; Ferri, G.; Pantoli, L.; Ragnoli, M.; Stornelli, V.; Safari, L.; Centurelli, F.; Tommasino, P.; Trifiletti, A. Low Power Class-AB VCII with Extended Dynamic Range. *AEU Int. J. Electron. Commun.* **2022**, *146*, 154120. [CrossRef]

- 40. Safari, L.; Barile, G.; Ferri, G.; Pantoli, L.; Ragnoli, M.; Stornelli, V. A New Architecture Proposal of Half-wave Precision Rectifier using a Single VCII. In Proceedings of the 11th International Conference on Sensor Networks, Vienna, Austria, 7–8 February 2022.

- 41. Yesil, A.; Minaei, S.; Psychalinos, C. ± 0.45 V CMOS Second-Generation Voltage Conveyor Based on Super Source Follower. *Circuits Syst. Signal Process.* **2022**, *41*, 1819–1833. [CrossRef]

- 42. Pushkar, K.L. Single-Resistance Controlled Sinusoidal Oscillator Employing Single Universal Voltage Conveyor. *Circuits Syst.* 2018, *9*, 81995. [CrossRef]

- Kulshrestha, S.; Bansal, D.; Bansal, S. A New Voltage Mode KHN Biquad Using VCII. J. Circuits Syst. Comput. 2021, 30, 2150232. [CrossRef]

- 44. Koton, J.; Herencsar, N.; Vrba, K. Current and Voltage Conveyors in Current- and Voltage-Mode Precision Full-Wave Rectifiers. *Radioengineering* **2011**, *20*, 19–24.

- 45. Safari, L.; Barile, G.; Stornelli, V.; Ferri, G. A New Versatile Full Wave Rectifier Using Voltage Conveyors. *AEU Int. J. Electron. Commun.* 2020, 122, 153267. [CrossRef]

- Harrison, R.R. A Versatile Integrated Circuit for the Acquisition of Biopotentials. In Proceedings of the 2007 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 16–19 September 2007; pp. 115–122.

- 47. Scotti, G.; Pennisi, S.; Monsurrò, P.; Trifiletti, A. 88-uA 1-MHz Stray-Insensitive CMOS Current-Mode Interface IC for Di\_erential Capacitive Sensors. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2014**, *61*, 1905–1916. [CrossRef]

- 48. Mochizuki, K.; Watanabe, K.; Masuda, T. A high-accuracy high-speed signal processing circuit of differential-capacitance transducers. *IEEE Trans. Instrum. Meas.* **1998**, 47, 1244–1247. [CrossRef]

- 49. Ferri, G.; Stornelli, V.; Parente, F.; Barile, G. Full range analog Wheatstone bridge-based automatic circuit for differential capacitance sensor evaluation. *Int. J. Circuit Theory Appl.* **2016**, *45*, 2149–2156. [CrossRef]

- Silva, M.; Oliveira, L. Regulated Common-Gate Transimpedance Amplifier Designed to Operate with a Silicon Photomultiplier at the Input. *IEEE Trans. Circuits Syst. I Regul. Pap.* 2014, 61, 725–735. [CrossRef]

- 51. Albuquerque, E.; Bexiga, V.; Bugalho, R.; Carriço, B.; Ferreira, C.S.; Ferreira, M.; Godinho, J.; Gonçalves, F.; Leong, C.; Lousã, P.; et al. Experimental characterization of the 192 channel CLEAR-PEM front-end ASIC coupled to a multi-pixel APD readout of LYSO:Ce crystals. *Nucl. Instrum. Methods Phys. Res. Sect. A* 2009, 598, 802–814. [CrossRef]

- Albuquerque, E.; Silva, M. Project PET, 4th Progress Report: Revised Design of the Front-End ASIC. Analog Processing; INESC-ID INESC-ID Technical Report 36/2006; INESC-ID: Lisboa, Portugal, 2006.

- Giannakopoulos, S.; He, Z.S.; Darwazeh, I.; Zirath, H. Di\_erential common base TIA with 56 dB Ohm gain and 45 GHz bandwidth in 130 nm SiGe. In Proceedings of the 2017 IEEE Asia Pacific Microwave Conference (APMC), Kuala Lumpar, Malaysia, 13–16 November 2017; pp. 1107–1110.

- Song, S.; Rooijakkers, M.; Harpe, P.; Rabotti, C.; Mischi, M.; van Roermund, A.; Cantatore, E. A Noise Reconfigurable Current-Reuse Resistive Feedback Amplifier with Signal Dependent Power Consumption for Fetal ECG Monitoring. *IEEE Sens. J.* 2016, 16, 8304–8313. [CrossRef]

- Shen, L.; Lu, N.; Sun, N. A 1-V 0.25-μW Inverter Stacking Amplifier with 1.07 Noise Efficiency Factor. *IEEE J. Solid-State Circuits* 2018, 53, 896–905. [CrossRef]

- Dong, S.; Tong, X.; Liu, L.; Yang, A.; Li, R. A Gain & Bandwidth Reprogrammable Neural Recording Amplifier with Leakage Reduction Switches. In Proceedings of the IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Xi'an, China, 12–14 June 2019; pp. 1–3.

- Liu, L.; Zhuang, Y.; Zhang, L.; Jing, K.; Dong, S.; Chen, Y. A Reconfigurable Low Noise Amplifier with Sub-amplifier Compensation for Wearable Wireless Neural Recording System. In Proceedings of the IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Xi'an, China, 12–14 June 2019; pp. 1–3.

- Oreggioni, J.; Caputi, A.A.; Silveira, F. Current-Efficient Preamplifier Architecture for CMRR Sensitive Neural Recording Applications. *IEEE Trans. Biomed. Circuits Syst.* 2018, 12, 689–699. [CrossRef]