# Article Impact of Line Edge Roughness on ReRAM Uniformity and Scaling

Vassilios Constantoudis <sup>1,2,\*</sup>, George Papavieros <sup>1,2</sup>, Panagiotis Karakolis <sup>1,3</sup>, Ali Khiat <sup>4</sup>, Themistoklis Prodromakis <sup>4</sup> and Panagiotis Dimitrakis <sup>1,\*</sup>

- <sup>1</sup> Institute of Nanoscience and Nanotechnology, NCSR Demokritos, 15341 Aghia Paraskevi, Greece; g.papavieros@inn.demokritos.gr (G.P.); p.karakolis@inn.demokritos.gr (P.K.)

- <sup>2</sup> Nanometrisis P.C., 15341 Aghia Paraskevi, Greece

- <sup>3</sup> Department of Physics, University of Patras, GR 265 00 Patras, Greece

- <sup>4</sup> Electronic Materials and Devices Research Group, Zepler Institute for Photonics and Nanoelectronics, University of Southampton, Southampton SO171BJ, UK; ak1a12@ecs.soton.ac.uk (A.K.); T.Prodromakis@soton.ac.uk (T.P.)

- \* Correspondence: v.constantoudis@inn.demokritos.gr (V.C.); p.dimitrakis@inn.demokritos.gr (P.D.)

Received: 29 September 2019; Accepted: 21 November 2019; Published: 30 November 2019

**Abstract:** We investigate the effects of Line Edge Roughness (LER) of electrode lines on the uniformity of Resistive Random Access Memory (ReRAM) device areas in cross-point architectures. To this end, a modeling approach is implemented based on the generation of 2D cross-point patterns with predefined and controlled LER and pattern parameters. The aim is to evaluate the significance of LER in the variability of device areas and their performances and to pinpoint the most critical parameters and conditions. It is found that conventional LER parameters may induce >10% area variability depending on pattern dimensions and cross edge/line correlations. Increased edge correlations in lines such as those that appeared in Double Patterning and Directed Self-assembly Lithography techniques lead to reduced area variability. Finally, a theoretical formula is derived to explain the numerical dependencies of the modeling method.

**Keywords:** Resistive Random Access Memory (ReRAM); Line Edge Roughness (LER); variability; uniformity; modeling; lithography

## 1. Introduction

Resistive Random Access Memory (ReRAM) technologies are considered as one of the most promising candidates for future nonvolatile memory (NVM) applications due to their high memory capacity [1], their simple two terminal architecture, and their excellent scalability [2]. ReRAM cells can be programmed faster than current NVMs and at lower voltages, overall leading to a significant reduction in energy consumption per bit [3]. The cross-point metal-insulator-metal (MIM) cell simple structure requires very low thermal budget and thus can be integrated easily in the current CMOS Back End of Line (BEOL) processing steps [4]. Large memory blocks have been implemented and demonstrated, following the cross-point architecture [5]. The cross-point area  $F \times F$ , F is the lithography node, can be as small as  $2 \text{ nm} \times 2 \text{ nm}$  [6] leading to a very small cell footprint (area/bit) 4F<sup>2</sup>. Conductive AFM experiments have demonstrated that the ReRAM memory cell area can be as small as that of an AFM tip [7]. In addition, the 3D stacking of different memory layers [8] reduces the cell's footprint to  $4F^2/n$ , where n is the number of the stacked memory layers, and hence severely increases the density of the ReRAM memory chips. Moreover, the ReRAM cell can be used to realize memristive devices to implement new computing paradigms like neuromorphic [3,9], reconfigurable electronics [10], and logic-in-memory [11].

The uniformity of the cell SET and RESET voltages ( $V_{SET}$  and  $V_{RESET}$ , respectively) is a key-challenge to large-scale manufacturing of ReRAM technology. Up to now, it has been mainly related to the stochastic nature of conducting a filament creation process. Remedies that have been proposed consider (a) engineering of electrode/oxide interface [12], (b) inserting seeds (nanoparticles) in the oxide bulk [13], and (c) reduction of the size of cell area [14]. The latter is related to the scaling trends of ReRAM devices and is a great advantage of this technology since scaling down the dimensions of a ReRAM cell goes with the increase in performance uniformity due to the mitigation of stochastic filament formation. Thus, scalability is generally considered an advantage of ReRAM owing to the filamentary conduction and switching mechanisms. The effect of the reduction of the cell size area to the various parameters of ReRAM operation is an active matter of debate. To that end, in Reference [14] a simplified analytical model to describe the area and thickness scaling of forming voltage is proposed. Binary-oxide ReRAM scalability performance has drawn the attention of various groups. The general scaling trend of the high and low resistance states from various metal oxide ReRAMs has been presented in Reference [15]. The dependence of the scaling area on various ReRAM operation parameters (Resistance, SET/RESET current, SET/RESET voltage) has been studied thoroughly for HfO<sub>x</sub> [16,17], TaO<sub>x</sub> [18], SiO<sub>2</sub> [19], ZrO<sub>2</sub> [20], and recently for Al<sub>2</sub>O<sub>3</sub> [21] and for TiO<sub>2</sub> [22]. Similar scalability issues have been examined for perovskite material-based ReRAMs, such as SrTiO<sub>3</sub> [23], and metal nitrides, such as AlN [24] and NiN [25].

However, up to now no special attention has been paid on deviations frompattern's uniformity induced by the fabrication process and material properties. In CMOS technology, one of the most important sources of such deviations from manufacturing uniformity is related to the Line Edge Roughness (LER). LER is actually the sidewall roughness of pattern lines manufactured via standard lithographic rules, as often observed via top-down SEM images. The effect of LER becomes more evident as the size of devices is reduced, which is the reason for the recent upsurge of interest in LER control in modern <20 nm semiconductor manufacturing [26]. Obviously, LER is responsible for the area variability of devices in a crossbar (Xbar) array and, furthermore, the cell-to-cell and wafer-to-wafer variability that appear in the operation parameters of ReRAM memory cells in Xbar arrays. More specifically, as mentioned in [15], the resistance at HRS increases as the inverse of the area cell A (i.e.,  $R_{HRS}$ ~1/A) while the reset current increases as A decreases. Furthermore, the reduction of the cell size A attributes to local heating causing faster switching times [17]. In addition, forming and SET voltages also increase as the cell area A decreases [17]. These detrimental LER effects are expected to become stronger increasing the size of the memory crossbar array: The larger the memory array the stronger the effects are.

The importance of LER is justified by the evaluation of its effects on device performance. This can be done through carefully designed experiments or modeling/simulation studies. Results from such studies help defining the specifications for allowed LER in roadmaps and factory production lines. Clearly, the level of acceptable LER is defined by the operating constraints of distinct applications that employ nanoscale devices. Up to now, several modeling and experimental investigations have been performed for conventional MOSFET [27–30] and FinFET [31,32] devices. On the contrary, very few studies have been devoted to the LER effects on memory and especially ReRAM devices. In the fabrication of ReRAM and especially in the cross-point configurations, the LER of metallic lines may affect device performance through the induced variability to the cross-point cell areas and consequently to the device resistance.

Furthermore, it was recently realized that LER characteristics are sensitive to the applied lithographic technique [33]. The main point of differentiation comes from the degree of correlations between the fabricated edges and lines. In EUV patterns, for example, the nearby lines and edges are totally uncorrelated while in Multiple Pattern (MP) techniques correlations are induced mainly between the edges of each line, whereas lines are still independent at least for Double Patterning (DP) schemes. On the contrary, in Directed Self-Assembly (DSA) lithography even nearby lines exhibit correlated fluctuations arising from the very self-assembly nature of the process and the sidewall

roughness of grapho-epitaxy grating used for the alignment of lines. Therefore, LER modeling should always consider such aspects and adjust the modeled patterns according to the considered lithography. Up to now, the modeling strategies for the generation of line edges similar to the fabricated ones are based on inverse Fourier techniques, where no correlations are taken into account between edges or lines [34,35].

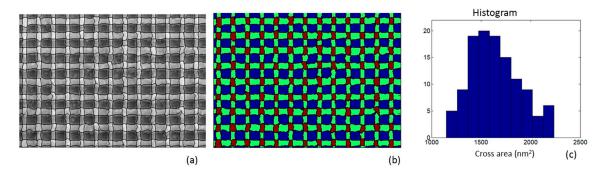

In order to get a better picture of the LER impact on cell area uniformity, one can observe Figure 1a where several ReRAM prototypes, of cross-point architecture, were fabricated by e-beam lithography and are depicted in a top-down SEM image. Furthermore, on the same SEM image the detected edges defining the borders of electrode lines are illustrated with black color. It can be clearly seen that the roughness of the metal edges induces non-uniform cell areas (see Figure 1b). The distribution of the cell areas is presented in Figure 1c where one can notice the wide distribution of cell area values. This data supports our claim that LER needs to be considered carefully for achieving a uniform and reliable ReRAM technology and deserves more investigation.

**Figure 1.** (a) A top-down SEM image of a cross-point pattern with the detected edges of the vertical and horizontal metal lines defining the crossing areas, (b) a colored illustration of the SEM image to show the crossing areas more clearly in red color and the metal lines in green color, (c) the histogram of the calculated cross-point area values in nm<sup>2</sup>. The Line Edge Roughness (LER) (average root mean square (rms) value) of the vertical and horizontal lines was measured and found equal to 2.6 and 3.8 nm, respectively. The width of the distribution of cross areas (standard deviation) is found to be almost 16% of the mean value. Therefore, the commonly used three times this value reaches almost 50% of the mean value indicating the strong impact of LER of metal lines to the nonuniformity of Resistive Random Access Memory (ReRAM) device areas.

In this paper, we evaluate the effects of LER of metallic lines on the device area uniformity, which is critical for the device performance. Three types of line patterns are considered corresponding to EUV, Multiple Patterning (MP), and DSA patterns to compare these with respect to their vulnerability to LER defect. In Section 2, the modeling methodology is presented and explained. The results of the modeling approach to EUV, MP, and DSA-based patterns are shown and discussed in Section 3. In the end of the same section, we also derive an analytical formula capturing the numerical modeling results with quantitative success. The last section, Section 4, summarizes the findings of the paper and draws the main conclusions.

## 2. Modeling Methodology

## 2.1. Background of Modeling: LER Characterization in Different Lithography Techniques

LER is usually defined as the deviation from smoothness (flatness) of the sidewalls of resist or substrate lines. In top-down SEM images, this deviation is reflected through the roughness of the edge defining the 2D borders of the line region. In the initial stages of LER studies, line edge points were considered uncorrelated and the main emphasis was given on the measurement of their root mean square (rms) value (standard deviation), quantifying the wideness of the edge point distribution. However, quite early, the characterization scheme was enriched with more parameters and functions aiming to capture and quantify the spatial/lateral or frequency aspects of LER preserving the dominant significance of rms. To this end, a three-parameter model has been proposed [26] consisting of rms value, correlation length  $\xi$ , and roughness exponent  $\alpha$  (related to the fractal dimension  $d = 2-\alpha$ ) and extensively used in different applications. The first parameter rms quantifies the vertical aspects of LER and is calculated by the standard deviation of the edge points about their mean value. The other two parameters ( $\xi$  and  $\alpha$ ) focus on the spatial aspects of LER. The correlation length  $\xi$  quantifies the window inside which the edge points can be considered correlated, i.e., they have similar deviations from the mean value, and delivers a statistical estimation of the mean width of edge fluctuations. Large values of  $\xi$  mean slowly varying edges while small values characterize more jagged edges. The correlation length is normally calculated through the autocorrelation function R(r) as the distance r at which R(r) is lowering beneath 1/e, i.e., R( $\xi$ ) = 1/e [36]. The roughness exponent 0 <  $\alpha$  < 1 quantifies the contribution of various scales and frequencies to the whole LER. When  $\alpha$  takes on low values, high frequencies dominate, whereas whenit approaches 1, the edge becomes smoother at small scales and the importance of high frequency fluctuations is being lessened.

When a more detailed function-like characterization of spatial and frequency LER aspects is demanded, the Power Spectrum (PS) and the Height–Height Correlation Function (HHCF) can be calculated and elaborated. The overall shape of these functions is linked to the three-parameter model, when LER obeys a self-affine fractal symmetry [36]. The effects of LER on line width fluctuations (usually called Line Width Roughness (LWR)) complete the overall picture of the conventional approach to LER metrology. The relationship between LER and LWR metrics has been clarified and it can be shown that the low frequency LWR could have a significant contribution to the total budget of local Critical Dimension Uniformity (CDU). This effect has underlined the importance of estimating the PS of LWR, which quantifies the contribution to LWR from different frequency areas. A detailed presentation of the conventional LER and LWR metrology can be found in [26].

Nevertheless, during the recent years significant changes in lithographic landscape have been evidenced. The conventional scaling down of feature dimensions, based on the optimization of wavelength and Numerical Aperture (NA), has been replaced by a more etch-based and material-driven resolution enhancement, which duplicates the density of patterns through successive deposition and etching steps. The family of these MP techniques is currently used in high volume manufacturing in semiconductor industries. Additionally, the concept of self-assembly of block copolymers has been employed in lithography research in the last 10 years due to its ability to easily provide line/space patterns with widths less than 20 nm. The DSA lithography has seen an upsurge and very important advances have been performed in defect reduction and scaling improvement. However, what is usually missing is the effect that these new lithographic approaches have on LER and its metrology characterization. The key aspect of these effects is the lateral (across line direction) correlations they introduce in line/space patterns. In the EUV lithography patterns, the LER of edges are uncorrelated and no propagation of edge fluctuations is noticed between the edges of a line or the nearby lines of a pattern. On the contrary, in MP lithography patterns, the edges of the same line fluctuate in a correlated manner forming wiggling lines. A more dramatic change is observed in DSA patterns. Here, not only the line edges but also the lines themselves present correlations in the way they fluctuate. To capture these new aspects of LER, an extended framework for LER/LWR metrology has been proposed and elaborated based on the c-factor parameter, function, and correlation length. A detailed presentation and examples of application of these metrics can be found in [35].

## 2.2. Implementation of Modeling

The key idea of our approach is to model LER effects in cross-point area statistics using the 2D projections of the real 3D patterns, as they are shown in top-down SEM images similar to that in Figure 1. The assumption behind this approach is that 3D morphological variations do not have an important contribution to LER impact on device variability. This assumption is supported by

recent observations according to which the sidewall roughness of lithographic lines does not change significantly along z-direction since it exhibits a curtain-like morphology [37].

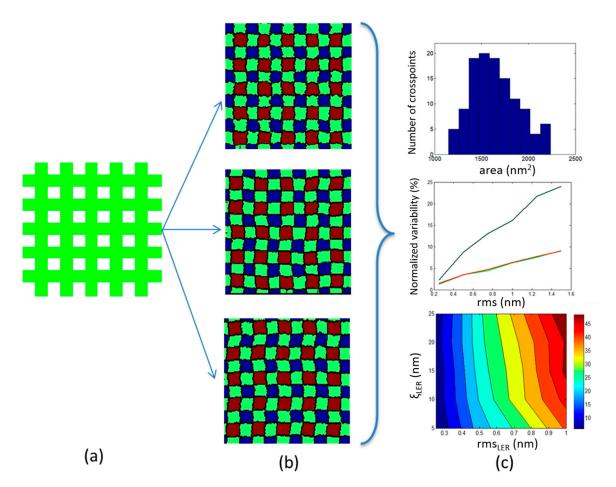

The modeling methodology is implemented in three steps. First, the structural parameters of the cross-point pattern are defined including line width (Critical Dimension, *CD*) and pitch values. The numbers of both vertical and horizontal lines are included in the modeling as well as. These parameters can differ in vertical (y) and horizontal (x) line patterns, though throughout this study we mainly consider the symmetrical case where  $CD_X = CD_Y$  and pitch<sub>x</sub> = pitch<sub>y</sub>. Based on these parameters, the ideal smooth pattern can be generated as shown in Figure 2a. In the second step, the smooth edges are converted to rough edges characterized by the input predetermined roughness parameters: rms,  $\xi$ ,  $\alpha$ . The generation of rough edges is made using the convolution method and requires the use of a model function for the Power Spectrum or the Height–Height Correlation Function. Here, we extensively use the following HHCF *G*(*r*) that is also used in self-affine rough processes [34,38]:

$$G^{2}(r) = 2rms^{2}(1 - e^{(-\frac{r}{\xi})^{2\alpha}}).$$

(1)

**Figure 2.** A schematic view of our modeling steps for LER effects on device uniformity. First, a pattern is formed (**a**) with the given parameters (Critical Dimension (*CD*), pitch, number of lines), then (**b**) roughness is imposed on the edges to get LER with predefined parameters, and then in (**c**) the statistical analysis of cross areas  $A_i$  is performed to get the normalized standard deviation  $\sigma(A)$  versus LER parameters.

The successive application of the convolution method with no further processing of edges produces uncorrelated edges, which then can be positioned according to *CD* and pitch values to build the whole cross-point pattern. The generated pattern can be used to model the 2D projection of line/space

structures fabricated by mask-based lithographic rules (EUV or 193i). When MP or DSA patterns are sought, we may add correlation either between the edges of the same line or to expand these between nearby lines to get DSA-like patterns. Figure 2b shows examples of such patterns with controlled LER parameters as well as cross-edge and cross-line correlations.

In the third step of our methodology, we measure the areas of cross-points  $A_i$ ,  $I = 1, ..., N_x N_y$  where horizontal and vertical lines overlap in the considered rough pattern of  $N_x x N_y$  lines. Then we calculate the normalized standard deviation  $\sigma(A)$  of the  $A_i$  values (=*std*( $A_i$ )/<  $A_i$  >) and we plot it for various dimensional and LER parameters and edge/line correlation levels (see Figure 2c).

## 3. Results and Discussion

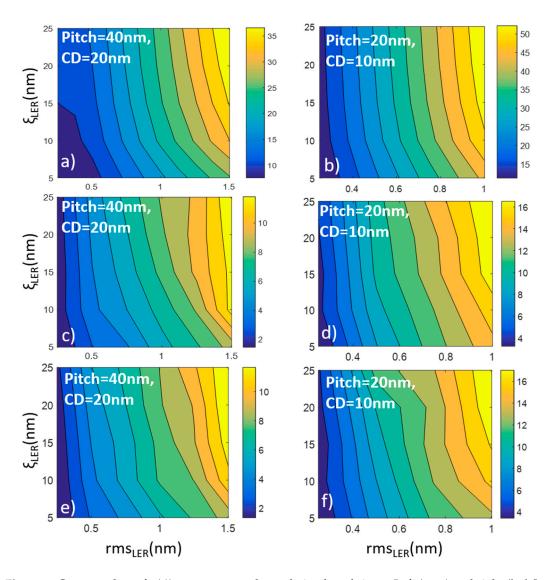

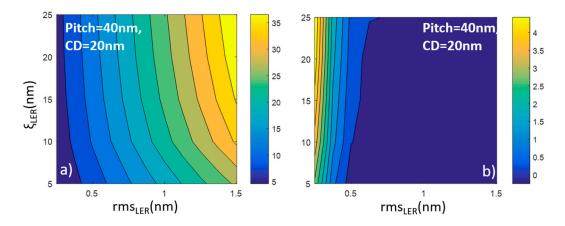

The results of our modeling calculations are collectively illustrated in Figure 3, which displays six contour plots. Each one of these plots depicts the dependence of  $\sigma(A)$  on the LER parameters rms and  $\xi$  given that these parameters are considered to quantify LER according to the last editions of ITRS [39]. In all runs, the roughness exponent  $\alpha$  is kept fixed to 0.5 in conformity with more experimental measurements. We consider that both horizontal and vertical lines have similar LER parameters. The left column of Figure 3a,c,e contains the contour plots with CD = 20 nm and pitch = 40 nm while the right column shows the results when the pattern scales down at CD = 10 nm and pitch = 20 nm. The different rows account for increased levels of horizontal (cross-line) correlations between edges and lines. In the first row, both edges and lines are generated to be uncorrelated to capture the case of mask lithography line structures (EUV and 193i). The second row contains the results for cross-point patterns where the edges of each line are correlated, though the lines themselves fluctuate independently. The latter pattern resembles the line/space structures acquired by Double Patterning Lithography techniques. In the third row, the contour plots concern model patterns where the horizontal correlations propagate across both edges and lines similarly to what is happening in DSAL.

From the contour plots of Figure 3, we are able to extract conclusions and discuss the following issues: (a) the dependence of  $\sigma(A)$  on LER parameters rms and  $\xi$  which seems to exhibit a similar pattern in all cases, (b) the effects of scaling down the pattern dimensions, and (c) the effects of cross-edge and line correlations.

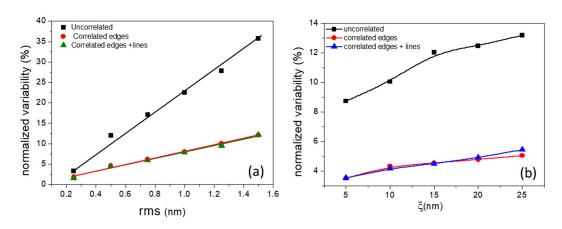

#### 3.1. The Impact of LER Parameters Rms, $\xi$

The overall shape of all contour plots in Figure 3 is characterized by the dominance of vertical contour lines, which reveal the stronger dependence of area uniformity on rms with respect to that of the correlation length. In order to focus on the dependencies themselves, we take a horizontal and vertical cross-section of the contour diagrams and the outcome plots are shown in Figure 4 for all considered cases. One can easily notice the linear increase of  $\sigma(A)$  with rms value in all cases, while the effects of  $\xi$  are sublinear justifying the dominant role of rms in the effects of LER on cross area uniformity. In other words, both rms and  $\xi$  in LER degrade device area variability with rms exhibiting the primary effect.

**Figure 3.** Contour plots of  $\sigma(A)$  vs. rms<sub>LER</sub> and correlation length  $\xi_{\text{LER}}$ . Left (**a**,**c**,**e**) and right (**b**,**d**,**f**) columns contain the plots for CD = 20 nm and CD = 10 nm, respectively. Furthermore, in the second (**c**,**d**) and third (**e**,**f**) row the calculations have been done considering patterns with correlated edges and correlated edges and lines respectively.

**Figure 4.** An example of the dependence of the normalized variability  $\sigma(A)$  on (**a**) rms and (**b**)  $\xi$  for typical parameters. One can notice the linear and sublinear increase of  $\sigma(A)$  vs. rms and  $\xi$ , respectively.

#### 3.2. The Impact of Scaling Device Size

The comparison of the contour plots of the left and right columns reveals that the scaling down of pattern dimensions by a factor 2 (quadrupling of device density) is associated with an almost doubling of normalized area variability  $\sigma(A)$ . This observation holds at all rows, i.e., it is independent of the level of edge/line correlations.

#### 3.3. The Impact of Edge and Line Correlations

When MP or DSA lithographic techniques are used for ReRAM pattern fabrication, edges and lines exhibit cross-correlations, i.e., they fluctuate in a correlated manner. The second and third rows of Figure 3 show the contour plots for  $\sigma(A)$  when the pattern exhibits only edge and both edge and line correlations, respectively. Although the pattern of contour lines remain almost unaltered, the  $\sigma(A)$  values demonstrate a clear reduction with respect to the values of first rows approximately by a factor 3. The amount of reduction is similar at the contour plots of the second and third rows, which indicates that the critical correlations for variability drop are those between edges. The cross-line correlations do not seem to play any role in LER-induced degradation effects on area uniformity.

## 3.4. Analytical Formula for LER Effects on Area Variability

The dependencies of  $\sigma(A)$  on LER parameters found by modeling and shown in Figure 3 can be captured in an analytical formula which can be derived as follows: For patterns with smooth edges (no LER) the cross-point areas are fixed in all devices and equal to  $A_i = CD_XCD_Y$  with no variability at all. When we consider rough edges, LER induces local variability in line widths, which is usually called Line Width Roughness (LWR). Therefore, each crossing area can be roughly characterized by  $A_i = CD_{ix}CD_{iy}$ , where  $CD_{ix}$  and  $CD_{iy}$  are the average line widths across x- and y-directions enclosed in the i-th crossing area. Due to LER and LWR,  $CD_{ix}$  and  $CD_{iy}$  change randomly from area to area. If we assume that on average this variability is similar to both vertical and horizontal lines, we get for the  $\sigma(A)$ :

$$\sigma(A) = \frac{std(A_i)}{\langle A_i \rangle} \approx \frac{\sqrt{2std(CD_i)}}{\langle CD_i \rangle}.$$

(2)

The relationship of *CD* variance  $(std^2(CD_i))$  with local and total variances of LWR values has been studied extensively in LER literature and the following formula can be proven [20]:

$$std^{2}(CD_{i}) + \langle rms_{LWR}^{2}(CD_{i}) \rangle = rms_{LWR}^{2}(total),$$

(3)

where  $rms_{LWR}(total)$  is the rms value of LWR for the total lines included in model patterns, which assume to get sufficiently large lengths so that the  $rms_{LWR}$  value stabilizes at a fixed value, and  $< rms_{LWR}^2(CD_i) >$  is the mean variance of LWR calculated inside the segments of length  $CD_i$  and averaged over all considered segments.

In order to get the relationship of  $\sigma(A)$  with the input LER parameters, we need to pass from LWR to LER parameters. This can be achieved through the following formula connecting LWR and LER assuming similarity between left and right LER:

$$rms_{LWR}^2 = 2(1-c) \ rms_{LER}^2.$$

(4)

Here, *c* is the c-factor quantifying the cross-correlations between the left and right edges of lines. For totally uncorrelated edges, c = 0, whereas for fully correlated (anti-correlated), c = 1 (-1) [26,33]. By combining (2), (3), and (4) we read:

$$\sigma(A) = \frac{2}{\langle CD_i \rangle} \sqrt{(1-c)(rms_{LER}^2(total) - \langle rms_{LER}^2(CD_i) \rangle)}.$$

(5)

The Formula (5) can be further processed in the case of edges with exponential autocorrelation functions (roughness exponent  $\alpha$  = 0.5) since for such edges it holds that

$$rms_{LER}^{2} (CD) = rms_{LER}^{2} (total) [1 - \frac{2\xi}{CD} (1 + \frac{\xi}{CD} e^{-\frac{CD}{\xi}} - 1)].$$

(6)

Inserting (6) into (5) we get the final formula for the dependence of  $\sigma(A)$  on LER parameters:

$$\sigma(A) = 2\sqrt{2(1-c)} \frac{rms_{LER}}{CD} \frac{\xi}{CD} \sqrt{\frac{CD}{\xi} + e^{-CD/\xi} - 1}.$$

(7)

Equation (7) incorporates all the dependencies of normalized area variability on the dimensional parameters (*CD*), the principal LER parameters ( $rms_{LER}$ ,  $\xi$ ) and the level of edge correlations (c-factor). As expected from the numerical results, pitch and line correlations are not included since they have no impact. One can easily notice that the analytical Formula (7) predicts (a) the linear proportionality of  $\sigma(A)$  to  $rms_{LER}$ , (b) the sublinear increase of  $\sigma(A)$  with  $\xi$ , (c) the almost linear inverse proportionality impact of *CD*, and (d) the reduced effects of increased edge correlations on  $\sigma(A)$  quantified by *c* through the factor (1-*c*).

In order to get a more quantified and complete comparison of the analytical prediction with the numerical results, we show in Figure 5a a contour plot with the dependencies of  $\sigma(A)$  on LER parameters (rms,  $\xi$ ) as derived by the analytical Formula (7). We have chosen c = 0 (no edge correlations) and CD = 20 nm, which are the parameters of the numerical contour plot of Figure 3a. One can clearly indicate the striking qualitative and quantitative similarity of two contour plots, which is more directly and quantitatively illustrated in Figure 5b where the difference of the numerical and analytical normalized variability  $\sigma(A)$  is shown versus rms and  $\xi$  parameters. The difference is always very close to zero and justifies the predictive power of the analytical formula. The sole exception is for the small rms values lower than 0.5 nm where the analytical formula seems to underestimate the numerical results. However, the observed discrepancy is due to issues with the numerical results. More specifically, in order to simulate the real procedure where the LER effects are evaluated through the analysis of SEM images (see Figure 1), in the numerical modeling we pixelize the edge data by rounding the generated edge points from the generator algorithms. We have shown that this discretization (pixelization) process induces a noise impact on LER and causes an increase of the measured rms value as explained in [40]. Therefore, in these regimes with extremely small rms values, one should trust the predictions of the analytical Formula (7) more than the numerical results of the 2D modeling.

**Figure 5.** (a) Contour plot of the normalized variability  $\sigma(A)$  cross-point areas versus the LER parameters rms and  $\xi$  for CD = 20 nm and c = 0 (no edge correlations) and (b) the difference of numerical and analytical predictions for  $\sigma(A)$  for the standard parameters CD = 20 nm and c = 0. One can notice the striking similarity of numerical and analytical results with the slight exception of very small rms values where numerical results are biased due to pixelization of edge data.

The similarity between numerical results and analytical predictions was confirmed independently of *CD* and edge correlations. This means that the Formula (7) comprises a strong analytical tool to get control and deeper understanding of the LER effects on ReRAM area variability and performance degradation since it captures successfully the impact of LER main parameters (rms,  $\xi$ ) as well as of the line width (*CD*) and edge correlations which may come from different lithography steps used in pattern formation.

## 4. Conclusions

In this work, we model the effect of lithographic performance parameters on the operation of ReRAM devices, assuming the main three lithographic techniques: EUV, MP and DSA. According to our numerical model, it is found that both rms and  $\xi$  in LER degrade device area variability with rms exhibiting the primary effect. Additionally, it is found that edge correlations favor area uniformity while the normalized area variability is doubled when the size becomes half of the initial. For comparison, an analytical model was developed also to simulate the impact of lithography performance parameters. The comparison between the 2D numerical and the analytical one reveals that both provide the same results independently of *CD* and edge correlations. Nevertheless, the analytical model is more accurate at extremely small rms values. In this context, the developed numerical and analytical models are highly valuable predictive tools for the integration of ReRAM devices at very small technology nodes.

Author Contributions: Conceptualization, V.C., T.P., and P.D.; data curation, V.C., G.P., A.K., and T.P.; formal analysis, V.C.; funding acquisition, V.C.; investigation, V.C., G.P., P.K., A.K., T.P., and P.D.; methodology, V.C. and P.D.; project administration, V.C.; resources, A.K. and T.P.; software, V.C. and G.P.; supervision, V.C.; validation, V.C.; visualization, V.C., G.P., and P.K.; writing—original draft, V.C., P.K., T.P., and P.D.; writing—review & editing, V.C., T.P., and P.D.

**Funding:** For this research, V.C., G.P., and P.D. have received funding from the EMPIR programme "3DNano" co-financed by the Participating States and from the European Union's Horizon 2020 research and innovation programme. P.K. and P.D. gratefully acknowledge the financial support from the Greece–Russia bilateral joint research project MEM-Q (proj.no./MIS T $4\Delta P\Omega$ -00030/5021467) and research project RADAR (proj.no./MIS T $1E\Delta K$ -00329/5032784)) supported by GSRT and funded by National and European funds. Finally, the authors A.K. and T.P. wish to acknowledge the financial support of the Engineering and Physical Sciences Research Council (EPSRC) grants EP/K017829/1, EP/R024642/1.

Conflicts of Interest: The authors declare no conflict of interest.

## References

- 1. Stathopoulos, S.; Khiat, A.; Trapatseli, M.; Cortese, S.; Serb, A.; Valov, I.; Prodromakis, T. Multibit memory operation of metal-oxide bi-layer memristors. *Sci. Rep.* **2017**, *7*, 17532. [CrossRef] [PubMed]

- 2. Khiat, A.; Ayliffe, P.; Prodromakis, T. High Density Crossbar Arrays with Sub-15 nm Single Cells via Liftoff Process Only. *Sci. Rep.* **2016**, *6*, 32614. [CrossRef]

- 3. Wu, H.; Yao, P.; Gao, B.; Wu, W.; Zhang, Q.; Zhang, W.; Deng, N.; Wu, D.; Wong, H.-S.P.; Yu, S.; et al. Device and circuit optimization of RRAM for Neuromorphic computing. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 11.5.1–11.5.4.

- Lv, H.; Xu, X.; Yuan, P.; Dong, D.; Gong, T.; Liu, J.; Yu, Z.; Huang, P.; Zhang, K.; Huo, C.; et al. BEOL Based RRAM with One Extra-mask for Low Cost, Highly Reliable Embedded Application in 28 nm Node and Beyond. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 2.4.1–2.4.4.

- Fujitsu Semiconductor Launches World's Largest Density 4 Mbit ReRAM Product for Mass Production. 2016. Available online: https://phys.org/news/2016-10-fujitsu-semiconductor-world-largest-density.html (accessed on 10 December 2017).

- Govoreanu, B.; Kar, G.S.; Chen, Y.-Y.; Paraschiv, V.; Kubicek, S.; Fantini, A.; Radu, I.; Goux, L.; Clima, S.; Degraeve, R.; et al. 10 × 10 nm<sup>2</sup> Hf/HfO<sub>x</sub> cross-point resistive RAM with excellent performance, reliability and low-energy operation. In Proceedings of the International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 31.6.1–31.6.4. [CrossRef]

- Wedig, A.; Luebben, M.; Cho, D.-Y.; Moors, M.; Skaja, K.; Rana, V.; Hasegawa, T.; Adepalli, K.K.; Yildiz, B.; Waser, R.; et al. Nanoscale cation motion in TaO<sub>x</sub>, HfO<sub>x</sub> and TiO<sub>x</sub> memristive systems. *Nat. Nanotechnol.* 2016, 11, 67–74. [CrossRef] [PubMed]

- Luo, Q.; Xu, X.; Gong, T.; Lv, H.; Dong, D.; Ma, H.; Yuan, P.; Gao, J.; Liu, J.; Yu, Z.; et al. 8-layers 3D Vertical RRAM with Excellent Scalability towards Storage Class Memory Applications. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 2.7.1–2.7.4.

- Serb, A.; Bill, J.; Khiat, A.; Berdan, R.; Legenstein, R.; Prodromakis, T. Unsupervised learning in probabilistic neural networks with multi-state metal-oxide memristive synapses. *Nat. Commun.* 2016, *7*, 12611. [CrossRef] [PubMed]

- Serb, A.; Khiat, A.; Prodromakis, T. Seamlessly Fused Digital-Analogue Reconfigurable Computing using Memristors. *Nat. Commun.* 2018, *9*, 2170. [CrossRef]

- 11. Chen, W.-H.; Lin, W.-J.; Lai, L.-Y.; Li, S.; Hsu, C.-H.; Lin, H.-T.; Lee, H.-Y.; Su, J.-W.; Xie, Y.; Sheu, S.-S.; et al. A 16Mb Dual-Mode ReRAM Macro with Sub-14ns Computing-In-Memory and Memory Functions Enabled by Self-Write Termination Scheme. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 28.2.1–28.2.4.

- Lübben, M.; Karakolis, P.; Ioannou-Sougleridis, V.; Normand, P.; Dimitrakis, P.; Valov, I. Graphene-Modified Interface Controls Transition from VCM to ECM Switching Modes in Ta/TaO<sub>x</sub> Based Memristive Devices. *Adv. Mater.* 2015, *27*, 6202–6207. [CrossRef]

- Tsigkourakos, M.; Bousoulas, P.; Aslanidis, V.; Skotadis, E.; Tsoukalas, D. Ultra-Low Power Multilevel Switching with Enhanced Uniformity in Forming Free TiO<sub>2-x</sub>-Based RRAM with Embedded Pt Nanocrystals. *Phys. Status Solidi (a)* 2017, 214, 1700570. [CrossRef]

- 14. Chen, A. Area and Thickness Scaling of Forming Voltage of Resistive Switching Memories. *IEEE Trans. Electron Devices* **2014**, *35*, 57–59. [CrossRef]

- 15. Wong, H.-S.P.; Lee, H.-Y.; Yu, S.; Chen, Y.-S.; Wu, Y.; Chen, P.-S.; Lee, B.; Chen, F.T.; Tsai, M.-J. Metal Oxide ReRAM. *Proc. IEEE* **2012**, *100*, 1951–1970. [CrossRef]

- 16. Fang, Z.; Li, X.; Wang, X.; Lo, P. Area Dependent Low Frequency Noise in Metal Oxide Based Resistive Random Access Memory. *Int. J. Inf. Electron. Eng.* **2012**, *2*, 882–884. [CrossRef]

- Lee, J.; Park, J.; Jung, S.; Hwang, H. Scaling Effect of Device Area and Film Thickness on Electrical and Reliability Characteristics of RRAM. In Proceedings of the IEEE International Interconnect Technology Conference and Materials for Advanced Metallization (IITC/MAM), Dresden, Germany, 8–12 May 2011. [CrossRef]

- Hayakawa, Y.; Himeno, A.; Yasuhara, R.; Boullart, W.; Vecchio, E.; Vandeweyer, T.; Witters, T.; Crotti, D.; Jurczak, M.; Fujii, S.; et al. Highly reliable TaOx ReRAM with centralized filament for 28-nm embedded application. In Proceedings of the Symposium on VLSI Technology Digest of Technical Papers, T14–T15, Kyoto, Japan, 17–19 June 2015. [CrossRef]

- Choi, B.J.; Chen, A.B.K.; Yang, X.; Chen, I.-W. Purely Electronic Switching with High Uniformity, Resistance Tunability, and Good Retention in Pt-Dispersed SiO<sub>2</sub> Thin Films for ReRAM. *Adv. Mater.* 2011, 23, 3847–3852. [CrossRef]

- 20. Guan, W.; Long, S.; Liu, Q.; Liu, M.; Wang, W. Nonpolar Nonvolatile Resistive Switching in Cu Doped ZrO<sub>2</sub>. *IEEE Electron Device Lett.* **2008**, 29, 434–437. [CrossRef]

- 21. Kim, M.; Choi, K.C. Transparent and flexible resistive random access memory based on Al<sub>2</sub>O<sub>3</sub> film with multilayer electrodes. *IEEE Trans. Electron Devices* **2017**, *64*, 3508–3510. [CrossRef]

- 22. Yoon, K.J.; Kim, G.H.; Yoo, S.; Bae, W.; Yoon, J.H.; Park, T.H.; Kwon, D.E.; Kwon, Y.J.; Kim, H.J.; Kim, Y.M.; et al. Double-Layer-Stacked One Diode-One Resistive Switching Memory Cross-point Array with an Extremely High Rectification Ratio of 10<sup>9</sup>. *Adv. Electron. Mater.* **2017**, *3*, 1700152. [CrossRef]

- 23. Sawa, A. Resistive switching in transition metal oxides. Mater. Today 2008, 11, 28–36. [CrossRef]

- 24. Kim, H.-D.; An, H.-M.; Lee, E.B.; Kim, T.G. Stable Bipolar Resistive Switching Characteristics and Resistive Switching Mechanisms Observed in Aluminum Nitride-based ReRAM Devices. *IEEE Trans. Electron Devices* **2011**, *58*, 3566–3573. [CrossRef]

- Kim, H.-D.; Yun, M.J.; Hong, S.M.; Kim, T.G. Size-dependent resistive switching properties of the active region in nickel nitride-based crossbar array resistive random access memory. *J. Nanosci. Nanotechnol.* 2014, 14, 9088–9091. [CrossRef]

- 26. Constantoudis, V.; Gogolides, E.; Patsis, G.P. Sidewall roughness in nanolithography: Origins, metrology and device effects, Nanolithography. In *The Art of Fabricating Nanoelectronic and Nanophotonic Devices and Systems*; Feldman, M.E., Ed.; Woodhead publishing: Cambridge, UK, 2013; pp. 503–537.

- 27. Xiong, S.; Bokor, J. A Simulation Study of Gate Line Edge Roughness Effects on Doping Profiles of Short-Channel MOSFET Devices. *IEEE Trans. Electron Devices* **2004**, *51*, 228–232. [CrossRef]

- Shibata, K.; Izumi, N.; Tsujita, K. Influence of line-edge roughness on MOSFET devices with sub-50-nm gates. Microlithography 2004, 5375, 865–873. [CrossRef]

- Kaya, S.; Brown, A.R.; Asenov, A.; Magot, D.; LintonI, T. Analysis of Statistical Fluctuations due to Line Edge Roughness in sub-0.1µm MOSFETs. In *Simulation of Semiconductor Processes and Devices 2001*; Springer Science and Business Media LL: Berlin, Germany, 2001; pp. 78–81.

- 30. Son, D.; Ko, K.; Woo, C.; Kang, M.; Shin, H. Line Edge Roughness and Process Variation Effect of Three Stacked Gate-All-Around Silicon MOSFET Devices. *J. Nanosci. Nanotechnol.* **2017**, *17*, 7130–7133. [CrossRef]

- 31. Baraveli, E.; Jurczak, M.; Speciale, N.; De Meyer, K.; Dixit, A. Impact of LER and Random Dopant Fluctuations on FinFET Matching Performance. *IEEE Trans. Nanotechnol.* **2008**, *7*, 291–298. [CrossRef]

- 32. Patel, K.; Liu, T.-J.K.; Spanos, C.J. Gate Line Edge Roughness Model for Estimation of FinFET Performance Variability. *IEEE Trans. Electron Devices* **2009**, *56*, 3055–3063. [CrossRef]

- Constantoudis, V.; Papavieros, G.; Gogolides, E.; Pret, A.V.; Pathangi, H.; Gronheid, R. Challenges in line edge roughness metrology in directed self-assembly lithography: placement errors and cross-line correlations. *J. Micro/Nanolithogr. MEMS MOEMS* 2017, *16*, 24001. [CrossRef]

- 34. Constantoudis, V.; Gogolides, E.; Roberts, J.; Stowers, J.K. Characterization and modeling of line width roughness (LWR). *Microlithography* **2005**, *5752*, 1227–1237.

- 35. Mack, C.A. Generating random rough edges, surfaces, and volumes. *Appl. Opt.* **2013**, *52*, 1472–1480. [CrossRef] [PubMed]

- 36. Constantoudis, V.; Patsis, G.P.; Leunissen, L.H.A.; Gogolides, E. Line edge roughness and critical dimension variation: Fractal characterization and comparison using model functions. *J. Vac. Sci. Technol. B Microelectron. Nanometer Struct.* **2004**, 22, 1974. [CrossRef]

- 37. Constantoudis, V.; Kokkoris, G.; Gogolides, E.; Pargon, E.; Martin, M. Effects of resist sidewall morphology on line-edge roughness reduction and transfer during etching: is the resist sidewall after development isotropic or anisotropic? *J. Micro/Nanolithogr. MEMS MOEMS* **2010**, *9*, 41209. [CrossRef]

- 38. Palasantzas, G.; Krim, J. Effect of the form of the height-height correlation function on diffuse x-ray scattering from a self-affine surface. *Phys. Rev. B* **1993**, *48*, 2873–2877. [CrossRef]

- 2013 ITRS-International Technology Roadmap for Semiconductors. Available online: http://www.itrs2.net/ 2013-itrs.html (accessed on 10 December 2017).

- 40. Papavieros, G.; Constantoudis, V. Line edge roughness measurement through SEM images: Effects of image digitization and their mitigation. *Proc. SPIE* **2017**, *10446*. [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).