# Article Mathematical Modeling and Analysis of Capacitor Voltage Balancing for Power Converters with Fewer Switches

Mamdouh L. Alghaythi <sup>1,\*</sup>, Gerald Christopher Raj Irudayaraj <sup>2</sup>, Senthil Kumar Ramu <sup>3,\*</sup>, Praveenraj Govindaraj <sup>2</sup> and Indragandhi Vairavasundaram <sup>4</sup>

- <sup>1</sup> Department of Electrical Engineering, College of Engineering, Jouf University, Sakaka 72388, Saudi Arabia

- <sup>2</sup> Department of Electrical and Electronics Engineering, PSNA College of Engineering and Technology,

- Dindigul 624622, Tamilnadu, India; gerald@psnacet.edu.in (G.C.R.I.); praveenrajmw@psnacet.edu.in (P.G.)

- <sup>3</sup> School of Electrical Engineering, Vellore Institute of Technology, Chennai 600127, Tamilnadu, India 4 School of Electrical Engineering, Vellore Institute of Technology, Vellore 620014, Tamilnadu, India

- School of Electrical Engineering, Vellore Institute of Technology, Vellore 632014, Tamilnadu, India; indragandhi.v@vit.ac.in

- \* Correspondence: mlalghaythi@ju.edu.sa (M.L.A.); senthilkumar.ramu@vit.ac.in (S.K.R.)

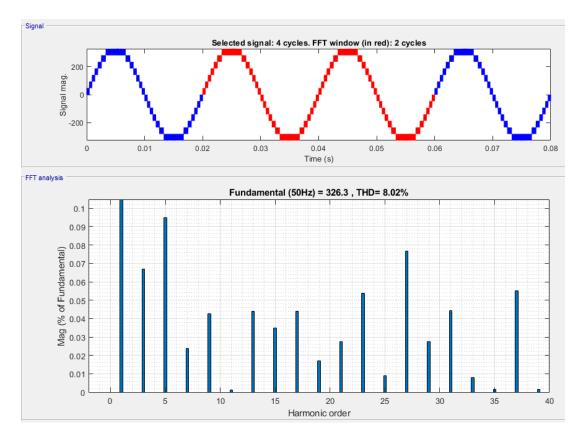

**Abstract:** The multilevel inverter (MLI) has been developed as a powerful power conversion scheme for several processes, including renewable energy, transmission systems, and electric drives. It has become popular across medium- to high-power operations due to its many advantages, including minimum harmonic content, low switching losses, and reduced electromagnetic interference (EMI). In this paper, the capacitor voltage balancing technique-based pulse width modulation (PWM) has been proposed. The proposed PWM strategy offers several advantages, such as high-quality output waveforms with reduced harmonic distortion, improved efficiency, and better control over the output voltage. The Xilinx ISE 10.1 software was used for synthesizing, and the VHDL code was written for the proposed method. MATLAB software was used to simulate and hardware was used to verify the proposed system. The SPARTAN 3E FPGA was used for the generation of the PWM. This paper developed a 2 kW single-phase 15-level inverter that created an AC wave from the DC input voltage, with a total harmonic distortion (THD) of 8.02%, which was less than the THD achieved from other conventional MLI. The results indicate that MLI topologies with low total harmonic currents, fewer switches, and higher output voltage levels are better stabilized during load disturbance circumstances.

Keywords: renewable energy; power converter; total harmonic distortion; modeling; capacitor voltage

## 1. Introduction

Global warming is a major environmental issue affecting the entire world. It refers to the gradual increase in the Earth's average surface temperature caused by the buildup of greenhouse gases in the atmosphere. The primary cause of global warming is human activity, particularly burning fossil fuels for energy and transportation, deforestation, and industrial processes. The impacts of global warming are far-reaching and can be felt worldwide [1,2]. Reducing greenhouse gas emissions is the most efficient approach to address global warming. It can be achieved through various strategies, such as transitioning to clean and renewable energy sources, improving energy efficiency, promoting public transportation, and implementing policies to reduce emissions from industries and agriculture [3].

A solar PV system converts sunlight into electricity using solar panels. Solar PV systems are becoming increasingly popular as a clean and sustainable alternative to traditional energy sources. A typical solar PV system consists of solar panels, an inverter, and a battery bank (optional). Solar panels consist of photovoltaic cells that convert sunlight into DC. An inverter converts the DC to AC, which powers household appliances and electronics. This output is influenced by solar radiation and temperature and is not steady [4,5]. Therefore,

Citation: Alghaythi, M.L.; Irudayaraj, G.C.R.; Ramu, S.K.; Govindaraj, P.; Vairavasundaram, I. Mathematical Modeling and Analysis of Capacitor Voltage Balancing for Power Converters with Fewer Switches. *Sustainability* **2023**, *15*, 10698. https://doi.org/10.3390/ su151310698

Academic Editor: Jaime W. Zapata

Received: 1 May 2023 Revised: 21 June 2023 Accepted: 29 June 2023 Published: 7 July 2023

**Copyright:** © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). it is important to obtain the most power possible out of solar PV, which is achieved by maximum power point tracking (MPPT) [6], for a PV panel to operate effectively even under numerous climatic changes throughout an annual calculation [7].

The use of an MPPT controller with this DC-to-DC converter offers several benefits. By ensuring that the solar panels operate at their maximum efficiency, the system can generate more energy, reducing the size of the solar panel array required to meet energy demands. Using a DC-to-DC converter also improves the system's efficiency by reducing losses in the power conversion process. It can lead to a more cost-effective and reliable solar PV system.

Since they have been around for over 50 years, multilevel inverters (MLIs) are gaining popularity in industrial settings as one of the fascinating ways to deploy medium- to high-power converters. Multilevel inverters are an important technology in power electronics that have gained significant attention in recent years due to their potential to provide high voltage and power quality to various applications. A multilevel inverter consists of several power electronic switches arranged in a specific configuration to produce multiple output voltage levels. The configuration for MLI depends on the number of levels and clamping used to achieve these levels.

An analytical indication for improving the quality of the alternating voltage is provided by MLI topologies [8]. Over traditional two-level inverters, MLIs offer several benefits, including a greater basic voltage at the output, reduced typical mode voltage and switch loss, less EMI, and less THD. Power electronic applications are crucial for the multilayer inverter to convert a direct current source. Several issues exist with the three-phase alternating machine and system supply PWM signaling approaches [9]. Since low-level inverters contain nonlinear elements such as MOSFET and IGBT, they may also produce waveforms with harmonics using pulse-width modulation (PWM) [10]. Nonlinear impacts such as distortion caused by harmonics develop on the outputs of load when the amount of the element has risen on the inverter. Studies have considered nonlinear impacts to reduce the impact of harmonic distortion on the operating loads of PWM inverters [11].

The cascaded H-bridge MLI consists of a succession of H-bridge inverters connected in a cascaded configuration. Each H-bridge inverter has four switches (upper arm = 2 and lower arm = 2) that switch the voltage to produce the needed DC output voltage waveform. The number of levels for the inverter is determined by the number of H-bridge modules used [12]. Increasing the DC-link voltage results in greater electromagnetic interference and voltage stress on power semiconductor devices [13]. Topologies that employ multiple levels of inverters can decrease the voltage stress of switches and EMI in the system, thus replacing the two-level inverter [14]. The cascaded H-bridge MLI offers various benefits over conventional inverters, including reduced harmonic distortion, improved voltage quality, lower EMI, higher efficiency, and a modular design. These advantages make it well suited for various applications such as renewable energy systems, motor drives, and electric vehicles.

PWM technology removes and lowers harmonics at the inverter output while controlling the output voltage. PWM serves the dual purpose of reducing or eliminating harmonics and controlling the voltage inside the inverter without an additional hardware price. With developments in MLIs, innovative modulation methods are increasingly necessary for these devices. Each modulation approach has negative and positive influences on the converter architecture and scope. The categorization of the modulation schemes for MLIs based on the difference between high- and low-frequency shifting is represented in [15]. Level shifting and phase shifting modulation schemes are two categories of PWM systems based on the waveform. To create high-quality output voltage waveforms, level shift modulated methods are commonly used in many applications [16,17].

Capacitor voltage balance (CVB) represents one of the most important problems for MLIs due to the modular design. The two primary forms of capacitor-voltage-balancing methods are arm regulation [18] and specific capacitor regulation [19]. The first approach, which necessitates a closed-loop regulation for each capacitor, must be revised for MMCs with many capacitors. The latter is the sorting and selection (SAS) approach and uses all

the capacitors in an arm. It sorts the capacitor voltages and chooses included or skipped sub-modules (SMs) by the signal of the arm current.

This PWM scheme provides periodic unneeded activation of the switches and supplies to turn up the initial level while producing a high-level voltage. The additional supply and switch action reduces the switch's lifetime and results in power loss. A new fraction sinus PWM improvement with a gap is presented in [20] on a three-phase signal processing approach. The dual DC to DC converter featuring a reverse connection for the MLI is suggested [21]. Ref. [22] discusses investigating the primary PWM operation instances and frequencies that influence this zero-crossing point.

An MLI with the fewest possible power electronic switching elements was proposed in this study. It used a multilayer inverter created in [23,24] and modified somewhat. By utilizing the inverter's series/parallel switches, the proposed MLI introduced an auxiliary network with four diodes and a toggle switch. In contrast to the traditional cascaded Hbridge inverters, just two independent source voltages were required to generate an equal number of voltage levels. Compared with existing techniques, the proposed inverter used fewer switching elements and had lower harmonics in the output voltage waveforms. The applicability of grid-tied photovoltaic systems, hybrid electric cars, etc., could be expanded using the proposed MLI design. In this proposed system, the RL load was considered from the inverter with the values of 100  $\Omega$  and 30 mH, respectively, for 11 and 15 levels of the inverter. In addition, the bottom and top inverter voltages for 11 levels were 65 V and 130 V, and those for 15 levels were 47 V and 94 V. Mathematical analyses, computer simulations, and experimental findings are provided to prove the proposed cascaded MLI's viability.

The field programmable gate arrays (FPGAs) used to implement various PWM regulators have grown progressively over the past few years. Because of their flexibility compared with other digital signal processors (DSPs), they are becoming the leading devices for employing various PWMs.

The main objective of this paper is to develop a CVB-based PWM technique for 11and 15-level inverters. This investigation offers a new MLI design that uses two DC sources and eight power electronic components to generate 11 and 15 levels. Based on the measured findings, the proposed MLI offers high-quality, consistent output waveforms with a decreased THD. In hardware, PWM generation was carried out using SPARTAN 3 A FPGA kit.

The paper's structure is as follows: Section 2 presents the cascaded H-bridge MLI that is being proposed. Section 3 discusses the problems with the proposed inverter's capacitor voltage balancing. Section 4 illustrates the PWM pulse modeling for the proposed cascaded MLI. In Section 5, the outcomes of the proposed system are analyzed. Furthermore, Section 6 provides an overview of the conclusions drawn from this paper.

### 2. Proposed Cascaded H-Bridge MLI

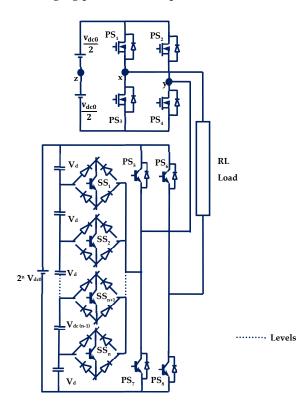

The proposed inverter had a top and bottom inverter in which the top inverter's primary switches were triggered with high frequency, while the bottom inverter was triggered with low frequency, as shown in Figure 1. The top three-level inverter had four switches with output levels of 0,  $+V_{dc}$ , and  $-V_{dc}$ . The bottom inverter had four basic primary switches and a second bidirectional switch, which could be increased to increase the overall level of the inverter.

#### 2.1. Modes of Operation

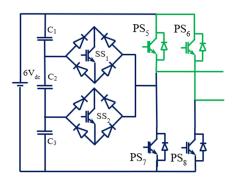

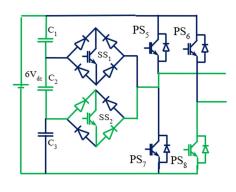

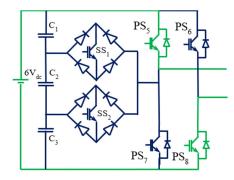

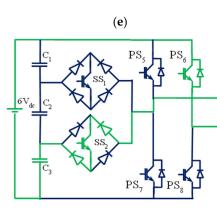

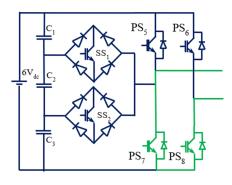

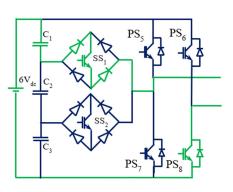

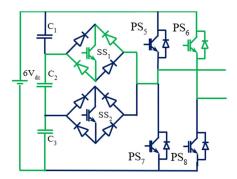

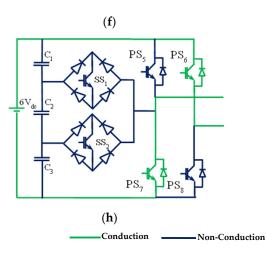

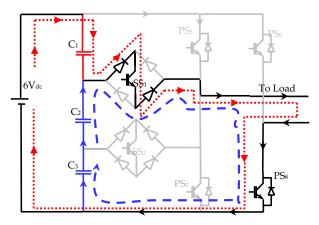

Figure 2 illustrates the suggested bottom inverter's operating modes, comprising four IGBT switches and two bidirectional switches. The green color indicates the conduction of switches and capacitors [25].

Switching mode 1, depicted in Figure 2a, involved turning on switches  $PS_5$  and  $PS_6$  while turning off the remaining switches. This configuration produced a voltage output of 0 [26].

The system had seven different switching modes.

In switching mode 1, switches  $PS_5$  and  $PS_6$  were on, while the others were off, producing a voltage of 0 (Figure 2a).

In switching mode 1, switches  $PS_7$  and  $PS_8$  were on, while the others were off, producing a voltage of 0 (Figure 2b).

Switching mode 2 involved switches  $PS_8$  and  $SS_2$  being on and the others being off, resulting in a voltage of 2  $V_{dc0}$  (Figure 2c).

Switching mode 3 entailed turning on switches  $PS_8$  and  $SS_1$  while keeping the others off, generating a voltage of 4  $V_{dc0}$  (Figure 2d).

In switching mode 4, switches  $PS_5$  and  $PS_8$  were on, and the rest were off, yielding a voltage of 6  $V_{dc0}$  (Figure 2e).

In switching mode 5, switches  $PS_6$  and  $SS_1$  were on, while the others were off, producing a voltage of  $-2 V_{dc0}$  (Figure 2f).

Switching mode 6 involved switches  $PS_6$  and  $SS_2$  being on and the others being off, resulting in a voltage of  $-4 V_{dc0}$  (Figure 2g).

Finally, in switching mode 7, switches  $PS_6$  and  $PS_7$  were on, while the rest were off, generating a voltage of  $-6 V_{dc0}$  (Figure 2h).

The various modes of operation of the proposed MLI are represented in Figure 2. The switching modes of the H-bridge inverter are illustrated in Table 1. It describes various active and non-active modes of IGBT switches.

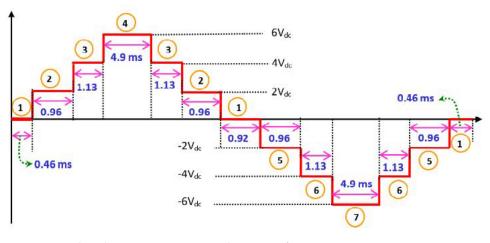

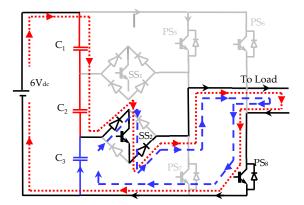

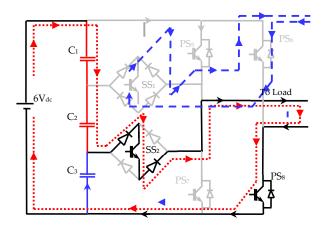

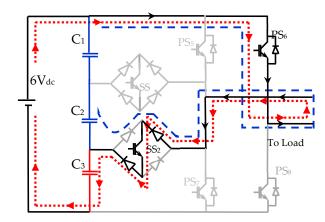

To maintain a frequency of 50 Hz over a total period of 0.02 s, Figure 3 displays the projected seven-stage output of the suggested bottom inverter. Figures 4–7 display the direction of current flow during the charging and discharging cycles of capacitors  $C_1$ ,  $C_2$ , and  $C_3$ . The dotted line indicates the charging phase, while the dashed line represents the discharging phase of the capacitors [26,27].

Figure 1. Proposed cascaded H-bridge multilevel inverter.

(**g**)

(**d**)

Figure 2. Mode of operation.

| Switching<br>Mode | PS5 | PS6 | PS7 | PS8 | SS1 | <b>SS2</b> | Voltage<br>Obtained | Reference |

|-------------------|-----|-----|-----|-----|-----|------------|---------------------|-----------|

|                   | 1   | 1   | ×   | ×   | ×   | ×          | 0                   | Figure 2a |

| 1 –               | ×   | *   | 1   | 1   | ×   | ×          | 0                   | Figure 2b |

| 2                 | ×   | ×   | ×   | 1   | ×   | 1          | 2 V <sub>dc0</sub>  | Figure 2c |

| 3                 | ×   | ×   | ×   | 1   | 1   | ×          | 4 V <sub>dc0</sub>  | Figure 2d |

| 4                 | 1   | ×   | ×   | 1   | ×   | *          | 6 V <sub>dc0</sub>  | Figure 2e |

| 5                 | ×   | 1   | ×   | ×   | ✓   | *          | $-2 V_{dc0}$        | Figure 2f |

| 6                 | ×   | 1   | ×   | ×   | ×   | 1          | $-4 V_{dc0}$        | Figure 2g |

| 7                 | ×   | 1   | 1   | *   | ×   | *          | $-6 V_{dc0}$        | Figure 2h |

Table 1. Switching modes of bottom H-bridge inverter.

Figure 3. Predicted seven-stage output voltage waveform.

Figure 4. Direction of current flow path during mode 2 ( ••••• Charging, ••••• Discharging).

## 2.2. Capacitor States of Bottom H Bridge Inverter

During mode 2, capacitors  $C_1$  and  $C_2$  were charged, and capacitors  $C_3$  discharged. Similarly, in mode 3, capacitor  $C_1$  charged, while capacitors  $C_2$  and  $C_3$  discharged, as depicted in Figure 5. During mode 5, capacitor  $C_1$  discharged, whereas capacitors  $C_2$  and  $C_3$  charged.

Likewise, during mode 6,  $C_1$  and  $C_2$  discharged, whereas  $C_3$  charged. Table 2 provides a detailed account of each capacitor's charging and discharging duration [28].

Figure 5. Direction of current flow path during mode 3 ( ----- Charging, ----- Discharging).

Figure 6. Direction of current flow path during mode 5 ( ----- Charging, ----- Discharging).

Figure 7. Direction of current flow path during mode 6 ( ----- Charging, ----- Discharging).

From Table 2, it is concluded that

- C<sub>1</sub> and C<sub>3</sub> total charging time = 4.18 milli seconds;

- C<sub>1</sub> and C<sub>3</sub> total discharging time = 4.18 milli seconds;

- C<sub>2</sub> total charging time = 3.84 milli seconds;

- C<sub>2</sub> total discharging time = 4.52 milli seconds.

The capacitor charging and discharging times should typically be equal to be balanced. According to the information above, capacitors  $C_1$  and  $C_3$  had equal charging and discharging times for cycles of 20 ms and were, therefore, balanced. However, capacitor  $C_2$  did not have an equal charging and discharging time and needed to be balanced. So, the solution

Status of Capacitors Switching Time  $PS_5$  $PS_6$  $PS_7$ PS<sub>8</sub>  $SS_1$  $SS_2$ Mode Duration  $C_1$  $C_3$  $C_2$ UC UC UC 1 1 × × ≍ × 1.84 ms 1 UC UC UC × × 1 1 × × 2 × 1 1 × × × ↑  $\uparrow$  $\downarrow$ 1.92 ms × × 1 1  $\downarrow$  $\downarrow$ 2.26 ms 3 ≍ ≍ ↑ 1 UC 4 × × 1 ≍ × UC UC 4.9 ms 5 × 1 × ≍ 1 ≍  $\downarrow$  $\uparrow$ ↑ 1.92 ms 6 × 1 × × × 1  $\downarrow$  $\downarrow$ ↑ 2.26 ms 7 1 UC UC UC 4.9 ms × 1 × × × X—OFF I ✓—ON I UC—Unchanged 20 ms

Table 2. Capacitor charging and discharging status of capacitors.

inverter's charging and discharging duration [28].

#### 3. Capacitor Voltage Balancing in the Proposed Inverter

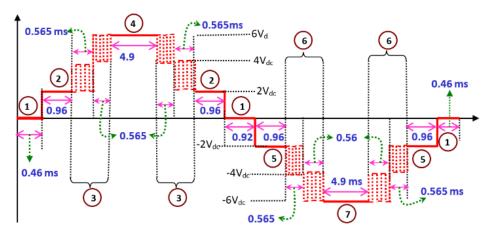

The seven-level inverter was proposed to eliminate the capacitor voltage balancing problem in capacitor  $C_2$ . Thus, the total voltage in the capacitor over 20 ms became positive [16]. It could be implemented during modes 3 and 6, where the capacitor  $C_2$  voltage decreased. Figure 8 shows the proposed capacitor voltage balancing technique, a modified switching technique. During switching stages 3 and 5, it was apparent that the proposed inverter voltage may switch among two levels.

for this problem, the capacitor balancing process, was required in this proposed seven-level

Figure 8. Proposed modified switching technique cascading top and bottom inverter.

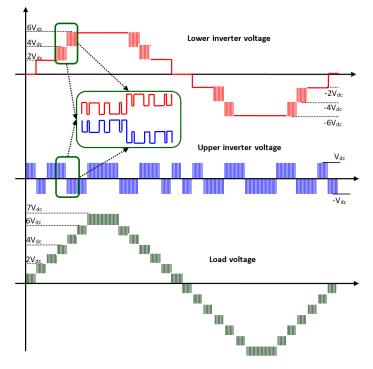

During mode 3, the inverter voltage was shifted among 2 V<sub>dc</sub> and 4 V<sub>dc</sub> for the first part of the time interval and among 4 V<sub>dc</sub> and 6 V<sub>dc</sub> during the next part of the time interval. This reduced the discharging time of C<sub>2</sub> in mode 3. Because of this switching, the voltage was either in 2 V<sub>dc</sub> or 6 V<sub>dc</sub>, increasing the charging time of capacitor C<sub>2</sub>. The cascaded output of the top- and bottom-level inverter is shown in Figure 9. The low switching frequency inverter (LSFI) and high switching frequency inverter (HSFI) voltages were immediately coupled to produce the load voltage. It can also be seen in Figure 9 (the magnified area) that at switching state 3 of the lower inverter, the HSFI should flip in the opposite direction of the LSFI. This was critical for switching the load voltage among 4 V<sub>dc</sub> and 5 V<sub>dc</sub>, as well as 5 V<sub>dc</sub> and 6 V<sub>dc</sub>. C<sub>2</sub> will begin charging in addition to C<sub>1</sub> and C<sub>3</sub> if the changed switching architecture powers the proposed inverter. As a result, the voltage over  $C_2$  must be monitored, and depending on its current value, either the generalized reduced switching method or the altered modulation strategy must be employed.

Figure 9. Top and bottom voltage waveforms and cascaded output by using modified switching technique.

## 4. Modeling of PWM Pulses for Proposed Cascaded Multilevel Inverter

To produce the reference waveform for the top inverter, the following Equations (1) and (2) were utilized [17]:

$$U_{ref} = A\sin(\omega t) \tag{1}$$

$$U_{ref,s} = \frac{U_{ref}}{7} \tag{2}$$

$$Z_1 = \begin{cases} 1 & \text{if } U_{ref} > 0\\ 0 & \text{if } U_{ref} < 0 \end{cases}$$

(3)

$$V_{bottom,expected} = \left( round \left( \frac{|U_{ref,s}|}{0.4} \right) * 0.4 * Z_1 \right) + \left( round \left( \frac{|U_{ref,s}|}{-0.4} \right) * 0.4 * Z_1 \right)$$

(4)

$$V_{top,ref} = 7 * \left( U_{ref,s} - V_{bottom,expected} \right)$$

<sup>(5)</sup>

Equation (3) describes the zero-crossing detector, while Equation (4) represents the projected output of the bottom inverter ( $V_{bottom}$ ). Equation (5) provides a mathematical expression for the reference waveform of the top inverter. The following equations must construct and describe the reference waveform to provide the PWM for the bottom inverter:

$$V_{bottom,ref} = round\left(\frac{\left|U_{ref,S}\right|}{0.4}\right) \tag{6}$$

After generating the reference waveform, it was divided into various waves Ry.

$$X = \frac{(N-11)}{4} + 2 \tag{7}$$

$$R_{y} = \begin{cases} 1 & \text{if } U_{bottom,ref} > y \\ 0 & \text{if } U_{bottom,ref} < y \end{cases}$$

(8)

The total number of secondary switches required for an *N*-level inverter was determined after dividing by the number of different signals.

$$NAS = \frac{(N-11)}{4} + 12 \tag{9}$$

where *N* = 11, 15, 19, 23 . . .

The turn-on and turn-off operation of the primary switches (*PSs*) of the bottom inverter was determined by the following equations:

$$PS_5(t) = \left[\overline{\mathbf{R}_1} + \overline{\mathbf{R}_y}\right] * (Z_1) \tag{10}$$

$$PS_6(t) = \left[\mathbf{R}_1 + \overline{Z_1}\right] + \left[\overline{\mathbf{R}_1} * Z_1\right]$$

(11)

$$PS_7(t) = \left[\overline{\mathbf{R}_1} + \mathbf{R}_y\right] * Z_1 \tag{12}$$

$$PS_8(t) = [\mathbf{R}_1 + Z_1] + [\overline{\mathbf{R}_1} * \overline{Z_1}]$$

(13)

where y = X, + stands for logical OR, and \* stands for multiplication. The following expression determines how the bottom inverter's secondary switches operate when they are turned on and off:

Step 1. Form a set:

$$\mathbf{R} = \begin{bmatrix} \mathbf{R}_{1,1} \mathbf{R}_{2,1} \mathbf{R}_{3,1} \mathbf{R}_{4,1} \dots \mathbf{R}_{y-3,1} \mathbf{R}_{y-2,1} \mathbf{R}_{y-1,1} & \mathbf{R}_{y} \end{bmatrix}$$

(14)

Step 2. Write the permutation P on R :

$$P = \begin{bmatrix} R_1 & R_2 & R_3 & \dots & R_{y-2} & R_{y-1} & R_y \\ R_2 & R_3 & R_4 & \dots & R_{y-1} & R_y & R_1 \end{bmatrix}$$

(15)

Step 3. Eliminate the final column in the above permutation  $P_1$  and rework as

$$P_{1} = \begin{bmatrix} R_{1} & R_{2} & R_{3} & \dots & R_{y-3} & R_{y-2} & R_{y-1} \\ R_{2} & R_{3} & R_{4} & \dots & R_{y-2} & R_{y-1} & R_{1} \end{bmatrix}$$

(16)

Step 4. We can develop the switching signals for the secondary switches calculated from the above equation. The first and last columns of the matrix are responsible for establishing the switching patterns for the initial and final secondary switches, respectively. The equations for  $SS_1$  and  $SS_n$  are also included.

$$SS_1(t) = \left( (\mathbf{R}_1 \oplus \mathbf{R}_2) * \overline{Z_1} \right) + \left( \left( \mathbf{R}_{y-1} \oplus \mathbf{R}_y \right) * Z_1 \right)$$

(17)

$$SS_n(t) = \left( (\mathbf{R}_1 \oplus \mathbf{R}_2) * Z_1 \right) + \left( \left( \mathbf{R}_{y-1} \oplus \mathbf{R}_y \right) * \overline{Z_1} \right)$$

(18)

where the XOR (exclusive OR) operation is represented as  $\oplus$ . In a similar manner, the second column of the permutation matrix  $P_1$  was used to generate the switching patterns for  $SS_2$ , while the second column from the end was used for  $SS_{(n-1)}$ . The expressions were as follows:

$$SS_2(t) = ((\mathbf{R}_2 \oplus \mathbf{R}_3) * Z_1) + ((\mathbf{R}_{y-2} \oplus \mathbf{R}_{y-1}) * Z_1)$$

(19)

$$SS_{n-1}(t) = ((\mathbf{R}_2 \oplus \mathbf{R}_3) * Z_1) + ((\mathbf{R}_{y-2} \oplus \mathbf{R}_{y-1}) * \overline{Z_1})$$

(20)

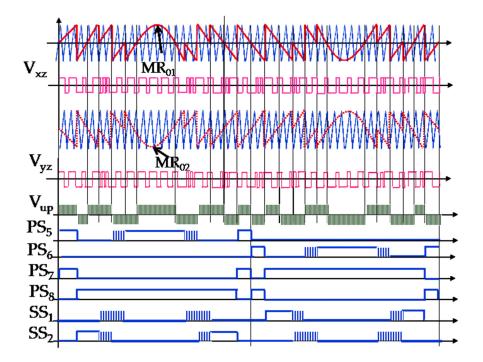

The switching states and expected output of the proposed fifteen-level inverter are represented in Table 3. It shows the top and bottom H-bridge switches in an active and non-active mode. The primary switches  $PS_1$  and  $PS_3$  were turned on and off by comparing the

MR01 reference waveform with the triangular carrier wave, and  $PS_2$  and  $PS_4$  were turned on and off by comparing the MR02 reference waveform with the triangular carrier wave, as shown in Figure 10. The resulting voltage Vyz was obtained from the waveform. The primary switches of the lower inverter from  $PS_5$  to  $PS_8$  were turned on and off concerning Equations (10)–(13), and the secondary switches  $SS_1$  and  $SS_1$  were turned on and off regarding Equations (17)–(19) as represented in the switching signals.

| Tar             | Top H Bridge Switches Bottom H Bridge Switches |                 |                 |                 |                 | Output Load Voltage |                 |        |        |      |                                                                                                                                                 |                                 |                                       |

|-----------------|------------------------------------------------|-----------------|-----------------|-----------------|-----------------|---------------------|-----------------|--------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------|

| төр             | n bria                                         | ge Swit         | cnes            | DU              | ittom r         | 1 Driu              | ige Sv          | vitche | 5      | Mode | $\mathbf{V}_{dc1} = \mathbf{V}_{dc2} = \mathbf{V}_{dc3} = 2\mathbf{V}_{dc0} \ i.e., \left[\frac{\mathbf{V}_{dcn}}{\mathbf{V}_{dc0}} = 2\right]$ |                                 |                                       |

| PS <sub>1</sub> | PS <sub>2</sub>                                | PS <sub>3</sub> | PS <sub>4</sub> | PS <sub>5</sub> | PS <sub>6</sub> | PS <sub>7</sub>     | PS <sub>8</sub> | $SS_1$ | $SS_2$ |      | V <sub>top</sub>                                                                                                                                | V <sub>bottom</sub>             | $V_{total} = V_{top} + V_{bottom}$    |

| 1               | ×                                              | ×               | 1               | ✓               | ×               | ×                   | 1               | ×      | ×      | Ι    | $0 \leftrightarrow V_{dc0}$                                                                                                                     | 6 V <sub>dc0</sub>              | $6V_{dc0} \leftrightarrow 7V_{dc0}$   |

| ×               | 1                                              | 1               | ×               | ✓               | ×               | ×                   | 1               | ×      | ×      | II   | $-V_{dc0}\leftrightarrow 0$                                                                                                                     | 6 V <sub>dc0</sub>              | $5V_{dc0} \leftrightarrow 6V_{dc0}$   |

| 1               | ×                                              | ×               | 1               | ×               | ×               | ×                   | 1               | 1      | ×      | III  | $0 \leftrightarrow -V_{dc0}$                                                                                                                    | $4V_{dc0} \leftrightarrow 6V_d$ | $4V_{dc0} \leftrightarrow 5V_{dc0}$   |

| ×               | 1                                              | 1               | ×               | ×               | ×               | ×                   | 1               | 1      | ×      | IV   | $V_{dc0} \leftrightarrow 0$                                                                                                                     | $2V_{dc0}\leftrightarrow 4V_d$  | $3V_{dc0} \leftrightarrow 4V_{dc0}$   |

| 1               | ×                                              | ×               | 1               | ×               | ×               | ×                   | 1               | ×      | 1      | V    | $0 \leftrightarrow V_{dc0}$                                                                                                                     | 2 V <sub>dc0</sub>              | $2V_{dc0} \leftrightarrow 3V_{dc0}$   |

| ×               | 1                                              | 1               | ×               | ×               | ×               | ×                   | 1               | ×      | 1      | VI   | $-V_{dc0} \leftrightarrow 0$                                                                                                                    | 2 V <sub>dc0</sub>              | $V_{dc0}\leftrightarrow 2V_{dc0}$     |

| 1               | ×                                              | ×               | 1               | ✓               | 1               | ×                   | ×               | ×      | ×      | VII  | $0 \leftrightarrow V_{dc0}$                                                                                                                     | 0                               | $0 \leftrightarrow V_{dc0}$           |

| ×               | 1                                              | 1               | ×               | ×               | ×               | 1                   | 1               | ×      | ×      | VIII | $0\leftrightarrow -V_{dc0}$                                                                                                                     | 0                               | $0\leftrightarrow -V_{dc0}$           |

| 1               | ×                                              | ×               | 1               | ×               | 1               | ×                   | ×               | 1      | ×      | IX   | $V_{dc0} \leftrightarrow 0$                                                                                                                     | $-2 V_{dc0}$                    | $-V_{dc0}\leftrightarrow -2V_{dc0}$   |

| ×               | 1                                              | 1               | ×               | ×               | 1               | ×                   | ×               | 1      | ×      | Х    | $0 \leftrightarrow -V_{dc0}$                                                                                                                    | $-2 V_{dc0}$                    | $-2V_{dc0} \leftrightarrow -3V_{dc0}$ |

| 1               | ×                                              | ×               | 1               | ×               | 1               | ×                   | ×               | ×      | 1      | XI   | $-V_{dc0} \leftrightarrow 0$                                                                                                                    | $-2V_{dc0}\leftrightarrow -$    | $-3V_{dc0}\leftrightarrow-4V_{dc0}$   |

| ×               | 1                                              | 1               | ×               | ×               | 1               | ×                   | ×               | ×      | 1      | XII  | $0 \leftrightarrow V_{dc0}$                                                                                                                     | $-4V_{dc0}\leftrightarrow -$    | $-4V_{dc0}\leftrightarrow-5V_{dc0}$   |

| 1               | ×                                              | ×               | 1               | ×               | 1               | 1                   | ×               | ×      | ×      | XIII | $V_{dc0} \leftrightarrow 0$                                                                                                                     | $-6 V_{dc0}$                    | $-5V_{dc0} \leftrightarrow -6V_{dc0}$ |

| ×               | 1                                              | 1               | ×               | ×               | 1               | 1                   | ×               | ×      | ×      | XIV  | $0\leftrightarrow -V_{dc0}$                                                                                                                     | $-6 V_{dc0}$                    | $-6V_{dc0} \leftrightarrow -7V_{dc0}$ |

| <b>*</b> –0     | FF   🗸 —                                       | ON              |                 |                 |                 |                     |                 |        |        |      |                                                                                                                                                 |                                 |                                       |

Table 3. Switching states and expected output of 15-level inverter.

Figure 10. Generated PWM switching signals for switches.

## 5. Results and Discussion

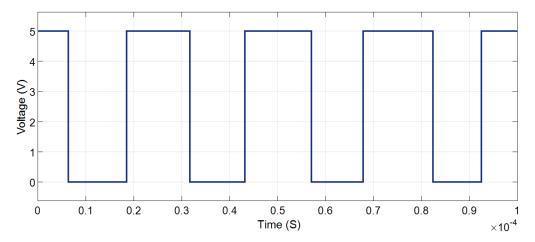

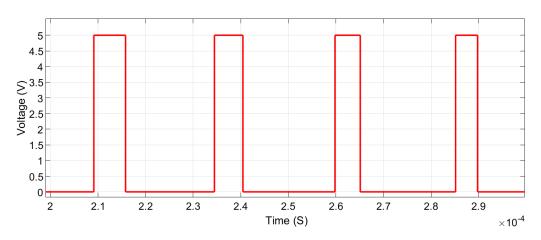

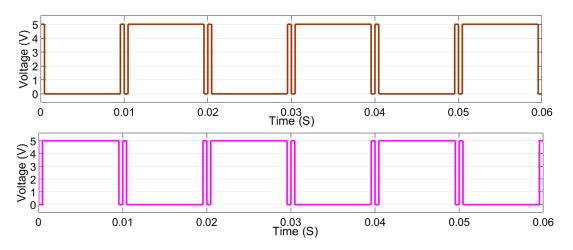

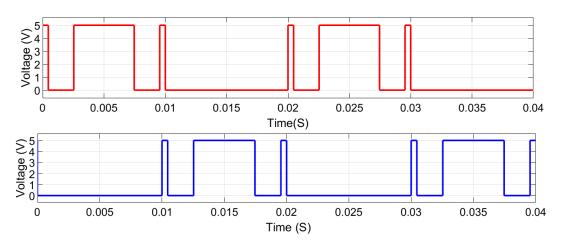

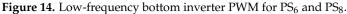

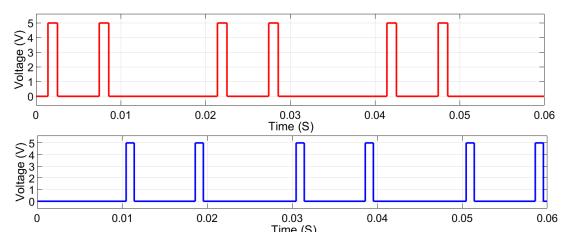

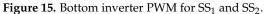

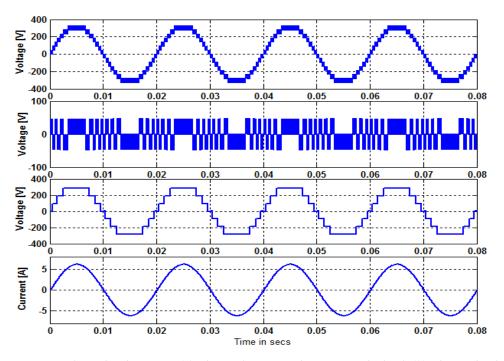

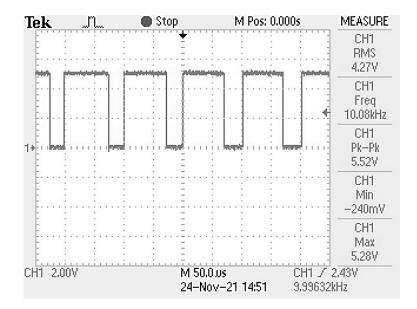

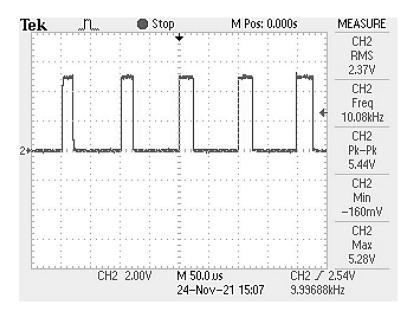

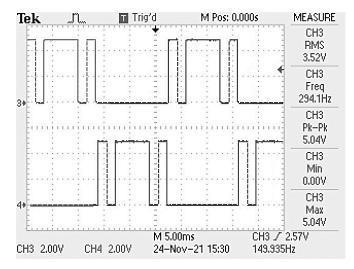

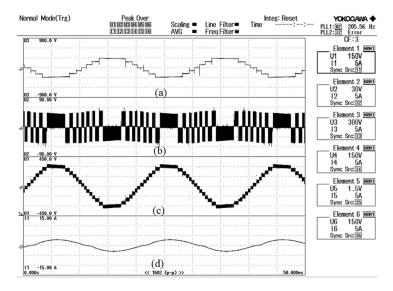

This section presents the simulation and experimental results of the proposed MLI. The simulation parameters used for the 15 levels are represented in Table 4. The simulation was conducted in MATLAB 2021a Simulink with a resistive load. Simulations were performed for the proposed inverter in MATLAB/Simulink to verify the inverter configuration. The simulations up to 15 levels used the algorithm outlined in Section 4, which could be expanded to every additional level needed. The setting up for both the simulation and the experiment was identical. Figures 11 and 12 illustrate the generated high-frequency PWM pulses for the top inverter primary switches PS1 to PS4. The bottom inverter was run at a low frequency, whereas the top inverter operated at a high switching rate identical to the carrier frequency (10 kHz). Figures 13 and 14 illustrate the generated low-frequency PWM pulses for the bottom inverter primary switches PS5 to PS8. Figure 15 illustrates the low-frequency PWM pulses generated for the bottom inverter secondary switches SS1 and SS2. The upper and lower inverter waveforms for a 15-level inverter and the final waveforms had a modulation index of 1. The output voltage levels fell as the quantity of "m" continued to decrease the resulting output voltage across the load, and the voltage output at the top inverter, the voltage output at the bottom inverter, and the load current waveform are displayed in Figure 16. The previously mentioned results were reached by assuming that each capacitor in the H-bridge inverter had its own independent DC source. Nevertheless, the generalized PWM switching approach and the improved modulation technique were employed to provide the proposed H-bridge inverter with one independent DC source.

Figure 11. High-frequency top inverter PWM for PS<sub>1</sub> and PS<sub>3</sub>.

**Figure 12.** High-frequency top inverter PWM for PS<sub>2</sub> and PS<sub>4</sub>.

Figure 13. Low-frequency bottom inverter PWM for PS<sub>5</sub> and PS<sub>7</sub>.

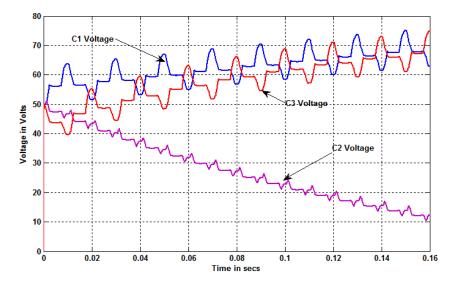

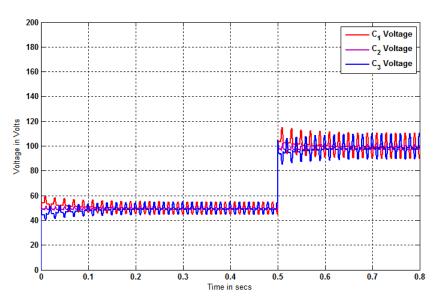

Figure 17 shows the output voltages at the capacitors without implementing the CVB approach. When using the generalized PWM method, it can be seen that although the  $C_1$  and  $C_{3'}$ s capacitor voltages continually charged,  $C_2$  drained continuously. Figure 18 shows the output voltages at the capacitors with the implementation of the CVB algorithm. It depicts the voltages across the proposed MLI's capacitors. At the same time, it was powered by an integrated conventional and improved switching approach, showing how closely spaced the capacitor voltages were to one another.

**Figure 16.** The 15-level inverter: (**a**) Obtained output voltage across the load. (**b**) Obtained voltage at the top inverter. (**c**) Obtained voltage at the bottom inverter. (**d**) Obtained load current waveform.

Figure 17. Capacitor voltage at the bottom inverter without balancing.

| Table 4. Simula | tion parameters. |

|-----------------|------------------|

|-----------------|------------------|

| PARAMETERS                                                             | LEVEL 11 | LEVEL 15 |  |  |  |

|------------------------------------------------------------------------|----------|----------|--|--|--|

| Top inverter voltage                                                   | 65 V     | 47 V     |  |  |  |

| Bottom inverter voltage                                                | 130 V    | 94 V     |  |  |  |

| Load resistance = $100 \Omega$ and load inductance = $30 \text{ mH}$ . |          |          |  |  |  |

Figure 18. Capacitor voltage at the bottom inverter with balancing.

### 6. Hardware Validation

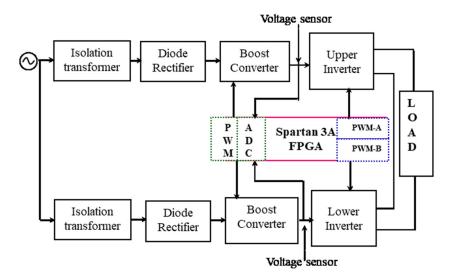

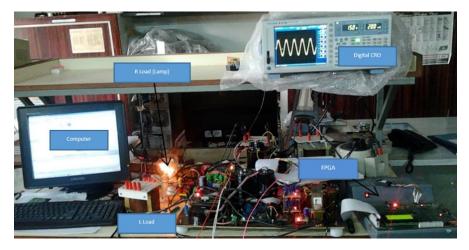

The proposed MLI was designed for a power of 2000 W with two asymmetrical DC input voltages of 47 V for the top inverter and 94 V  $\times$  3 for the bottom inverter, and the cascaded output voltage was obtained with equal discrete steps. Figure 19 depicts the block diagram of the hardware setup of the proposed converter. Figure 20 displays an image of the hardware configuration for the proposed d inverter with 15 levels constructed in the laboratory. The top and bottom inverters employed IGBTs from the MKI 80-06T6K series. A FIO50-12BD bidirectional secondary switch was employed in the bottom inverter. A SPARTAN 3A FPGA kit was used to create the gate-driving signal.

Figure 19. Hardware block setup of the proposed inverter.

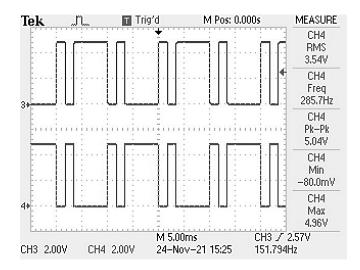

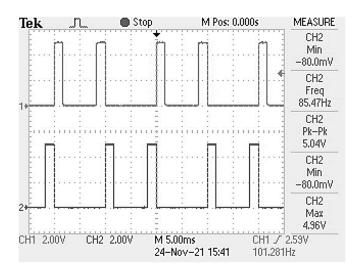

Figures 21 and 22 depict the experimental findings of a 15-level inverter for upper inverters (PS1, PS3, PS2, and PS4). The switching pulses were produced for the high frequency of the top inverters while operating using the CVB technique. The switching frequency was maintained as 9.996 KHz for the upper switches (1 Div = 2 V). Figures 23 and 24 depict the experimental results of the PWM waveform for the bottom inverters (PS5, PS7, PS6, and PS8). The switching voltages for the lower inverters were 5 V with (1 Div = 2 V). It showed that it maintained constant voltage while applying the lower switches with the help of CBV. The secondary switches' PWM waveforms are illustrated in Figure 25. It

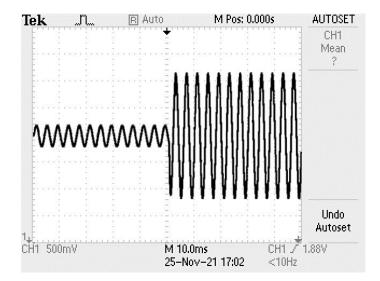

operated at a low frequency of 101.381 Hz (1 Div = 2 V). It showed that while applying the CVB algorithm, the auxiliary switches operated at a high frequency, and the remaining switches operated at a low frequency. The output voltage of the proposed inverter, while controlled by the CVB methodology, is shown in Figure 26. In addition to the load current waveform, it also displayed the high- and low-frequency inverter waveforms. It was seen that the lower-frequency inverter output momentarily switched to a high frequency [29–31]. Figure 27 shows the hardware results of the capacitance voltages when the load was rapidly raised from 5 KW to 10 KW. It was clear that regardless of the case of an immediate load shift, the capacitor voltage only slightly deviated from its initial value before returning to it.

Figure 20. Hardware prototype model of the proposed inverter.

Figure 21. High-frequency top inverter PWM for PS<sub>1</sub> and PS<sub>3</sub>.

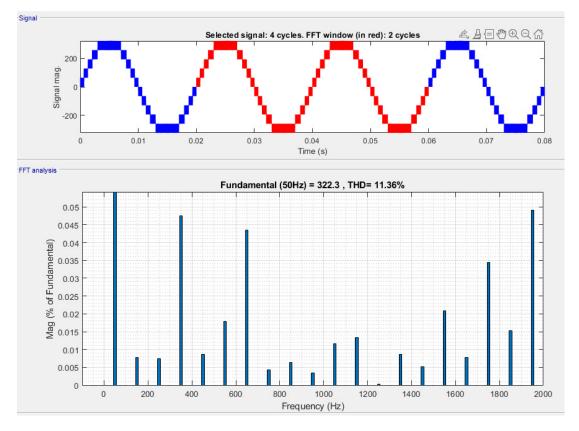

The FFT analyses of the output voltage for the 11- and 15-level inverters are shown in Figures 28 and 29. The total harmonic distortions (THDs) of 11.36% and 8.02% were obtained for a fundamental frequency of 50 Hz. Without utilizing substantial voltage filters at the output, the load voltage was reached with a symmetrical voltage step equal to 100 V. The load current waveform with its harmonic spectra was reduced for a proposed MLI with a load of 5 kW and 0.8 LPF.

Figure 22. High-frequency top inverter PWM for PS<sub>2</sub> and PS<sub>4</sub>.

Figure 23. Low-frequency bottom inverter PWM for PS<sub>5</sub> and PS<sub>7</sub>.

Figure 24. Low-frequency bottom inverter PWM for PS<sub>6</sub> and PS<sub>8</sub>.

Figure 25. Bottom inverter PWM for  $SS_1$  and  $SS_2$ .

Figure 26. (a) Output voltage at the bottom inverter. (b) Voltage at the top inverter. (c) Output voltage across the load. (d) Load current hardware waveform.

Figure 27. Output current with load variation.

Figure 28. FFT analysis for 11-level inverter.

**Figure 29.** FFT analysis for 15-level inverter.

Table 5 details the current THD and the number of switches required for the 11- and 15level inverters. The current THD values were 0.88 and 2.41 for 15 and 11 MLI, respectively. Table 6 demonstrates that the proposed topology outperformed the alternative topologies regarding switching devices and THD. In the MLI topologies, as the level increased, the THD reduced, and the decreased THD offered higher performance and power quality.

| Table 5. V | /oltage | THD for | 11- and | 15-level | inverters. |

|------------|---------|---------|---------|----------|------------|

|------------|---------|---------|---------|----------|------------|

| Levels | No. of Primary Switches<br>in the Top Inverter | No. of Primary Switches<br>in the Bottom Inverter | No. of Secondary<br>Switches in the Bottom | Current THD in % |

|--------|------------------------------------------------|---------------------------------------------------|--------------------------------------------|------------------|

| 15     | 4                                              | 4                                                 | 2                                          | 0.88             |

| 11     | 4                                              | 4                                                 | 1                                          | 2.41             |

| -             |        | -                             | -                   |                  |

|---------------|--------|-------------------------------|---------------------|------------------|

| Previous Work | Levels | Total No. of<br>Switches Used | Total DC<br>Sources | Current THD in % |

| [9]           | 15     | 10                            | 3                   | 2.32             |

| [10]          | 15     | 10                            | 3                   | 1.83             |

| [17]          | 15     | 10                            | 3                   | 1.08             |

| Proposed      | 15     | 10                            | 2                   | 0.88             |

Table 6. THD comparison of various 15-level MLIs with the proposed inverter.

### 7. Conclusions

MLI provides improved output waveforms with a low THD. This study proposed a novel PWM technique for cascaded MLI with the few discrete DC sources and power electronics components possible. The capacitor voltages were also balanced using cuttingedge voltage balancing technology. The 15-level inverter converted a DC input voltage into a sinusoidal waveform with a lower THD of 8.02% compared with an 11-level MLI. The proposed inverter was simulated using MATLAB/Simulink, and experimental results were obtained, which were consistent with the simulation. The gate signals for the simulated inverter were generated using a SPARTAN 3A FPGA board, and these pulses were used to obtain the 15-level output of the inverter. The method balanced the capacitor voltages; hence, the generated inverter did not need extra multi-outlet DC–DC converters. The proposed inverter has various benefits apart from fewer components; it can be smaller and cost less and can have fewer switching losses and higher efficiency. As a result, applications requiring high and medium power can be employed with the proposed inverter. In future, this work can be extended to apply power balancing and machine learning approaches for controlling and diagnosing various faults in MLI.

**Author Contributions:** Conceptualization, S.K.R.; methodology, G.C.R.I.; investigation, G.C.R.I. and P.G.; writing—original draft preparation, S.K.R. and I.V; writing—review and editing, S.K.R.; resources, I.V.; visualization and administration, I.V. and M.L.A.; funding acquisition, M.L.A. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded by the Deputyship for Research & Innovation, Ministry of Education in Saudi Arabia for funding this research work through project number 223202.

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

Data Availability Statement: Not applicable.

Acknowledgments: The authors extend their appreciation to the Deputyship for Research & Innovation, Ministry of Education in Saudi Arabia for funding this research work through project number 223202.

**Conflicts of Interest:** There are no conflicts of interest declared by the authors.

## References

- 1. Almehizia, A.A.; Al-Masri, H.M.; Ehsani, M. Feasibility Study of sustainable energy sources in a fossil fuel rich country. *IEEE Trans. Ind. Appl.* **2019**, *55*, 4433–4440. [CrossRef]

- 2. Kumar, B.R.; Sundararaju, K.; Saravanan, S.; Senthil Kumar, R. Mboa based PV array interconnection scheme for enlarging the harvested power under PS condition. *Int. J. Electron.* **2022**, *110*, 26–53.

- Podder, A.K.; Roy, N.K.; Pota, H.R. MPPT methods for solar PV systems: A critical review based on tracking nature. *IET Renew.* Power Gener. 2019, 13, 1615–1632. [CrossRef]

- 4. Alzahrani, A.; Ramu, S.K.; Devarajan, G.; Vairavasundaram, I.; Vairavasundaram, S. A review on hydrogen-based hybrid microgrid system: Topologies for hydrogen energy storage, integration, and energy management with solar and wind energy. *Energies* **2022**, *15*, 7979. [CrossRef]

- Ramu, S.K.; Paramasivam, S.; Muthusamy, S.; Panchal, H.; Sadasivuni, K.K.; Noorollahi, Y. A novel design of switched boost action based multiport converter using dsPIC controller for Renewable Energy Applications. *Energy Sources Part A Recovery Util. Environ. Eff.* 2021, 44, 75–90. [CrossRef]

- 6. Rong, F.; Gong, X.; Huang, S. A novel grid-connected PV system based on MMC to get the maximum power under partial shading conditions. *IEEE Trans. Power Electron.* **2017**, *32*, 4320–4333. [CrossRef]

- Farivar, G.; Hredzak, B.; Agelidis, V.G. A DC-side sensorless cascaded H-bridge multilevel converter-based Photovoltaic System. IEEE Trans. Ind. Electron. 2016, 63, 4233–4241. [CrossRef]

- Can, E. Mathematical algorithm of Fuzzy Logic Controller for multilevel inverter creating vertical divided voltage. *Acta Polytech*. 2019, 59, 1–11. [CrossRef]

- 9. Can, E. Novel high multilevel inverters investigated on simulation. *Electr. Eng.* 2016, 99, 633–638. [CrossRef]

- 10. Bendyk, M.S.; Luk, P.C.-K.; Alkhafaji, M.H. Control strategy for a modified Cascade multilevel inverter with dual DC source for enhanced Drivetrain Operation. *IEEE Trans. Ind. Appl.* **2017**, *53*, 4655–4664. [CrossRef]

- 11. Can, E.; Sayan, H.H. A novel SSPWM controlling inverter running nonlinear device. *Electr. Eng.* 2016, 100, 39–46. [CrossRef]

- 12. Yu, Y.; Konstantinou, G.; Hredzak, B.; Agelidis, V.G. Power balance of cascaded H-bridge multilevel converters for large-scale photovoltaic integration. *IEEE Trans. Power Electron.* **2016**, *31*, 292–303. [CrossRef]

- 13. Yu, Y.; Konstantinou, G.; Hredzak, B.; Agelidis, V.G. Operation of cascaded H-bridge multilevel converters for large-scale photovoltaic power plants under bridge failures. *IEEE Trans. Ind. Electron.* **2015**, *62*, 7228–7236. [CrossRef]

- 14. Kaliamoorthy, M.; Rajasekaran, V.; Raj, I.G.C. Single-phase fifteen-level grid-connected inverter for photovoltaic system with evolutionary programming based MPPT algorithm. *Sol. Energy* **2014**, *105*, 314–329. [CrossRef]

- 15. Kaliamoorthy, M.; Rajasekaran, V.; Christopher Raj, I.G.; Hubert Tony Raj, L. Generalised hybrid switching topology for a single-phase Modular Multilevel Inverter. *IET Power Electron.* **2014**, *7*, 2472–2485. [CrossRef]

- Ramu, S.K.; Irudayaraj, G.C.; Paramasivam, S.K.; Murugesan, R.; Muthusamy, S.; Sundararajan, S.C.; Panchal, H.; Sadasivuni, K.K.; Meena, R.S. A simplified methodology for renewable energy integration and harmonic current reduction in Hybrid Micro Grid. *Energy Sources Part A Recovery Util. Environ. Eff.* 2021, 44, 8357–8379. [CrossRef]

- 17. Hu, P.; Teodorescu, R.; Wang, S.; Li, S.; Guerrero, J.M. A currentless sorting and selection-based capacitor-voltage-balancing method for modular multilevel converters. *IEEE Trans. Power Electron.* **2019**, *34*, 1022–1025. [CrossRef]

- Peftitsis, D.; Tolstoy, G.; Antonopoulos, A.; Rabkowski, J.; Jang-Kwon, L.; Bakowski, M.; Ängquist, L.; Nee, H. High-power modular multilevel converters with SIC JFETs. *IEEE Trans. Power Electron.* 2012, 27, 28–36. [CrossRef]

- 19. Can, E.; Sayan, H.H. Development of fractional sinus pulse width modulation with β gap on three step signal processing. *Int. J. Electron.* **2022**, *110*, 527–546. [CrossRef]

- 20. Can, E. A new multi-level inverter with reverse connected dual DC to DC converter at simulation. *Int. J. Model. Simul.* **2020**, *42*, 34–46. [CrossRef]

- 21. Can, E.; Sayan, H.H. Investigation of the effect of the gap at the zero-crossing point of pwms creating the first level voltage in a multi-level inverter. *J. Eng. Res.* **2022**. [CrossRef]

- 22. Anand, I.; Senthilkumar, S.; Biswas, D.; Kaliamoorthy, M. Dynamic Power Management System employing a single-stage power converter for standalone solar PV applications. *IEEE Trans. Power Electron.* **2018**, *33*, 10352–10362. [CrossRef]

- 23. Hinago, Y.; Koizumi, H. A single-phase multilevel inverter using switched series/parallel DC voltage sources. *IEEE Trans. Ind. Electron.* **2010**, *57*, 2643–2650. [CrossRef]

- 24. Sabyasachi, S.; Borghate, V.B.; Karasani, R.R.; Maddugari, S.K.; Suryawanshi, H.M. Hybrid control technique-based three-phase cascaded multilevel inverter topology. *IEEE Access* 2017, *5*, 26912–26921. [CrossRef]

- Agrawal, N.; Bansal, P. A new 21-level asymmetrical multilevel inverter topology with different PWM techniques. In Proceedings

of the 2017 Recent Developments in Control, Automation & Power Engineering (RDCAPE), Noida, India, 26–27 October 2017.

- Reddy, V.P.; Muralikumar, K.; Ponnambalam, P.; Mahapatra, A. Asymmetric 15-level multilevel inverter with fuzzy controller using super imposed carrier PWM. In Proceedings of the 2017 Innovations in Power and Advanced Computing Technologies (i-PACT), Vellore, India, 21–22 April 2017.

- 27. Saravanan, S.; Senthil Kumar, R.; Prakash, A.; Chinnadurai, T.; Tiwari, R.; Prabaharan, N.; Chitti Babu, B. Photovoltaic array reconfiguration to extract maximum power under partially shaded conditions. In *Distributed Energy Resources in Microgrids*; Academic Press: Cambridge, MA, USA, 2019; pp. 215–241.

- Sarasvathy, K.; Luciana, M.L.; Kumar, R.S. Comparison of sine, hysteresis, SVPWM and predictive PWM techniques for shunt active power filter. In Proceedings of the 2017 IEEE International Conference on Electrical, Instrumentation and Communication Engineering (ICEICE), Karur, India, 27–28 April 2017.

- 29. Alghaythi, M.L.; O'Connell, R.M.; Islam, N.E.; Khan, M.M.S.; Guerrero, J.M. A High Step-Up Interleaved DC–DC Converter with Voltage Multiplier and Coupled Inductors for Renewable Energy Systems. *IEEE Access* **2020**, *8*, 123165–123174. [CrossRef]

- Alghaythi, M.L.; O'Connell, R.M.; Islam, N.E. Design of a High Step-up DC-DC Power Converter with Voltage Multiplier Cells and Reduced Losses on Semiconductors for Photovoltaic Systems. In Proceedings of the 2019 IEEE Electric Ship Technologies Symposium (ESTS), Arlington, VA, USA, 14–16 August 2019; pp. 214–218.

- Najwan Hamidi, M.; Ishak, D.; Ammirrul Atiqi Mohd Zainuri, M.; Ai Ooi, C.; Tarmizi, T. Asymmetrical multi-level DC-link inverter for PV Energy System with perturb and observe based voltage regulator and capacitor compensator. *J. Mod. Power Syst. Clean Energy* 2021, 9, 199–209. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.