# Article High Performance Drain Engineered InGaN Heterostructure Tunnel Field Effect Transistor

Xiaoling Duan \*, Jincheng Zhang \*, Jiabo Chen, Tao Zhang, Jiaduo Zhu, Zhiyu Lin and Yue Hao

Wide Bandgap Semiconductor Technology Disciplines State Key Laboratory, School of Microelectronics, Xidia University, Xi'an 710071, China; jbchen@stu.xidian.edu.cn (J.C.); zhangtao9204@sina.com (T.Z.); jdzhu@xidian.edu.cn (Z.L.); yhao@xidian.edu.cn (Y.H.)

Correspondence: duanxiaoling@xidian.edu.cn (X.D.); jchzhang@xidian.edu.cn (J.Z.);

Tel.: +86-29-8820-1759 (X.D.); +86-29-8820-1446 (J.Z.)

Received: 27 December 2018; Accepted: 18 January 2019; Published: 21 January 2019

**Abstract:** A drain engineered InGaN heterostructure tunnel field effect transistor (TFET) is proposed and investigated by Silvaco Atlas simulation. This structure uses an additional metal on the drain region to modulate the energy band near the drain/channel interface in the drain regions, and increase the tunneling barrier for the flow of holes from the conduction band of the drain to the valence band of the channel region under negative gate bias for n-TFET, which induces the ambipolar current being reduced from  $1.93 \times 10^{-8}$  to  $1.46 \times 10^{-11}$  A/µm. In addition, polar InGaN heterostructure TFET having a polarization effect can adjust the energy band structure and achieve steep interband tunneling. The average subthreshold swing of the polar drain engineered heterostructure TFET (DE-HTFET) is reduced by 53.3% compared to that of the nonpolar DE-HTFET. Furthermore, I<sub>ON</sub> increases 100% from 137 mA/mm of nonpolar DE-HTFET to 274 mA/mm of polar DE-HTFET.

**Keywords:** drain engineered; tunnel field effect transistor (TFET); polarization; ambipolar; subthreshold; ON-state

# 1. Introduction

Tunnel field effect transistors (TFETs) have been considered as attractive alternative replacements to metal-oxide-semiconductor field effect transistors (MOSFETs) for low power applications [1–3], due to the conductive mechanism of band to band tunneling, realizing a steep subthreshold swing (SS) (less than 60 mV/dec at room temperature), good immunity against Short Channel Effects (SCEs) and high ON-state current (I<sub>ON</sub>) to OFF-state current (I<sub>OFF</sub>) ratio (I<sub>ON</sub>/I<sub>OFF</sub>) [1,4,5]. Although TFETs have various benefits, there are still some problems to be solved, such as the ambipolar behavior [6,7], low ON-state current (I<sub>ON</sub>) [8], and less-than-idea SS. To solve these problems, different techniques such as the use of high-k dielectric materials [9], heterojunction engineering [10–13], source pocket based devices [14,15], junction-less concept based devices [16–18], and narrow bandgap materials have been investigated to boost I<sub>ON</sub>. Drain doping profile investigation [7], gate-drain electrode gap control [19], the hetero-dielectric box concept [20], and heterojunction engineering have been developed to restrain ambipolar behavior.

III Nitride is the direct bandgap semiconductor, and its bandgap can be modulated from 0.7 eV (InN) to 6.2 eV (AlN), while the natural polarization effect will facilitate the formation of a steep energy band at the tunneling junction of the heterostructure, inducing a steep tunneling junction, small subthreshold swing and large ON-state current [21]. Recently, it has been reported that III Nitride TFETs exhibit superior device characteristics, showing the great potential of the application in the low power field [21–24]. However, the research on III Nitride TFET devices is just beginning, and it is worth further study.

In this paper, the drain engineering method uses workfunction engineering on an additional metal to modulate the energy band on the drain/channel interface in the drain regions and increase the tunneling barrier for the flow of holes from the conduction band of the drain to the valence band of the channel region under negative gate bias for n-TFET, which will reduce the ambipolar current of InGaN heterojunction TFETs (HTFETs). In addition, the improvement mechanism of the polarization effect on the subthreshold and ON-state characteristics of polar InGaN HTFETs are investigated at length.

The remaining paper is organized as follows: Section 2 presents the device structure, simulation models and material parameters. Section 3 is dedicated to results and discussions, including the drain engineered TFET used to suppress the ambipolar current of InGaN HTFET, and the performance comparison and analysis of polar and nonpolar HTFETs. Finally, Section 4 concludes the paper with some important findings.

# 2. Device Structure and Simulation Parameters

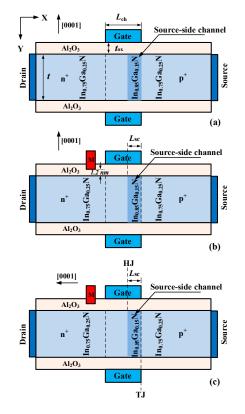

Figure 1 shows the cross-sectional views of InGaN nonpolar heterostructure TFET (HTFET), InGaN nonpolar drain engineered heterostructure TFET (DE-HTFET), and InGaN polar DE-HTFET, respectively. The InGaN HTFET contains a source-side channel to improve the ON-state current and reduce the subthreshold swing. This work has been reported in reference [24]. The channel length ( $L_{ch}$ ) and the channel thickness (t) are set as 50 nm, and 10 nm, respectively. The drain metal and the gate ( $L_{GD}$ ) are 100 nm. The gate dielectric material is Al<sub>2</sub>O<sub>3</sub> with a thickness ( $t_{ox}$ ) of 3 nm. The doping concentrations in the source, the channel, and the drain region are p+ 9.9 × 10<sup>19</sup> cm<sup>-3</sup>, n 1 × 10<sup>15</sup> cm<sup>-3</sup>, and n+ 1.2 × 10<sup>19</sup> cm<sup>-3</sup>, respectively. The workfunction of gate metal is 5.1 eV. The proposed nonpolar DE-HTFET contains an additional drain engineering metal with the length of 10 nm and a dielectric thickness of 1.2 nm to modulate the energy band in the drain/channel region and finally reduce the ambipolar current. Along with this, the polar DE-HTFET is proposed to modulate the energy band at the source/channel tunneling junction, and will further improve the device characteristics.

**Figure 1.** Cross-sectional views of the nonpolar (**a**) conventional, (**b**) drain engineered InGaN tunnel field effect transistor (TFET), and (**c**) polar drain engineered InGaN TFET.

Simulations are carried out using a 2D Silvaco Atlas simulator (5.19.20.R, Silvaco Inc., Santa Clara, CA, USA) [25]. The nonlocal band to-band tunneling (BTBT) is incorporated in the simulation for the calculation of the tunneling rate of charge carriers. The Shockley–Read–Hall (SRH) carrier recombination model, bandgap narrowing (BGN) model, constant low field mobility model, and field-dependent mobility model at high electric fields are activated using the SRH, BGN and FLDMOB parameters, respectively. The polarization effect in the polar TFET is simulated by a fixed polarization charge at the heterojunction interface [26], and the density of polarization surface charge ( $\sigma_{pol}$ ) will be discussed in Section 3.2. Other material parameters used in the simulations are presented in Table 1.

In the electrical characteristics analysis below,  $I_{ON}$  is defined to be the drain current  $I_D$  at  $V_G = V_D$ = 1 V. The average sub-threshold swing (SS<sub>avg</sub>) is obtained from the  $I_D$ -V<sub>G</sub> curve, it is given by

$$SS_{avg} = (V_{TH} - V_{OFF}) / (logI_{V_{TH}} - logI_{OFF})$$

(1)

where the threshold voltage  $V_{TH}$  is defined to be the gate voltage (V<sub>G</sub>) at current of  $1 \times 10^{-7}$  A/mm, and  $V_{OFF}$  is the gate voltage at I<sub>D</sub> of  $10^{-18}$  A/mm.

| Parameters                                             | In <sub>0.75</sub> Ga <sub>0.25</sub> N | In <sub>0.85</sub> Ga <sub>0.15</sub> N |

|--------------------------------------------------------|-----------------------------------------|-----------------------------------------|

| Band gap E <sub>g</sub> (eV)                           | 1.1125                                  | 0.9265                                  |

| Hole effective mass $(m_0)$                            | 0.295                                   | 0.273                                   |

| Electron effective mass $(m_0)$                        | 0.1025                                  | 0.0895                                  |

| Static dielectric constant $\varepsilon_r$             | 12.75                                   | 13.05                                   |

| Electron mobility μ <sub>e</sub> (cm <sup>2</sup> /Vs) | 1050                                    | 1050                                    |

| Hole mobility $\mu_h$ (cm <sup>2</sup> /Vs)            | 20                                      | 20                                      |

Table 1. Material parameters used in simulations [21].

#### 3. Results and Discussions

#### 3.1. Drain Engineered HTFET to Suppress Ambipolar Current

## 3.1.1. Impact of Drain Engineering Metal Position on Electrical Characteristic of DE-HTFET

Drain engineered HTFET using an additional drain engineering metal (M) to modulate the energy band can increase the tunneling barrier for the flow of holes on the drain/channel interface, and reduce the ambipolar current at the negative  $V_G$  bias. The M position will obviously affect the electrical characteristic of DE-HTFET. The following simulations are discussed with the different M position at the M workfunction ( $\phi_M$ ) of 5.15 eV.

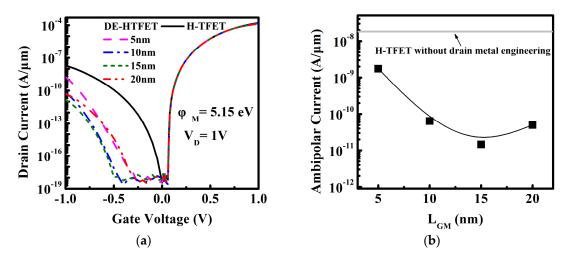

Figure 2 displays the I-V curves of HTFET without M and DE-HTFET with the different gate to M space (L<sub>GM</sub>). HTFET without drain engineering metal shows an ambipolar current of  $1.93 \times 10^{-8}$  A/µm. Overall, I<sub>ambipolar</sub> of DE-HTFET by drain metal engineering has been obviously reduced compared with that of HTFET without M. As L<sub>GM</sub> increases from 5 nm to 20 nm, I<sub>ambipolar</sub> reduces firstly and then increases. At L<sub>GM</sub> of 15 nm, DE-HTFET obtains the smallest I<sub>ambipolar</sub> (1.46 × 10<sup>-11</sup> A/µm), while the ON-state current (I<sub>ON</sub>) is almost not degraded.

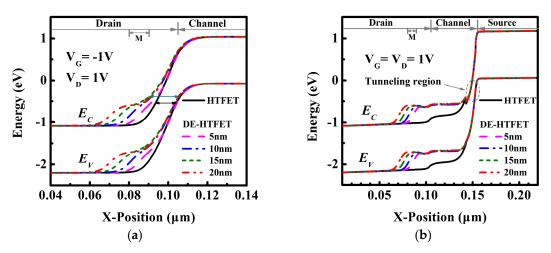

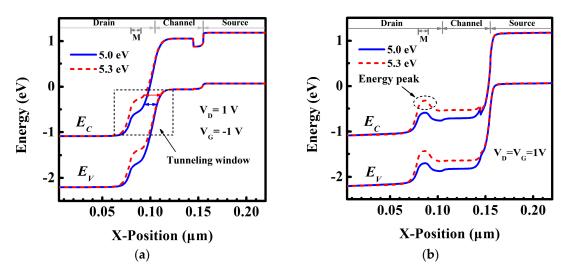

To gain a better insight into the variation of  $I_{ambipolar}$  and  $I_{ON}$ , energy band profiles for  $V_G$  of -1 V and 1 V are shown in Figure 3a,b, respectively. Figure 3a shows the energy band of DE-HTFET near the drain/channel junction at  $V_G$  of -1 V. With drain metal engineering, the tunneling distance of DE-HTFET at the negative gate bias is larger than that of HTFET. The tunneling distance of DE-HTFET firstly increases and then decreases with the increase of L<sub>GM</sub>. DE-HTFET with L<sub>GM</sub> = 15 nm has the largest tunneling distance in the L<sub>GM</sub> range from 5 nm to 20 nm. The larger tunneling distance will contribute to a lower electric field (E) and thereby a smaller tunneling rate, as illustrated with Kane's formula [27]:

$$P_{tun} \sim \frac{E^2 m_r^{1/2}}{E_g^{1/2}} \exp\left(-\frac{C_2 m_r^{1/2} E_g^{3/2}}{E}\right),$$

(2)

where E is the electric field,  $C_2$  is a constant and  $m_r$  is effective mass. This can well explain the variation tendency of  $I_{ambipolar}$ . Thus, DE-HTFET with  $L_{GM}$  of 15 nm has the smallest  $I_{ambipolar}$ . Figure 3b shows the energy band of DE-HTFET at the ON-state ( $V_G = V_D = 1$  V). It is obvious that  $L_{GM}$  variation has almost no influence over the tunneling distance at the source/channel junction, therefore  $I_{ON}$  is almost not degraded. Considering the aforementioned factors,  $L_{GM}$  of 15 nm is selected in the following discussions.

**Figure 2.** (a) Transfer characteristic of HTFET and DE-HTFET with varied  $L_{GM}$  at  $V_D$  of 1 V and  $\phi_M$  of 5.15 eV, and (b) ambipolar current with different  $L_{GM}$  extracted from the I-V curve.

**Figure 3.** (a) Energy band diagram of DE-HTFET near the drain/channel tunneling junction with  $L_{GM} = 15$  nm at  $V_G$  of -1 V,  $V_D$  of 1 V, and (b) Energy band diagram of DE-HTFET at ON-state.

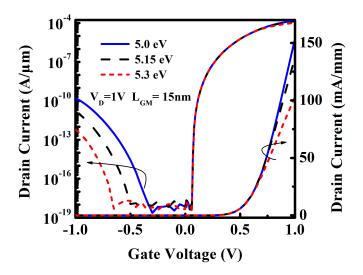

3.1.2. Impact of Drain Engineering Metal Workfunction ( $\varphi_M$ ) on Electrical Characteristic of DE-HTFET

In this section, in order to find the optimal drain engineering metal, the impacts of the various of workfunction are studied in detail. The function of the drain engineering metal is to increase the tunneling barrier of the drain/channel junction at the negative V<sub>G</sub> bias, so a relatively high work function of the drain engineering metal may be a good choice. Here, electrical characteristics of DE-HTFET with drain engineering metal  $\varphi_M = 5.0, 5.15$ , and 5.3 eV are simulated, respectively, and the results are shown in Figure 4. Based on the results, it is indicated that I<sub>ambipolar</sub> presents an exponential decrease trend with the increment of  $\varphi_M$ , and I<sub>ON</sub> stays in the same level. However, there is also a balance between I<sub>ambipolar</sub> and I<sub>ON</sub>, that is to say, a higher workfunction is not always better. I<sub>ON</sub> also reduces with the increment of  $\varphi_M$ , although it is in the same level. As  $\varphi_M$  increases from 5.0 eV

to 5.15 eV,  $I_{ON}$  decreases slightly. However, at  $\phi_M$  of 5.3 eV,  $I_{ON}$  decreases significantly, which is not desirable.

Figure 4. Transfer characteristic of DE-HTFET with various  $\phi_M$  at  $V_D$  of 1 V.

To gain a better insight into the variation of  $I_{ambipolar}$  and  $I_{ON}$ , Figure 5 exhibits the energy band diagram of DE-HTFET with  $\varphi_M = 5.0$  eV and 5.3 eV for VG of -1 V and 1 V, respectively. Figure 5a shows that the tunneling distance in the tunneling window for DE-HTFET with  $\varphi_M = 5.3$  eV is larger than that for DE-HTFET with  $\varphi_M = 5.0$  eV, which results in the lower BTBT tunneling rate at the drain/channel interface for DE-HTFET with higher  $\varphi_M$ , therefore, lower  $I_{ambipolar}$  is obtained for higher  $\varphi_M$ . Figure 5b shows the energy band profile at the ON-state. An energy peak is created near the drain/channel interface, which will act as a barrier for electrons tunneling from the source to the drain region at the positive bias [28]. Therefore,  $I_{ON}$  of DE-HTFET with  $\varphi_M = 5.3$  eV significantly degrades as shown in Figure 4. To make a trade-off between  $I_{ambipolar}$  and  $I_{ON}$ ,  $\varphi_M$  of 5.15 eV is selected as the last choice.

**Figure 5.** Energy band diagram at the line 1 nm away from the interface of InGaN/Al<sub>2</sub>O<sub>3</sub> for DE-HTFET with  $\varphi_M$  = 5.0 eV and 5.3 eV as (a)  $V_D$  = 1 V,  $V_G$  = -1 V, and (b)  $V_D$  =  $V_G$  = 1 V.

## 3.2. Polar Heterostructure DE-HTFET to Improve Device Performances

The heterostructures in TFETs studied above are all along the nonpolar plane, so no polarization charge exists at the interface of heterojunction. However, studies show that the polarization engineering

in the III-nitride heterostructure can further adjust the energy band structure and achieve the interband tunneling [21]. It needs the heterostructure growing along the c-axis. Because of spontaneous polarization and piezoelectric polarization along the c-axis, large amounts of fixed polarization charge can be induced at the heterojunction interface. The polarization charge generated by polarization engineering can lead to a large internal electric field near the heterojunction interface, and increase the tunneling rate. On the other hand, polarization also changes the energy structure near the tunneling junction and helps improve TFET performance.

Herein, the polar and non-polar DE-HTFETs are compared. Figure 1c shows the schematic diagram of polar DE-HTFETs. The growth direction is along [0001], that is, the negative direction of X-axis in Figure 1. In this case, the polarization charge at the interface of III-Nitride heterojunction will be taken into account in the simulations. In particular, the polarization charge near the tunneling junction may have important effects on the device characteristics of InGaN DE-HTFET. By calculation, the density of polarization surface charge ( $\sigma_{pol}$ ) is  $-1.27134 \times 10^{13}$ /cm<sup>2</sup> at the position of TJ, and  $1.27134 \times 10^{13}$ /cm<sup>2</sup> at the position of HJ. The negative value of  $\sigma_{pol}$  represents a negative polarization charge, and vice versa.

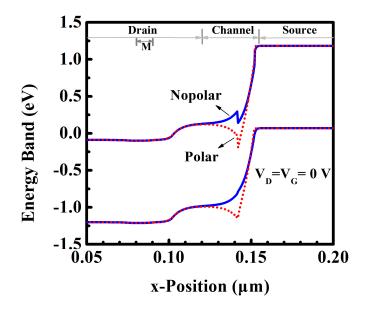

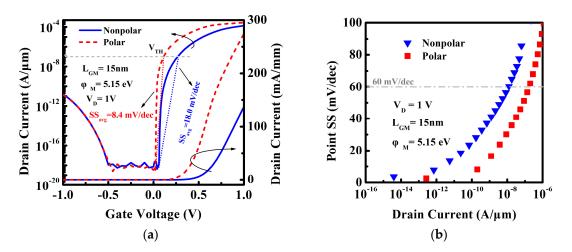

The polarization changes the energy structure near the tunneling junction. Figure 6 shows that the polar DE-HTFET has a steeper energy band near the tunneling junction, which facilitates the better subthreshold and ON-state characteristics. Figure 7a displays the transfer characteristic of nonpolar and polar DE-HTFETs at  $L_{GM}$  of 15 nm and  $V_D$  of 1 V.  $I_D$ - $V_G$  curve indicates a smaller threshold voltage for the polar DE-HTFET, which will be more beneficial to the low-power applications. Besides this, the average subthreshold swing (SS<sub>avg</sub>) of the polar DE-HTFET is reduced by 53.3% compared to that of the nonpolar DE-HTFET. Also,  $I_{ON}$  increases 100% from 137 mA/mm of nonpolar DE-HTFET to 274 mA/mm of polar DE-HTFET. Figure 7b shows the point subthreshold swing (SS<sub>point</sub>) of TFETs with different  $I_D$  extracted from the  $I_D$ - $V_G$  curve. Obviously, SS<sub>point</sub> of the polar DE-HTFET is smaller than that of the nonpolar TFET at any  $I_D$  value.

Figure 6. Energy band diagram in the thermal state.

**Figure 7.** (**a**) Transfer characteristic and (**b**) point subthreshold swing for the nonpolar and polar InGaN TFET at V<sub>D</sub> of 1 V.

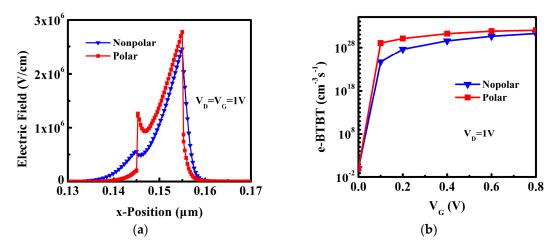

To further investigate the mechanism of performance improvement for polar DE-HTFET, the electric field and e-BTBT rate are discussed as follows. Figure 8a exhibits that the transverse electric field intensity of the channel near the tunneling junction of polar DE-HTFET is higher than that of the non-polar device under the effect of polarization at the ON-state. Therefore, the e-BTBT rate at ON-state between the source and channel of the polar DE-HTFET is much larger than that of the nonpolar DE-HTFET as shown in Figure 7b, which is consistent with Kane's Formula (1). This is the reason why the polar InGaN DE-HTFETs have the larger I<sub>ON</sub>. On the other hand, the e-BTBT rate with various of V<sub>G</sub> is shown in Figure 8b. When V<sub>G</sub> = 0 V, the tunneling rate of both TFETs is almost 0; when V<sub>G</sub> increases to 0.1 V, the tunneling rate of polar DE-HTFET increases to  $1.14 \times 10^{29}$  cm<sup>-3</sup>s<sup>-1</sup>, however the tunneling rate of non-polar DE-HTFET is only  $4.49 \times 10^{24}$  cm<sup>-3</sup>s<sup>-1</sup>. The significant increase of the tunneling rate with the increase of V<sub>G</sub> for polar DE-HTFETs in the subthreshold region makes polar DE-HTFETs have the lower subthreshold swing.

Figure 8. (a) Electric field in the ON-state, and (b) electron tunneling rate with various  $V_{G}$ .

## 4. Conclusions

In summary, a drain engineered InGaN HTFET is investigated by Atlas simulation in this paper. Firstly, with the trade-off between  $I_{ambipolar}$  and  $I_{ON}$ ,  $I_{ambipolar}$  is reduced from  $1.93 \times 10^{-8}$  A/µm of DE-HTFET to  $1.46 \times 10^{-11}$  A/µm of HTFET by studying the impact of the drain engineering metal position and workfunction on device performances. The decreased  $I_{ambipolar}$  results from the energy band modulation by the drain engineering metal and workfunction near the drain/channel junction

in the drain region. Secondly, the polarization effect induces a large internal electric field near the heterojunction interface, changes the energy structure near the tunneling junction, and helps improve TFET performance. SS<sub>avg</sub> of the polar InGaN DE-HTFET is 8.4 mV/dec, which is reduced by 53.3% compared to that of the nonpolar InGaN DE-HTFET. Also, I<sub>ON</sub> increases 100% from 137 mA/mm of nonpolar DE-HTFET to 274 mA/mm of polar DE-HTFET. Therefore, the structure of polar InGaN DE-HTFET embodies much more promising in low power applications.

**Author Contributions:** X.D. provided the concept, designed the structures, performed the simulations, and wrote the manuscript; J.Z. (Jincheng Zhang) and Y.H. gave valuable suggestions on the manuscript; All authors discussed the results and approved the final manuscript.

**Funding:** This work was supported by the National Key Research and Development Program (Grant No. 2016YFB0400100) and the Fundamental Research Funds for the Central Universities (Grand No. JB181104).

Conflicts of Interest: The authors declare no conflict of interest.

## References

- 1. Ionescu, A.M.; Riel, H. Tunnel field effect transistors as energy efficient electronic switches. *Nature* **2011**, 479, 329–337. [CrossRef] [PubMed]

- 2. Avci, U.E.; Morris, D.H.; Young, I.A. Tunnel field-effect transistors: Prospects and challenges. J. Electron. *Dev. Soc.* 2015, *3*, 88–95. [CrossRef]

- 3. Koswatta, S.O.; Lundstrom, M.S.; Nikonov, D.E. Performance comparison between p-i-n tunneling transistors and conventional MOSFETs. *IEEE Trans. Electron Devices* **2007**, *56*, 456–465. [CrossRef]

- 4. Luisier, M.; Klimeck, G. Performance comparisons of tunneling field-effect transistors made of InSb, Carbon, and GaSb–InAs broken gap heterostructures, In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; pp. 1–4.

- 5. Nirschla, T.; Henzler, S.; Fischer, J.; Fulde, M.; Bargagli-Stoffi, A.; Sterkel, M.; Sedlmeir, J.; Weber, C.; Heinrich, R.; Schaper, U.; et al. Scaling properties of the tunneling field effect transistor (TFET): Device and circuit. *Solid-State Electron.* **2006**, *50*, 44–51. [CrossRef]

- 6. Vijayvargiya, V.; Vishvakarma, S.K. Effect of drain doping profile on double-gate tunnel field-effect transistor and its influence on device RF performance. *IEEE Trans. Nanotechnol.* **2014**, *13*, 974–981. [CrossRef]

- 7. Loan, S.A.; Alharbi, A.G.; Rafat, M. Ambipolar leakage suppression in electron–hole bilayer TFET: Investigation and analysis. *J. Comput. Electron.* **2018**, *17*, 977–985.

- 8. Beneventi, G.B.; Gnani, E.; Gnudi, A.; Reggiani, S.; Baccarani, G. Dual-metal-gate InAs tunnel FET with enhanced turn-on steepness and high ON-current. *IEEE Trans. Electron. Dev.* **2014**, *61*, 776–784. [CrossRef]

- Choi, W.Y.; Lee, W. Hetero-gate-dielectric tunneling field-effect transistors. *IEEE Trans. Electron. Dev.* 2010, 57, 2317–2319. [CrossRef]

- 10. Chauhan, S.S.; Sharma, N. Enhancing analog performance and suppression of subthreshold swing using hetero-junctionless double gate TFETs. *Superlattices Microstruct.* **2017**, *112*, 257–261. [CrossRef]

- 11. Peng, Y.; Han, G.; Wang, H.; Zhang, C.; Liu, Y.; Wang, Y.; Zhao, S.; Zhang, J.; Hao, Y. InN/InGaN complementary heterojunction-enhanced tunneling field-effect transistor with enhanced subthreshold swing and tunneling current. *Superlattices Microstruct.* **2016**, *93*, 144–152. [CrossRef]

- 12. Wang, H.; Liu, Y.; Liu, M.; Zhang, Q.; Zhang, C.; Ma, X.; Zhang, J.; Hao, Y.; Han, G. Performance improvement in novel germanium–tin/germanium heterojunction-enhanced p-channel tunneling field-effect transistor. *Superlattices Microstruct.* **2015**, *83*, 401–410. [CrossRef]

- Wang, Y.; Liu, Y.; Han, G.; Wang, H.; Zhang, C.; Zhang, J.; Hao, Y. Theoretical investigation of GaAsBi/GaAsN tunneling field-effect transistors with type-II staggered tunneling junction. *Superlattices Microstruct.* 2017, 106, 139–146. [CrossRef]

- 14. Raad, B.R.; Sharma, D.; Kondekar, P.; Nigam, K.; Baronia, S. DC and analog/RF performance optimisation of source pocket dual work function TFET. *Int. J. Electron.* **2017**, *104*, 1992–2006. [CrossRef]

- Chang, H.-Y.; Adams, B.; Chien, P.-Y.; Li, J.; Woo, J.C.S. Improved subthreshold and output characteristics of source-pocket Si tunnel FET by the application of laser annealing. *IEEE Trans. Electron Devices* 2013, 60, 92–96. [CrossRef]

- 16. Kumar, M.J.; Janardhanan, S. Doping-less tunnel field effect transistor: Design and investigation. *IEEE Trans. Electron Devices* **2013**, *60*, 3285–3290. [CrossRef]

- 17. Bashir, F.; Loan, S.A.; Rafat, M.; Alamoud, A.R.M.; Abbasi, S.A. A high performance gate engineered charge plasma based tunnel field effect transistor. *J. Comput. Electron.* **2015**, *14*, 477–485. [CrossRef]

- 18. Duan, X.; Zhang, J.; Wang, S.; Li, Y.; Xu, S.; Hao, Y. A High-Performance Gate Engineered InGaN Dopingless Tunnel FET. *IEEE Trans. Electron Devices* **2018**, *65*, 1223–1229. [CrossRef]

- 19. Abdi, D.B.; Kumar, M.J. PNPN tunnel FET with controllable drain side tunnel barrier width: Proposal and analysis. *Superlattices Microstruct.* 2015, *86*, 121–125. [CrossRef]

- 20. Sahay, S.; Kumar, M.J. Controlling the drain side tunneling width to reduce ambipolar current in tunnel FETs using heterodielectric BOX. *IEEE Trans. Electrons Devices* **2015**, *62*, 3882–3885. [CrossRef]

- 21. Li, W.; Sharmin, S.; Ilatikhameneh, H.; Rahman, R.; Lu, Y.; Wang, J.; Yan, X.; Seabaugh, A.; Klimeck, G.; Jena, D.; et al. Polarization-Engineered III-Nitride Heterojunction Tunnel Field-Effect Transistors. *IEEE J. Explor. Solid-State Comput. Devices Circuits* **2015**, *1*, 28–34. [CrossRef]

- 22. Li, W.; Cao, L.; Lund, C.; Keller, S.; Fay, P. Performance projection of III-nitride heterojunction nanowire tunneling field-effect transistors. *Phys. Status Solidi A* **2016**, *213*, 905–908. [CrossRef]

- Cho, M.S.; Kwon, R.H.; Seo, J.H.; Yoon, Y.J.; Jang, Y.I.; Won, C.H.; Kim, J.-G.; Lee, J.; Cho, S.; Lee, J.-H.; et al. Electrical performances of InN/GaN tunneling field-effect transistor. *J. Nanosci. Nanotechnol.* 2017, 17, 8355–8359. [CrossRef]

- Duan, X.; Zhang, J.; Wang, S.; Quan, R.; Hao, Y. Effect of graded InGaN drain region and 'In' fraction in InGaN channel on performances of InGaN tunnel field-effect transistor. *Superlattices Microstruct.* 2017, 112, 671–679. [CrossRef]

- 25. ATLAS Device Simulation Software, Silvaco Int.: Santa Clara, CA, USA, 2013.

- Duan, X.; Zhang, J.; Xiao, M.; Zhao, Y.; Ning, J.; Hao, Y. Groove-type channel enhancement-mode AlGaN/GaN MIS HEMT with combined polar and nonpolar AlGaN/GaN heterostructures. *Chin. Phys. B* 2016, 25, 087304. [CrossRef]

- 27. Verhulst, A.S.; Vandenberghe, W.G.; Maex, K.; Groeseneken, G. Boosting the on-current of a n-channel nanowire tunnel field-effect transistor by source material optimization. *J. Appl. Phys.* **2008**, *104*, 064514. [CrossRef]

- 28. Raad, B.R.; Sharma, D.; Kondekar, P.; Nigam, K.; Yadav, D.S. Drain work function engineered doping-less charge plasma TFET for ambipolar suppression and RF performance improvement: A proposal, design, and investigation. *IEEE Trans. Electron Devices* **2016**, *63*, 3950–3957. [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).