# Article Analysis of Threshold Voltage Shift for Full V<sub>GS</sub>/V<sub>DS</sub>/Oxygen-Content Span under Positive Bias Stress in Bottom-Gate Amorphous InGaZnO Thin-Film Transistors

Je-Hyuk Kim <sup>1</sup>, Jun Tae Jang <sup>1</sup>, Jong-Ho Bae <sup>1</sup>, Sung-Jin Choi <sup>1</sup>, Dong Myong Kim <sup>1</sup>, Changwook Kim <sup>2</sup>, Yoon Kim <sup>3,\*</sup> and Dae Hwan Kim <sup>1,2,\*</sup>

- <sup>1</sup> The School of Electrical Engineering, Kookmin University, Seoul 02707, Korea; jhyuck93@kookmin.ac.kr (J.-H.K.); jtjang@kookmin.ac.kr (J.T.J.); jbae@kookmin.ac.kr (J.-H.B.); sjchoiee@kookmin.ac.kr (S.-J.C.); dmkim@kookmin.ac.kr (D.M.K.)

- <sup>2</sup> Circadian ICT Research Center, Kookmin University, Seoul 02707, Korea; ncwkim@kookmin.ac.kr

- <sup>3</sup> The School of Electrical and Computer Engineering, University of Seoul, Seoul 02504, Korea

- Correspondence: yoonkim82@uos.ac.kr (Y.K.); drlife@kookmin.ac.kr (D.H.K.); Tel.: +82-2-6490-2352 (Y.K.); +82-2-910-4872 (D.H.K.)

**Abstract:** In this study, we analyzed the threshold voltage shift characteristics of bottom-gate amorphous indium-gallium-zinc-oxide (IGZO) thin-film transistors (TFTs) under a wide range of positive stress voltages. We investigated four mechanisms: electron trapping at the gate insulator layer by a vertical electric field, electron trapping at the drain-side GI layer by hot-carrier injection, hole trapping at the source-side etch-stop layer by impact ionization, and donor-like state creation in the drain-side IGZO layer by a lateral electric field. To accurately analyze each mechanism, the local threshold voltages of the source and drain sides were measured by forward and reverse read-out. By using contour maps of the threshold voltage shift, we investigated which mechanism was dominant in various gate and drain stress voltage pairs. In addition, we investigated the effect of the oxygen content of the IGZO layer on the positive stress-induced threshold voltage shift. For oxygen-rich devices and oxygen-poor devices, the threshold voltage shift as well as the change in the density of states were analyzed.

**Keywords:** indium-gallium-zinc-oxide thin-film transistors (-IGZO TFT); oxygen content; instability; electron trapping; hole trapping; donor-like state creation

# 1. Introduction

Amorphous InGaZnO (a-IGZO) thin-film transistors (TFTs) have made significant progress, particularly in display and mobile electronics, owing to their high mobility, high transparency to visible light, and low process temperatures [1–3]. The instability issues of a-IGZO TFTs have recently attracted significant attention. For the reliable incorporation of a-IGZO TFTs into the driving circuits for display application, it is crucial to understand the degradation mechanisms of the device under bias stresses. Many research groups have reported stress-induced instability characteristics [4–14]. Most of these studies have focused on the verification of degradation mechanisms, such as charge trapping, hole trapping, and donor-state creation. However, no studies have been reported that analyze the instability for a wide stress voltage region, including a very large gate or drain voltage. In addition, a thorough understanding of the effect of oxygen content in IGZO thin films on the degradation mechanisms under various stress conditions has not been reported.

In this study, we analyzed the change in threshold voltage ( $V_T$ ) in a-IGZO TFTs over a stress voltage range of 10–50 V. Local  $V_T$  shifts at the drain and source sides were measured by reverse and forward read-out conditions, respectively. In addition, we investigated the degradation mechanism by extracting the density of states (DOS) before and after stress. Further, the effect of different oxygen contents was analyzed by adjusting the oxygen

Citation: Kim, J.-H.; Jang, J.T.; Bae, J.-H.; Choi, S.-J.; Kim, D.M.; Kim, C.; Kim, Y.; Kim, D.H. Analysis of Threshold Voltage Shift for Full V<sub>GS</sub>/V<sub>DS</sub>/Oxygen-Content Span under Positive Bias Stress in Bottom-Gate Amorphous InGaZnO Thin-Film Transistors. *Micromachines* 2021, 12, 327. https://doi.org/ 10.3390/mi12030327

Academic Editor: Niall Tait

Received: 19 February 2021 Accepted: 16 March 2021 Published: 19 March 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). flow rate (OFR) in the deposition process of the IGZO layer on the positive stress-induced  $V_{\rm T}$  shift.

### 2. Device Sample Preparation

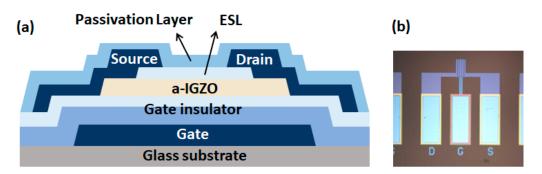

Figure 1 shows a schematic diagram of the bottom-gate a-IGZO TFT device structure. The width ( $W_{ch}$ ) and length of the device channel ( $L_{ch}$ ) were 100 and 15 µm, respectively. Key fabrication steps of the device are as follows:

The molybdenum (Mo) bottom gate was patterned on a glass substrate by room temperature (RT) sputtering. The gate insulator (GI) was formed with  $SiN_x$  and  $SiO_2$  using plasma-enhanced chemical vapor deposition (PE-CVD) on the bottom gate. The equivalent oxide thickness (EOT) of GI is 258 nm. The a-IGZO layer with a thickness of 50 nm was sputtered in an oxygen-argon atmosphere. Different devices—oxygen-poor (O-poor) and oxygen-rich (O-rich)—are fabricated in different OFRs by direct current (DC) sputtering at RT. O<sub>2</sub> flow rates of 21 and 63 sccm were used for the O-poor and O-rich devices, respectively. An Ar flow rate of 25 sccm was used for both the devices. After the deposition of the IGZO layer, the  $SiO_x$  etch-stop layer (ESL) and source and drain electrodes were patterned with Mo. Finally,  $SiO_x$  and  $SiN_x$  passivation layers were deposited, followed by annealing at 250 °C.

The electrical properties of the fabricated devices were measured in the dark at room temperature using an Agilent B1500A semiconductor parameter analyzer (Agilent Technologies, Santa Clara, CA, United States).

**Figure 1.** Amorphous InGaZnO (a-IGZO) thin-film transistor Sample: (**a**) Schematic structure of bottom-gate a-IGZO TFT device; (**b**) Top view of layout image.

# 3. Results and Discussion

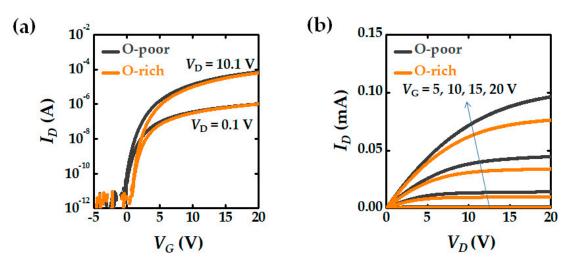

Mechanisms of stress-induced  $V_T$  shift in the fabricated a-IGZO TFTs were verified using I-V characteristics and monochromatic photonic C-V (MPCV) sub-gap DOS measurements [15–19]. Figure 2 indicates the transfer characteristics and output characteristics of pristine a-IGZO TFTs. After applying 10 s of stress at 25 different bias conditions with  $V_{GS}$ and  $V_{DS}$  bias matrices in the range of 10–50 V, contour of  $V_T$  shift ( $\Delta V_T$ ) is represented. A constant current method with a constant drain current ( $I_D = 10^{-8}$  A) was used to extract the  $V_T$ . To observe the  $V_T$  shift in the source and drain regions separately, a reverse and forward readout condition was used. In general, the threshold voltage of a transistor is determined by the region at which the barrier potential is high within the channel region. Since the barrier potential of the channel is low in the drain region where a relatively high voltage is applied, the threshold voltage of the transistor is determined not by the drain region, but by the source region where a relative low voltage is applied. Therefore, Forward read-out can measure source-side  $V_T$  by applying a higher bias at the drain side, and reverse read-out can measure drain-side  $V_T$  by switching the source and drain electrodes. Note that the forward read-out or reverse read-out measurements does not cause a  $V_T$  shift.

**Figure 2.** Current-voltage characteristics of IGZO TFT device: (**a**) Transfer characteristics of O-poor and O-rich devices; (**b**) Output characteristics of O-poor and O-rich devices.

#### 3.1. V<sub>T</sub> Shift Mechanisms

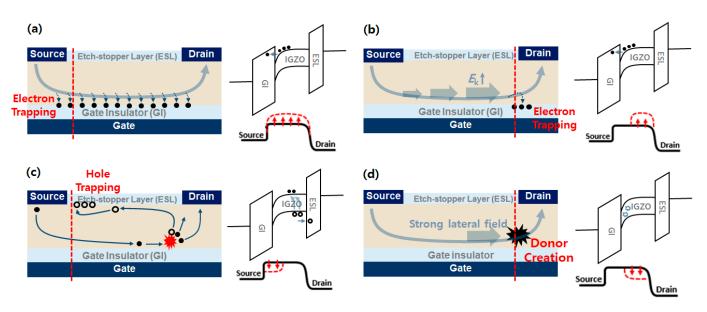

As shown in Figure 3,  $V_{\rm T}$  shift can occur by four different mechanisms in a-IGZO TFTs, as follows:

- 1. Electron trapping in the interface of bulk GI layer occurs by a vertical electric field (positive gate voltage), as shown in Figure 3a. This occurs throughout the entire channel area. However, when a high voltage is applied to the drain, it occurs more at the source-side interface because  $V_{\text{GS}} > V_{\text{GD}}$ . In this case, a positive  $V_{\text{T}}$  shift occurs owing to the screen effect of trapped electrons [6,20,21].

- Electron trapping at the drain-side GI layer occurs by hot-carrier injection (HCI), as shown in Figure 3b. HCI is one of the mechanisms that adversely affects the reliability of semiconductors. Electrons gain sufficient kinetic energy by a large lateral electric field to overcome a potential barrier between the IGZO channel and the GI [22]. These electrons can be trapped in the GI and also cause a positive V<sub>T</sub> shift of the device [13,23].

- 3. Hole trapping at the source-side ESL occurs via impact ionization, as shown in Figure 3c. This is also caused by the lateral electric field because of the highly applied drain bias, and electrons can get enough energy to give rise to impact ionization, and an electron-hole pair (EHP) is finally generated. The generated holes are trapped at the interface between the IGZO channel and ESL while drifting to the source side because of the absence of a path to exit (body electrode), which causes a potential increase in the channel, thus resulting in a negative  $V_{\rm T}$  shift [13].

- 4. Donor-like state creation in the drain-side IGZO layer occurs by a lateral electric field, as shown in Figure 3d. In general, oxygen vacancies in a-IGZO were found to act mostly as shallow donors. In some cases, a deep donor can be created through the creation of a metal-metal bond with an electronic property able to capture two electrons. Donor-like states originate from the impact ionization of oxygen vacancies in the IGZO layer (Vo + e<sup>-</sup>  $\rightarrow$  Vo<sup>2+</sup> + 3e<sup>-</sup>). These positively charged states result in a negative  $V_{\rm T}$  shift [13,24–27]. This mechanism is dominant near the drain side because the lateral electric field is higher than the source side.

**Figure 3.** Schematic structures and energy band diagrams of four different mechanisms of  $V_T$  shift in IGZO TFT device: (a) Electron trapping at the GI layer by vertical electric field; (b) Electron trapping at the drain-side GI layer by HCI; (c) Hole trapping at the source-side ESL by impact ionization; (d) Donor-like state creation in the drain-side IGZO layer by lateral electric field.

# 3.2. V<sub>T</sub> Shift Results

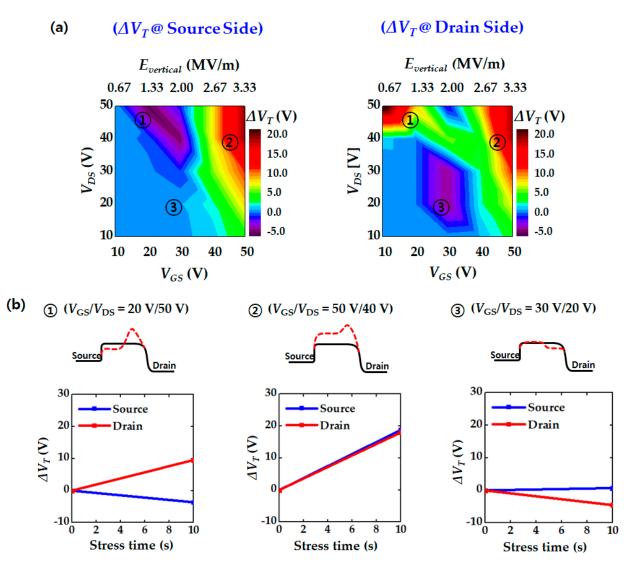

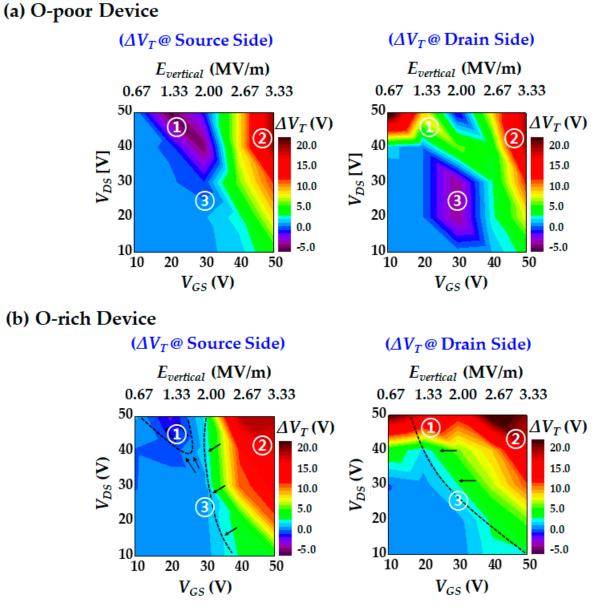

Figure 4a shows  $V_{\rm T}$  shift contour maps at the source and drain sides under various stress conditions ( $V_{\rm CS}$  and  $V_{\rm DS}$  biases). The  $V_{\rm T}$  change was observed after applying a stress bias for 10 s to the O-poor devices. This contour map helps to easily identify the  $V_{\rm T}$  instability characteristics for various stress bias ranges. Interestingly, three stress-bias regions with different  $V_{\rm T}$  shift trends were observed.

In the bias region of (1) with relatively low  $V_{\text{GS}}$  and high  $V_{\text{DS}}$  stress ( $V_{\text{GS}} = \sim 20$  V and  $V_{\text{DS}} = \sim 50$  V), a very high lateral electric field is applied; thus, impact ionization and HCI are the dominant mechanisms. Hole trapping at the source side occurs from EHP generation due to impact ionization and results in a negative  $V_{\text{T}}$  shift. On the other hand, electron trapping due to HCI causes a positive  $V_{\text{T}}$  shift at the drain side.

In the bias region of (2), a very high voltage was applied to the gate ( $V_{\text{CS}} = -50$  V). When a large vertical electric field is applied, electron trapping occurs in the entire GI region due to electron tunneling; thus, positive  $V_{\text{T}}$  shifts were observed at both sides. In addition, as the drain stress bias increased, HCI was generated. Consequently, more electron trapping and a larger  $V_{\text{T}}$  shift occurred.

Next, the bias condition of ③ with moderate stress voltages ( $V_{\text{GS}} = ~30$  V and  $V_{\text{DS}} = ~20$  V) causes different  $V_{\text{T}}$  shifts at the source and drain sides. A slightly negative  $V_{\text{T}}$  shift occurred at the drain side, while almost no  $V_{\text{T}}$  shift occurred at the source side. Under this stress condition, the creation of donor-like states near the drain side is a dominant  $V_{\text{T}}$ -shift mechanism.

Figure 4b shows the change in  $V_{\rm T}$  according to the stress time in each bias region. Schematic illustrations of the potential barrier modulation are also presented.

**Figure 4.**  $V_{\rm T}$  shift results after various stress bias (O-poor device case): (a) Contour maps of  $V_{\rm T}$  shift at source and drain side (forward and reverse read-out); (b)  $V_{\rm T}$  change as a function of stress time at three major bias regions with schematic illustration of barrier height modulation.

# 3.3. Effect of OFR on $V_T$ Instability

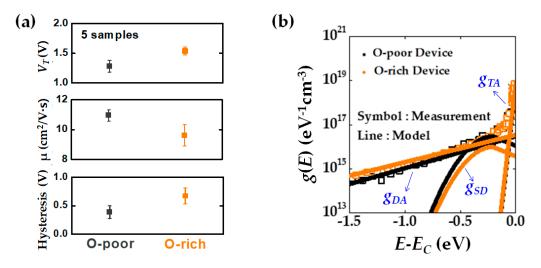

Next, the effect of OFR on the electrical characteristics of the a-IGZO TFT devices was observed. Figure 5a shows the pristine electrical characteristics of the O-poor and O-rich devices.

A high oxygen content results in a higher  $V_{\rm T}$ . This is because the number of oxygen vacancies, which act as shallow donors, decreases. As the oxygen content increases, the number of electron traps generated by the diffusion of oxygen into the GI increases [28–30]. Consequently, devices with a higher OFR have lower carrier mobility and a low mean free path. In addition, O-rich devices cause greater hysteresis than O-poor devices. Here, the hysteresis is defined as the difference in  $V_{\rm T}$  between the  $V_{\rm GS}$  sweep from 20 to -20 V and that from -20 to 20 V. Large hysteresis indicates many electrons trapped in the GI and GI/IGZO interfaces.

The experimentally extracted DOS in the IGZO layers are shown in Figure 5b. The DOS was extracted using the MPCV measurement method based on the photoresponsive C-V characteristics in the subgap energy range ( $E_V < E < E_C$ ). The detailed methodology was described in our previous work [17]. Capacitance was measured by a LCR meter (HP4284A) using a 50 kHz AC signal. A 5 mW illumination source with a photon energy

of 2.8 eV was used. The extracted DOS (g(E)) near the conduction band were modeled to be a superposition of three components: 1. shallow donor-like states ( $g_{SD}$ ), 2. acceptor-like deep states ( $g_{DA}$ ), 3. acceptor-like tail states ( $g_{TA}$ ). Each DOS was modeled according to Equation (1):

$$g(E) = g_{TA}(E) + g_{DA}(E) + g_{SD}(E)$$

=  $N_{TA} \exp\left(-\frac{E_C - E}{kT_{TA}}\right) + N_{DA} \exp\left(-\frac{E_C - E}{kT_{DA}}\right) + N_{SD} \exp\left(-\left(\frac{E_C - E - E_{SD}}{kT_{SD}}\right)^2\right)$  (1)

where  $E_{SD}$  denotes a center energy of the Gaussian peak.

The O-rich device has a higher DOS near the conduction band edge ( $E_C$ ), which means that they have more electron traps, as mentioned above.

**Figure 5.** Characteristic comparisons between O-poor and O-rich a-IGZO devices: (a) Electrical characteristics (threshold voltage, mobility, and hysteresis) of O-poor and O-rich devices; (b) Experimentally extracted DOS distributions of two devices by using MPCV method. Black and orange symbols indicate O-poor and O-rich device, respectively.

Figure 6 shows the contour maps of the  $V_T$  shift after 10 s of stress applied to the gate and drain electrodes. The two graphs in Figure 6a are  $\Delta V_T$  of the O-poor device and the others in Figure 6b are those of the O-rich device. The left graphs are  $\Delta V_T$  at the source side, and the right graphs are those at the drain side. Compared with the O-poor device, the O-rich device exhibited the following changes in each stress bias region (1), (2) and (3).

In the O-rich device, hole trapping at the source side and electron trapping at the drain side caused by impact ionization in the bias region of ① are reduced. This can be interpreted as electrons of the O-rich device struggle to obtain sufficient kinetic energy to cause impact ionization due to poor carrier mobility and small mean free path.

In addition, O-rich devices have more traps inside the bulk GI and at the interface of GI/IGZO, so more electrons can be trapped for the same gate stress voltage. Thus, the bias region of (2), where the electron trapping by the vertical electric field is the dominant mechanism, is extended, as can be seen in Figure 6b. In addition, it should be noted that the self-heating effect also affects the electron density trapped at the interface and bulk GI layer. Under the same operation voltages, the drain current of the O-poor device is larger than that of the O-rich device as can be seen in Figure 2, and thus the Joule heating is also larger. Consequently, the O-poor device generates more self-heating-assisted e-trapping [30]. Nevertheless, the fact that the  $V_{\rm T}$  shift of the O-rich devices is larger than that of the O-poor device indicates that the mechanism of electron trapping at the GI layer by the vertical electric field is dominated by the trap density rather than by the self-heating effect.

Figure 6. V<sub>T</sub> shift results after various stress bias: (a) O-poor device characteristic; (b) O-rich device characteristic.

Finally, in the case of the O-rich device, the donor-like state creation at the drain side under the bias region of ③ is significantly reduced. This result can be interpreted in a similar way to the bias region of ①. As mentioned earlier, the O-rich device has lower carrier mobility and smaller mean free path. Consequently, the number of electrons that obtain sufficient kinetic energy to cause impact ionization of oxygen vacancies in the O-rich device is smaller than that in the O-poor.

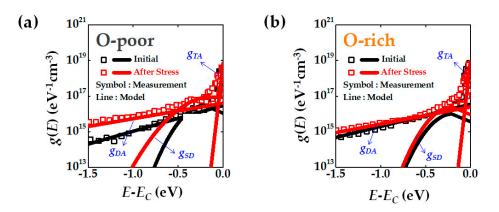

To further analyze this, DOS was extracted before and after applying the stress bias of region ③ ( $V_{GS} = 30$  V and  $V_{DS} = 20$  V), as shown in Figure 7. The O-poor device exhibits an increase in the donor-like state( $g_{SD}$ ) after stress, whereas the increase in the donor-like state of the O-rich device is relatively small, as seen in Figure 7b.

**Figure 7.** Extracted DOS distributions before and after stress: (**a**) The DOS change of O-poor device; (**b**) The DOS change of O-rich device.

# 4. Conclusions

In this study, the characteristics of the  $V_{\rm T}$  shift caused by various positive stress voltages were investigated. For various gate and drain stress voltage pairs ( $V_{\rm DS}/V_{\rm DS} = 10~50$  V), local  $V_{\rm T}$ s at the source and drain sides were observed. In particular, we classified three stress bias regions using contour maps of the  $V_{\rm T}$  shift. In the bias region with relatively low  $V_{\rm GS}$  and high  $V_{\rm DS}$  stress, electron trapping at the drain-side GI layer, and hole trapping at the source-side ESL are the dominant mechanisms. In the bias region under a high gate voltage, electron trapping predominately occurs at the GI layer by the vertical electric field. In the bias region with moderate stress voltages ( $V_{\rm GS} = ~30$  V and  $V_{\rm DS} = ~20$  V), donor-like state creation in the drain-side IGZO layer is the dominant mechanism. In addition, we analyzed the effect of the oxygen content of the IGZO layer on each  $V_{\rm T}$  shift mechanism. Our instability analysis for a wide stress voltage can provide useful information when determining deterioration acceleration conditions for the purpose of reliability testing or when dealing with new applications that require a large operation voltage.

**Author Contributions:** Conceptualization, J.-H.K. and D.H.K.; formal analysis, J.-H.K. and J.T.J.; investigation, J.-H.K. and Y.K.; methodology, J.-H.K., J.-H.B., S.-J.C., D.M.K., C.K., and D.H.K.; writing—original draft J.-H.K. and Y.K.; writing—review and editing, D.H.K. and Y.K. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was supported by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science and ICT (MSIT) of Korea under Grant (2020R1C1C1009006, 2016R1A5A1012966, 2020R1A2B5B01001979).

Acknowledgments: The CAD software was supported by SILVACO and IDEC.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. *Sci. Technol. Adv. Mater.* 2010, 11, 1–23. [CrossRef]

- 2. Kamiya, T.; Hiramatsu, H.; Nomura, K.; Hosono, H. Device applications of transparent oxide semiconductors: Excitonic blue LED and transparent flexible TFT. *J. Electroceram* **2006**, *17*, 267–275. [CrossRef]

- Lin, C.-L.; Chang, W.-Y.; Hung, C.-C. Compensating Pixel Circuit Driving AMOLED Display With a-IGZO TFTs. *IEEE Electron* Device Lett. 2013, 34, 1166–1168. [CrossRef]

- 4. Yen, C.-C.; Tai, A.-H.; Liu, Y.-U.; Chen, T.-L.; Chou, C.-H.; Liu, C.W. Oxygen-Related Reliability of Amorphous InGaZnO Thin Film Transistors. *IEEE J. Electron Devices Soc.* 2020, *8*, 540–544. [CrossRef]

- 5. Lee, D.; Jeong, C.-Y.; Song, S.-H.; Xiao-Shi, J.; Kim, J.I.; Lee, J.-H.; Kwon, H.-I. Asymmetrical degradation behaviors in amorphous InGaZnO thin-film transistors under various gate and drain bias stresses. *J. Vac. Sci. Technol. B* **2014**, *33*, 011202. [CrossRef]

- 6. Cho, I.-T.; Lee, J.-M.; Lee, J.-H.; Kwon, H.-I. Charge trapping and detrapping characteristics in amorphous InGaZnO TFTs under static and dynamic stresses. *Semicond. Sci. Technol.* **2008**, *24*, 015013. [CrossRef]

- 7. On, N.; Kim, K.; Lee, S.; Kim, E.H.; Lim, J.H.; Jeong, J.K. Hot Carrier Effect in Self-Aligned In–Ga–Zn–O Thin-Film Transistors With Short Channel Length. *IEEE Trans. Electron Devices* **2020**, *67*, 5544–5551. [CrossRef]

- 8. Takahashi, T.; Miyanaga, R.; Fujii, M.N.; Tanaka, J.; Takechi, K.; Tanabe, H.; Bermudo, J.P.; Ishikawa, Y.; Uraoka, Y. Hot carrier effects in InGaZnO thin-film transistor. *Appl. Phys. Express* 2019, *12*, 094007. [CrossRef]

- Kim, J.I.; Jeong, C.-Y.; Kwon, H.-I.; Jung, K.D.; Park, M.S.; Kim, K.H.; Seo, M.S.; Lee, J.-H. Modeling of asymmetric degradation based on a non-uniform electric field and temperature in amorphous In-Ga-Zn-O thin film transistors. *Semicond. Sci. Technol.* 2017, 32, 035017. [CrossRef]

- Lin, D.; Su, W.-C.; Chang, T.-C.; Chen, H.-C.; Tu, Y.-F.; Zhou, K.-J.; Hung, Y.-H.; Yang, J.; Lu, I.-N.; Tsai, T.-M.; et al. Degradation Behavior of Etch-Stopper-Layer Structured a-InGaZnO Thin-Film Transistors under Hot-Carrier Stress and Illumination. *IEEE Trans. Electron Devices* 2021, 68, 556–559. [CrossRef]

- Kim, J.; Choi, S.; Jang, J.; Jang, J.T.; Kim, J.; Choi, S.-J.; Kim, D.M.; Kim, D.H. Analysis of Instability Mechanism under Simultaneous Positive Gate and Drain Bias Stress in Self-Aligned Top- Gate Amorphous Indium-Zinc-Oxide Thin-Film. *J. Semicond. Technol. Sci.* 2015, 15, 526–531. [CrossRef]

- 12. Abe, K.; Takahashi, K.; Sato, A.; Kumomi, H.; Nomura, K.; Kamiya, T.; Kanicki, J.; Hosono, H. Amorphous In–Ga–Zn–O Dual-Gate TFTs: Current–Voltage Characteristics and Electrical Stress Instabilities. *IEEE Trans. Electron Devices* **2012**, *59*, 1336–1339. [CrossRef]

- 13. Urakawa, S.; Tomai, S.; Ueoka, Y.; Yamazaki, H.; Kasami, M.; Yano, K.; Wang, D.; Furuta, M.; Horita, M.; Ishikawa, Y.; et al. Thermal analysis of amorphous oxide thin film transistor degraded by combination of joule heating and hot carrier effect. *Appl. Phys. Lett.* **2013**, *102*, 053506. [CrossRef]

- 14. Choi, S.-H.; Han, M.-K. Effect of channel widths on negative shift of threshold voltage, including stress-induced hump phenomenon in InGaZnO thin-film transistors under high-gate and drain bias stress. *Appl. Phys. Lett.* **2012**, *100*, 043503. [CrossRef]

- Jeon, K.; Kim, C.; Song, I.; Park, J.; Kim, S.; Kim, S.; Park, Y.; Park, J.-H.; Lee, S.; Kim, D.M.; et al. Modeling of amorphous InGaZnO thin-film transistors based on the density of states extracted from the optical response of capacitance-voltage characteristics. *Appl. Phys. Lett.* 2008, 93, 182102. [CrossRef]

- Park, J.-H.; Jeon, K.; Lee, S.; Kim, S.; Kim, S.; Song, I.; Kim, C.J.; Park, J.; Park, Y.; Kim, D.M.; et al. Extraction of Density of States in Amorphous GaInZnO Thin-Film Transistors by Combining an Optical Charge Pumping and Capacitance–Voltage Characteristics. *IEEE Electron Device Lett.* 2008, 29, 1292–1295. [CrossRef]

- 17. Bae, H.; Choi, H.; Jun, S.; Jo, C.; Kim, Y.H.; Hwang, J.S.; Ahn, J.; Oh, S.; Bae, J.-U.; Choi, S.-J.; et al. Single-Scan Monochromatic Photonic Capacitance-Voltage Technique for Extraction of Subgap DOS Over the Bandgap in Amorphous Semiconductor TFTs. *IEEE Electron Device Lett.* 2013, *34*, 1524–1526. [CrossRef]

- Choi, S.; Jang, J.T.; Kang, H.; Baeck, J.H.; Bae, J.U.; Park, K.-S.; Yoon, S.Y.; Kang, I.B.; Kim, D.M.; Choi, S.-J.; et al. Systematic Decomposition of the Positive Bias Stress Instability in Self-Aligned Coplanar InGaZnO Thin-Film Transistors. *IEEE Electron* Device Lett. 2017, 38, 580–583. [CrossRef]

- 19. Jang, J.T.; Choi, S.-J.; Kim, D.M.; Kim, D.H. The Calculation of Negative Bias Illumination Stress-Induced Instability of Amorphous InGaZnO Thin-Film Transistors for Instability-Aware Design. *IEEE Trans. Electron Devices* **2018**, *65*, 1002–1008. [CrossRef]

- 20. Zhou, Y.; Dong, C. Influence of Passivation Layers on Positive Gate Bias-Stress Stability of Amorphous InGaZnO Thin-Film Transistors. *Micromachines* **2018**, *9*, 603. [CrossRef]

- 21. Lee, J.-M.; Cho, I.-T.; Lee, J.-H.; Kwon, H.-I. Bias-stress-induced stretched-exponential time dependence of threshold voltage shift in InGaZnO thin film transistors. *Appl. Phys. Lett.* **2008**, *93*, 093504. [CrossRef]

- 22. Chen, B.-W.; Chang, T.-C.; Hung, Y.-J.; Hsieh, T.-Y.; Tsai, M.-Y.; Liao, P.-Y.; Tsai, W.-W.; Chiang, W.-J.; Yan, J.-Y. Investigation of temperature-dependent asymmetric degradation behavior induced by hot carrier effect in oxygen ambiance in In–Ga–Zn-O thin film transistors. *Thin Solid Films* **2014**, *572*, 33–38. [CrossRef]

- Choi, S.; Kim, H.; Jo, C.; Kim, H.-S.; Choi, S.-J.; Kim, D.M.; Park, J.; Kim, D.H. The Effect of Gate and Drain Fields on theCompetition Between Donor-Like State Creation and Local Electron Trapping in In–Ga–Zn–O Thin Film Transistors under Current Stress. *IEEE Electron Device Lett.* 2015, *36*, 1336–1339. [CrossRef]

- 24. Kim, J.I.; Cho, I.-T.; Joe, S.-M.; Jeong, C.-Y.; Lee, D.; Kwon, H.-I. Effect of Temperature and Electric Field on Degradation in Amorphous InGaZnO TFTs under Positive Gate and Drain Bias Stress. *IEEE Electron Device Lett.* **2014**, *35*, 458–460. [CrossRef]

- Choi, S.; Kim, H.; Jo, C.; Kim, H.-S.; Choi, S.-J.; Kim, D.M.; Kim, D.H. A Study on the Degradation of In–Ga–Zn–O Thin-Film Transistors under Current Stress by Local Variations in Density of States and Trapped Charge Distribution. *IEEE Electron Device Lett.* 2015, *36*, 690–692. [CrossRef]

- 26. Lee, S.M.; Cho, W.-J.; Park, J.T. Device Instability under High Gate and Drain Biases in InGaZnO Thin Film Transistors. *IEEE Trans. Decive Mater. Reliab.* **2014**, *14*, 471–476. [CrossRef]

- 27. Fung, T.-C.; Chuang, C.-S.; Chen, C.; Abe, K.; Cottle, R.; Townsend, M.; Kumomi, H.; Kanicki, J. Two-dimensional numerical simulation of radio frequency sputter amorphous In–Ga–Zn–O thin-film transistors. J. Appl. Phys. 2009, 106, 084511. [CrossRef]

- Kim, S.; Jeon, Y.W.; Kim, Y.; Kong, D.; Jung, H.K.; Bae, M.-K.; Lee, J.-H.; Ahn, B.D.; Park, S.Y.; Park, J.-H.; et al. Impact of Oxygen Flow Rate on the Instability under Positive Bias Stresses DC-Sputtered Amorphous InGaZnO Thin-Film Transistors. *IEEE Electron Device Lett.* 2012, 33, 62–64. [CrossRef]

- 29. Chiang, H.Q.; McFarlane, B.R.; Hong, D.; Presley, R.E.; Wager, J.F. Processing effects on the stability of amorphous indium gallium zinc oxide thin-film transistors. *J. Non-Cryst. Solids* **2008**, *354*, 2826–2830. [CrossRef]

- 30. Choi, S.; Kim, J.-Y.; Kang, H.; Ko, D.; Rhee, J.; Choi, S.-J.; Kim, D.M.; Kim, D.H. Effect of Oxygen Content on Current Stress-Induced Instability in Bottom-Gate Amorphous InGaZnO Thin-Film Transistors. *Materials* **2019**, *12*, 3149. [CrossRef]