Communication

# Exploration of a Novel Electric-Fuse Device with a Simple Structure of Ni Metal on a SiO<sub>2</sub> Dielectric for Electrostatic Discharge Protection under a Human Body Model

He Guan<sup>1,\*</sup>, Jiaying Li<sup>1</sup>, Yangchao Chen<sup>1</sup>, Yongchuan Tang<sup>1,2</sup> and Yunshuo Li<sup>1</sup>

- <sup>1</sup> School of Microelectronics, Northwestern Polytechnical University, Xi'an 710072, China; 2020302234@mail.nwpu.edu.cn (J.L.); chenyangchao@mail.nwpu.edu.cn (Y.C.); tangyongchuan@nwpu.edu.cn (Y.T.); 2016301981@mail.nwpu.edu.cn (Y.L.)

- <sup>2</sup> Chongqing Innovation Center, Northwestern Polytechnical University, Chongqing 401135, China

- Correspondence: he.guan@nwpu.edu.cn

**Abstract:** On-chip electrostatic discharge (ESD) protection poses a challenge in the chip fabrication process. In this study, a novel electric fuse (E-fuse) device featuring a simple structure of Ni metal on a SiO<sub>2</sub> dielectric for ESD protection was proposed, and the physical mechanism of its operation was investigated in detail. Experimental evaluations, utilizing transmission line pulse (TLP) testing and fusing performance analyses, reveal that the E-fuse, constructed with a Ni metal layer measuring 5  $\mu$ m in width, 100  $\mu$ m in length, and 5 nm in thickness, achieved a significant ESD protection voltage of 251 V (*V*<sub>HBM</sub>) and demonstrates low-voltage fusing at a bias voltage of 7 V. Compared to traditional ESD protection devices, the E-fuse boasts a smaller size and removability. To assess fusing performance, devices of varying sizes were tested using a fusing lifetime model. This study supports both theoretical and empirical evidence, enabling the adoption of cost-effective, straightforward E-fuse devices for ESD protection.

Keywords: electrostatic discharge; electric fuse; transmission line pulse

## 1. Introduction

As chip processes are reduced, they become more susceptible to ESD. ESD can occur throughout the entire chip manufacturing process, including during the preparation, packaging, and shipping stages of integrated circuits (ICs). This can damage sensitive components and interfere with their operation, resulting in reduced chip performance or even failure. Therefore, ESD protection is receiving increasing attention as an important aspect of chip reliability [1–3].

ESD protection can be divided into off-chip and on-chip ESD protection according to different protection positions. Off-chip ESD protection devices are mainly Ceramic Capacitors, Zener Diodes, Schottky Diodes, Multi-Layer Varistor (MLV) and Transient Voltage Suppressors (TVSs) [4–8], which are generally placed in the peripheral circuits of the chip. However, off-chip ESD protection devices are difficult to integrate and cannot meet the miniaturization requirements. On-chip ESD protection devices are mainly diodes, Gate-Grounded NMOS (GG-NMOS), and Silicon Controlled Rectifier (SCR) [9–11]. Compared to off-chip ESD protection circuits, on-chip ESD protection circuits can directly and significantly enhance ESD protection, save board space, reduce system costs, and decrease design and wiring complexity. However, this inevitably introduces parasitic parameters and increases layout complexity. In 2014, Kuhn et al. proposed the use of E-fuse devices for ESD protection, providing new ideas for on-chip ESD protection [12]. Compared with traditional on-chip ESD protection devices, E-fuse protection devices have the advantages of small size, low parasitic parameters, and removability, making them very suitable for one-time electrostatic protection in the chip manufacturing process [13].

**Citation:** Guan, H.; Li, J.; Chen, Y.; Tang, Y.; Li, Y. Exploration of a Novel Electric-Fuse Device with a Simple Structure of Ni Metal on a SiO<sub>2</sub> Dielectric for Electrostatic Discharge Protection under a Human Body Model. *Micromachines* **2024**, *15*, 1163. https://doi.org/10.3390/mi15091163

Academic Editor: Mohammed Mabrook

Received: 1 September 2024 Revised: 10 September 2024 Accepted: 17 September 2024 Published: 19 September 2024

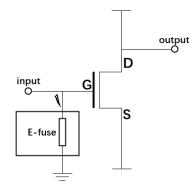

**Copyright:** © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). Based on this background, this paper presents an improved E-fuse ESD protection device with a simpler structure. The device includes a nano-scale Ni metal layer lithographically covered on the  $SiO_2$  dielectric layer, which is very easy to integrate onto the surface of any semiconductor device through a semiconductor device process to realize on-chip ESD protection. As an illustration example, as shown in Figure 1, the E-fuse device could be connected to the gate of the MOSFET devices for ESD protection. When high-voltage static electricity is generated during the operation, the E-fuse device is used to discharge the accidental static electricity in order to protect the gate of the MOSFET device from ESD damage. It is noted that, when a continuous low-voltage is added, the E-fuse device will be fused off by electromigration and will not affect the working performance of the MOSFET. This means that the protection device can be easily removed, reducing the impact on the internal circuitry.

Figure 1. The circuit diagram of the E-fuse device applied in MOSFET.

The specific studies in this paper are as follows. Firstly, the design structure and manufacturing process of the E-fuse device are introduced, and the working physical mechanism is investigated in detail. Among the various types of electrostatic discharges, human body electrostatic damage is a significant component of chip electrostatic damage, posing a significant threat to semiconductor devices [14]. Therefore, the TLP test, which is considered to be the typical evaluation measurement of an ESD human body model (HBM), is applied to the device to characterize the ESD performance. In addition, a fusing experimental test was conducted on the device, the fusing lifetime model was discussed based on devices with various sizes, and a detailed analysis of the results was performed. The test results show that the prepared E-fuse device, with a length of 100  $\mu$ m, a width of 5  $\mu$ m, and a thickness of 5 nm, had an ESD protection voltage of 251 V and achieved low-voltage fusing at a bias voltage of 7 V.

#### 2. Device Preparation

## 2.1. Structural Design

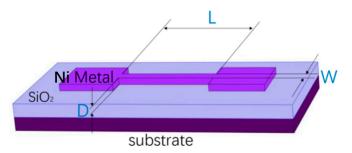

The E-fuse protection device was designed as shown in Figure 2. Based on the substrate (Si, as the most common semiconductor, was selected in this paper), a SiO<sub>2</sub> dielectric layer with 200 nm thickness is deposited. Above the dielectric, Ni metal was chosen for use as the E-fuse part because of its high strength, corrosion resistance, heat resistance, and good conductivity [15]. The length, width, and thickness of the E-fuse are represented as *L*, *W*, and *D*, respectively. The rectangular parts on the left and right sides of the thin E-fuse are metal electrodes for convenient testing. Obviously, E-fuse devices prepared with pure Ni metal are much simpler and easier to integrate compared to conventional ESD protection devices.

Figure 2. Structural diagram of the E-fuse device.

#### 2.2. Preparation and Characterization

The device is fabricated using nanoscale semiconductor technology with the following steps: (1) Cleaning of wafers [16]. The wafer samples are placed in a beaker with acetone and then isopropyl alcohol (IPA) is added. All organic solvents are subjected to an ultrasonic water bath to remove organic contaminants from the sample surface. The samples are then rinsed with deionized water and dried with a nitrogen gun to complete the cleaning procedure [17]. (2) Deposition of polysilicon [18]. A 200 nm silicon dioxide dielectric layer is deposited on the wafer using a low-pressure chemical vapor deposition (LPCVD) process [19]. (3) Preparation of E-fuse devices [20–22].

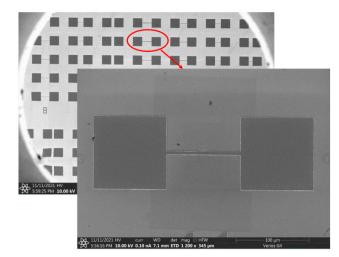

The preparation process follows the order of adhesive coating, electron beam lithography (EBL), development, and metal thermal vapor deposition. First, the photoresist is uniformly spin-coated on the sample surfaces. Next, EBL is performed. The sample is placed in the photolithography equipment and the mask is aligned. After the pattern on the mask has been aligned, the sample is brought into contact with the mask, the photoresist is exposed to UV light, and the sample is immersed in deionized water to remove the conductive adhesive. Development is then performed. The sample is immersed in the developer (4-Methyl-2-pentanone and IPA), and then washed and dried with isopropanol and N<sub>2</sub>. O<sub>2</sub> plasma is used to remove residual rubber backing from the sample surface. Finally, metal thermal evaporation is performed. Metals are deposited using an electron beam metal evaporator. Then, the samples are placed in acetone and sonicated, followed by immersion in a mixture of acetone and IPA to complete the metal stripping. The sample is re-immersed in deionized water and an ultrasonic water bath, and then dried with N<sub>2</sub>. The image of the prepared device as viewed through a scanning electron microscope (SEM) is shown in Figure 3.

Figure 3. E-fuse device under SEM test.

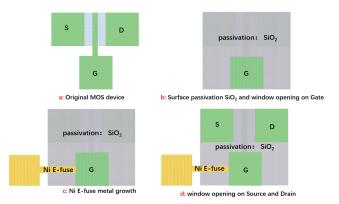

In practice, the process of this device is also very simple. For the application shown in Figure 3, as the example, the layout diagram is as shown in Figure 4. It requires three

simple steps for surface passivation with SiO<sub>2</sub> and window opening on the gate, Ni E-fuse metal deposition, and window opening on source and drain.

**Figure 4.** The illustration and diagram of the process and layout of the E-fuse device applied in MOSFET, where G, S, and D denote the gate, source, and drain of the MOSFET, respectively.

#### 3. Testing and Analysis

## 3.1. TLP Test

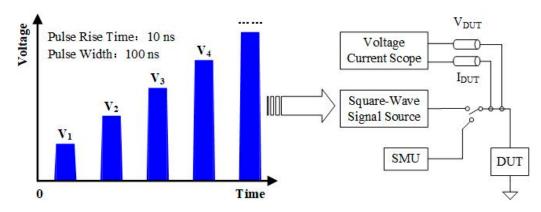

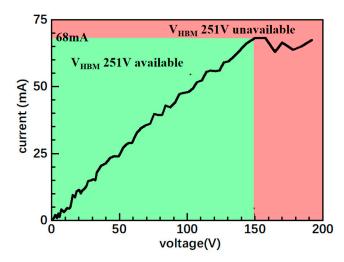

The TLP test was applied on a sample with a Ni E-fuse metal length L of 100  $\mu$ m, width W of 5  $\mu$ m, and thickness D of 5 nm to simulate the HBM. The TLP test procedure is shown in Figure 5. By gradually applying increasing voltage pulses to both ends of the device under test (DUT) and recording the voltage across the DUT and the current flowing through it under each pulse, the TLP test curve of the DUT can be obtained. Typically, the rise time of the voltage pulse applied for the TLP test is 10 ns and the pulse width is 100 ns [23,24]. Figure 6 illustrates the TLP test results; when the pulse voltage across the device is less than 149 V and the current is less than 68 mA, the TLP test curve of the device has an approximately constant slope, which is consistent with the normal leakage current characteristics of E-fuse devices. At this stage, the E-fuse resistance R<sub>on</sub> can be calculated to be approximately 2191  $\Omega$ . When the voltage rises above 149 V and the current exceeds 68 mA, the resistance of the device rises sharply, indicating that the device is damaged by the current generated during the TLP test. During this period, the secondary thermal escape current ( $I_{t2}$ ) can reach as high as 68 mA. Since the E-fuse resistance is significant, the protection voltage calculation equation is expanded so that Equation (1) [25] can be obtained, in which 1500 represents the equivalent resistance of the human body in the HBM. The final protection voltage  $V_{HBM}$  of the device was calculated to be 251 V, which is higher than that of similar devices [26,27]. To further enhance the  $V_{HBM}$  values, the current density can be reduced by increasing the size of the E-fuse device, which results in a larger  $I_{t2}$  and  $V_{HBM}$ .

$$V_{HBM} = (1500 + R_{on}) \times I_{t2} \tag{1}$$

Figure 5. TLP block diagram.

Figure 6. E-fuse device TLP test results.

#### 3.2. Fusing Test

After completing the TLP test, a fusing test was performed to demonstrate that the device could be successfully removed. Unlike the TLP test, which applies a continuously increasing pulse voltage, the fusing test applies a constant voltage across the device terminals until the device fails, and the corresponding fusing time is recorded. The fusing mechanism of the E-fuse device can be explained by electromigration, and the corresponding mechanism is described as follows. Under the continuous application of a certain voltage, the E-fuse will fuse due to electromigration. The physical theory of electromigration can be explained as follows. Under the influence of the current, metal atoms are displaced, leading to the formation of cavities in some areas of the metal. Similarly, other areas develop crystal hills due to the accumulation of metal atoms piled up on the surface or within the metal [28,29]. The electrons in the metal gain high speed under the influence of the electric current, and these high-speed electrons collide with the metal atoms. Through these collisions, the metal atoms gain momentum, leading to their acceleration. This movement of metal atoms, driven by what is known as electron wind force, is also influenced by the electrostatic field. However, when the current density in the circuit is high, electrons diffuse toward the anode under the current density's action. The resulting electron wind force becomes greater than the electrostatic field force. Therefore, under the combined influence of the electron wind force and the electrostatic field, metal atoms undergo directional diffusion from the cathode to the anode. The accumulation of the directional motion of metal atoms at the microscopic level results in metal fusion, causing the current to drop to 0 [30-32].

Electromigration is a complex process, involving several physical and chemical factors. Therefore, it is necessary to comprehensively consider various factors in practical applications to evaluate the performance and reliability of the E-fuse. To analyze the effect of E-fuse sizes and metal materials on the fusing performance of the device, we manufactured different E-fuses with various lengths and widths, and applied different voltages to both ends of the device for fusing tests.. The fusing test results, such as fusing time and fusing voltage, are shown in Table 1. It is obvious that at higher DC voltages, E-fuse devices of the same size have a shorter fusing time. Therefore, in specific applications, the fusing time can be changed by adjusting the size of the device to meet different application scenarios.

Here, Black's equation [33] is used as a model for evaluating the fusing performance of E-fuse devices at different sizes, as shown in Equation (2).

$$MTTF = A \times J^{-n} \times Exp\left(\frac{E_a}{k_b \times T}\right)$$

<sup>(2)</sup>

where *MTTF* refers to the electromigration lifetime, specifically the mean time to failure; A and n are constants related to the material, conductor geometry, and current distribution; J refers to the current density when the device fuses; *Ea* represents the activation energy of electromigration, which is a characteristic of the material and indicates the energy barrier that needs to be overcome during the electromigration process;  $k_b$  is Boltzmann's constant; and T refers to the absolute temperature.

| D/[nm] | L/[µm] | W/[µm] | Fusing<br>Voltage/[V] | Fusing<br>Time/[s] | Fusing<br>Resistance/[Ω] | Fusing<br>J/[mA/µm <sup>2</sup> ] |

|--------|--------|--------|-----------------------|--------------------|--------------------------|-----------------------------------|

| 50     | 100    | 5      | 7                     | 47.17              | 3200                     | 61.25                             |

| 50     | 30     | 3      | 4.5                   | 11.22              | 1600                     | 84.38                             |

| 50     | 30     | 3      | 5                     | 10.76              | 1600                     | 104.17                            |

| 50     | 25     | 5      | 5                     | 3.57               | 800                      | 125                               |

| 50     | 25     | 5      | 6                     | 2.1                | 800                      | 180                               |

Table 1. Fusing test results with various e-fuse sizes and metal materials.

The equation indicates that a higher current density will increase the collision frequency between electrons and metal atoms, thereby accelerating the electromigration process. Consequently, the E-fuse device may be more prone to fusing off under higher current densities, meaning that *MTTF* is inversely proportional to *J*. In Table 1, the fusing current density *J* can be calculated through the E-fuse size and fusing voltage. It is found that the fusing time of devices with different sizes is inversely proportional to their current density. Therefore, the fusing time trend of the devices is consistent with the *MTTF* indicated in the model formula; that is, the larger the *MTTF* is, the longer the fusing time is. However, it is assumed here that the temperature is constant. In practice, according to Joule's law, the current flowing through the E-fuse device will inevitably generate heat, which will have some effect on the *MTTF*. Therefore, in subsequent work, the effect of temperature on *MTTF* will also be considered as much as possible.

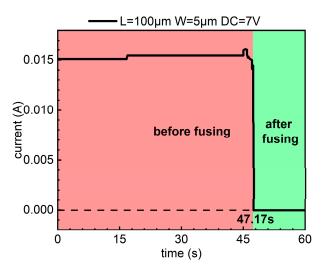

The device with a Ni metal length of 100  $\mu$ m, a width of 5  $\mu$ m, and a thickness of 5 nm, which was selected to illustrate ESD test above, presents a fusing performance as shown in Figure 7. It is found that the device is blown under a 7 V voltage in approximately 47.17 s. It is indicated that the devices exhibit low-voltage fusibility. The specific application of the fusing phenomenon is that after the circuit assembly has been completed, the fuse element is blown by an externally applied low DC voltage to finalize the circuit configuration. Disabling or triggering the ESD circuit in this manner will not cause any damage to the protected device. This E-fuse device is a competitive solution for low-cost and reliable on-chip ESD protection requirements.

Figure 7. Fusing test results of the device.

Further tests show that the E-fuse device generates a capacitance of about 40 pF after fusing, primarily due to the parasitic effects of preparing the device directly on the Si substrate for testing purposes. Although this capacitance is equivalent to that of a conventional DC isolation capacitor, its self-resonance frequency is high, which affects high-frequency signals but has less of an impact on most low-frequency analog and digital circuits. In practice, E-fuse devices can be fabricated on layers other than the substrate to reduce the impact of parasitic effects. We will continue to improve the device fabrication process to reduce the parasitic capacitance generated after fusing, thereby expanding the application areas of E-fuse protection devices. Furthermore, we will continue our research on improving the E-fuse ESD structure by optimizing its size, metal composition, and fabrication process, aiming to achieve lower resistance and higher voltage ratings for future high-level HBM standard applications.

## 4. Conclusions

In conclusion, this study has successfully demonstrated the potential of an innovative  $SiO_2$ -Ni electrical fuse device as an effective on-chip ESD protection solution. Through TLP tests and fusing performance evaluations, our findings reveal that the fabricated E-fuse device, featuring a Ni metal of 100 µm length, 5 µm width, and 5 nm thickness, exhibits a remarkable protection voltage of 251 V while achieving low-voltage fusing at only 7 V. Furthermore, an analysis of devices with varying dimensions is applied to develop a fusing lifetime model, enhancing the understanding of the device's fusing performance. This work primarily validates the feasibility of using cost-effective and simple-design Ni metal E-fuse devices for ESD protection applications, and presents their theoretical basis, thereby offering new insights and potential avenues for advancements in chip protection technology. We will continually improve the protection voltage and microsecond-scale fusing time in our upcoming study to make them more readily available for various applications.

Author Contributions: Conceptualization, H.G.; Data curation, H.G. and Y.L.; Project administration, H.G.; Writing—review and editing, H.G.; Resources, H.G.; Funding acquisition, H.G.; Formal analysis, J.L.; Investigation, J.L.; Methodology, J.L. and Y.L.; Writing—original draft, J.L. and Y.C.; Supervision, Y.T.; Validation, Y.L. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported in part by National Natural Science Foundation of China (Program No. 62471402), Key R&D plan of Shaanxi province, China (Program No. 2023GXLH-084), Natural Science Foundation of Chongqing, China (Program No. CSTB2023NSCQ-MSX0513), Natural Science Basic Research Program of Shaanxi for Youth Projects (Program No. D5110210132), and National Natural Science Foundation of China (Program No. 62104199).

Data Availability Statement: Data are contained within the article.

Conflicts of Interest: The authors declare no conflicts of interest.

## References

- 1. Meiguni, J.S.; Zhou, J.; Maghlakelidze, G.; Xu, Y.; Izadi, O.H.; Marathe, S.; Shen, L.; Bub, S.; Holland, S.; Beetner, D.G. Transient analysis of ESD protection circuits for high-speed ICs. *IEEE Trans. Electromagn. Compat.* **2021**, *63*, 1312–1321. [CrossRef]

- 2. Guan, Q. Energy Coupling of Contact ESD on Shielded Electronic Equipment. *Int. J. Perf. Eng.* 2021, *17*, 973.

- Angelov, G.V.; Dobrichkov, B.D.; Liou, J.J. An Overview of On-Chip ESD Protection in Modern Deep Sub-Micron CMOS Technology. In Proceedings of the 2018 IEEE XXVII International Scientific Conference Electronics-ET, Sozopol, Bulgaria, 13–15 September 2018; pp. 1–4.

- Scheier, S.; Frei, S. Characterization and modeling of ESD-behavior of multi layer ceramic capacitors. In Proceedings of the 2013 International Symposium on Electromagnetic Compatibility, Brugge, Belgium, 2–6 September 2013; pp. 1028–1033.

- Shen, Y.-S.; Ker, M.-D. The impact of holding voltage of transient voltage suppressor (TVS) on signal integrity of microelectronics system with CMOS ICs under system-level ESD and EFT/burst tests. *IEEE Trans. Electron Devices* 2021, 68, 2152–2159. [CrossRef]

- Koga, E.; Sawada, N. Electrical degradation caused by electro-static discharge pulse in ZnO-based multilayer varistor. *Key Eng. Mater.* 2009, 388, 15–18. [CrossRef]

- Yen, C.-T.; Hsu, F.-J.; Chu, K.-T.; Hung, C.-C.; Lee, L.-S.; Lee, C.-Y. SiC MOSFET with Integrated Zener Diode as an Asymmetric Bidirectional Voltage Clamp between the Gate and Source for Overvoltage Protection. In Proceedings of the 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019; pp. 135–138.

- 8. Yao, B.; Shi, Y.; Wang, H.; Xu, X.; Chen, Y.; He, Z.; Xiao, Q.; Wang, L.; Lu, G.; Li, H. A novel bidirectional AlGaN/GaN ESD protection diode. *Micromachines* **2022**, *13*, 135. [CrossRef]

- Shankar, B.; Gupta, S.D.; Soni, A.; Raghavan, S.; Shrivastava, M. ESD Behavior of AlGaN/GaN Schottky Diodes. *IEEE Trans. Device Mater. Reliab.* 2019, 19, 437–444. [CrossRef]

- Liu, S. Research on Optimal Design of Chip ESD Protection Circuit Based on CMOS Technology. *Trans. Comput. Sci. Intell. Syst. Res.* 2023, 1, 86–90. [CrossRef]

- 11. Liu, J.; Liu, Y.; Han, A.; Nie, Y.; Huang, Q.; Liu, Z. A novel voltage divider trigger SCR with low leakage current for low-voltage ESD application. *IEEE Trans. Electron Devices* **2022**, *69*, 2534–2542. [CrossRef]

- 12. Kuhn, W.B.; Eatinger, R.J.; Melton, S.A. ESD Detection Circuit and Associated Metal Fuse Investigations in CMOS Processes. *IEEE Trans. Device Mater. Reliab.* **2014**, *14*, 146–153. [CrossRef]

- Huang, S.-C.; Chen, L.-F.; Chen, C.-C.; Lin, T.-Y.; Hsu, K.-C.; Jou, Y.-N.; Lin, C.-H.; Chen, Y.-C.; Chen, W.-S.; Lee, J.-H. ESD protection for poly fuses. In Proceedings of the 2019 41st Annual EOS/ESD Symposium (EOS/ESD), Riverside, CA, USA, 15–20 September 2019; pp. 1–10.

- 14. Reiner, J.C.; Keller, T. Relevance of contact reliability in HBM-ESD test equipment. *Microelectron. Reliab.* **2001**, *41*, 1397–1401. [CrossRef]

- 15. Loto, C. Electroless nickel plating—A review. Silicon 2016, 8, 177–186. [CrossRef]

- 16. Reinhardt, K.A.; Kern, W. Handbook of Semiconductor Wafer Cleaning Technology, 3rd ed.; Noyes Publication: Cambridge, MA, USA, 2018; pp. 185–252.

- 17. Kern, W. The evolution of silicon wafer cleaning technology. J. Electrochem. Soc. 1990, 137, 1887. [CrossRef]

- 18. Harbeke, G.; Krausbauer, L.; Steigmeier, E.; Widmer, A.; Kappert, H.; Neugebauer, G. Growth and physical properties of LPCVD polycrystalline silicon films. *J. Electrochem. Soc.* **1984**, *131*, 675. [CrossRef]

- 19. Pan, X.; Broers, A.; Jeynes, C. Study of the lithographic process in deposited silicon dioxide. *J. Vac. Sci. Technol. B Microelectron. Nanometer Struct.-Process. Meas. Phenom.* **1992**, *10*, 2882–2885. [CrossRef]

- Shen, X.; Wang, H.; Yu, T. How do the electron beam writing and metal deposition affect the properties of graphene during device fabrication? *Nanoscale* 2013, *5*, 3352–3358. [CrossRef]

- 21. Leng, B.; Zhang, Y.; Tsai, D.P.; Xiao, S. Meta-device: Advanced manufacturing. Light Adv. Manuf. 2024, 5, 117–132. [CrossRef]

- 22. Chen, Y. Nanofabrication by electron beam lithography and its applications: A review. *Microelectron. Eng.* **2015**, *135*, 57–72. [CrossRef]

- 23. Li, X.; Hao, W.; Pan, Z.; Miao, Y.; Yue, Z.; Wang, A. Practical Considerations on ESD Testing. In Proceedings of the 2024 IEEE 42nd VLSI Test Symposium (VTS), Tempe, AZ, USA, 22–24 April 2024; pp. 1–3.

- Xie, J.; Shi, Q.; Gao, Y. Integrated circuit ESD protection structure failure analysis based on TLP technique. In Proceedings of the 2016 17th International Conference on Electronic Packaging Technology (ICEPT), Wuhan, China, 16–19 August 2016; pp. 1267–1271.

- Xin, Y.; Chen, W.; Sun, R.; Shi, Y.; Liu, C.; Xia, Y.; Wang, F.; Xu, X.; Shi, Q.; Wang, Y. Electrostatic discharge (ESD) behavior of p-GaN HEMTs. In Proceedings of the 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020; pp. 317–320.

- Chen, Z.; Zhang, M.; Yan, Y.; Xue, S.; Lan, W.; He, S.; Huang, Y.; Zhou, Y.; Kwok, H.-S. Study on Electrostatic Discharge Stress Reliability of Thin-Film Transistors with Various Interface and Structure Types. *IEEE Trans. Electron Devices* 2024, 1–5. [CrossRef]

- Chen, Q.; Ma, R.; Zhang, W.; Lu, F.; Wang, C.; Liang, O.; Zhang, F.; Li, C.; Tang, H.; Xie, Y.-H.; et al. Systematic Characterization of Graphene ESD Interconnects for On-Chip ESD Protection. *IEEE Trans. Electron Devices* 2016, 63, 3205–3212. [CrossRef]

- Xiao, Y.; Concannon, A.; Sankaralingam, R. HBM failures induced by ESD cell turn-off and circuit interaction with ESD protection. In Proceedings of the 2015 37th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Reno, NV, USA, 2 November 2015; pp. 1–7.

- 29. d'Heurle, F.M. Electromigration and failure in electronics: An introduction. Proc. IEEE 1971, 59, 1409–1418. [CrossRef]

- 30. Kothandaraman, C.; Iyer, S.K.; Iyer, S.S. Electrically programmable fuse (eFUSE) using electromigration in silicides. *IEEE Electron Device Lett.* **2002**, *23*, 523–525. [CrossRef]

- Sah, C.-T.; Jie, B. The Driftless Electromigration Theory (Diffusion-Generation-Recombination-Trapping Theory). J. Semicond. 2008, 29, 815–821.

- 32. Ho, P.S.; Kwok, T. Electromigration in metals. Rep. Prog. Phys. 1989, 52, 301. [CrossRef]

- 33. Tu, K.-N.; Gusak, A. Mean-time-to-failure equations for electromigration, thermomigration, and stress migration. *IEEE Trans. Compon. Packag. Manuf. Technol.* **2020**, *10*, 1427–1431. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.