Charge-Line Dual-FET High-Repetition-Rate Pulsed Laser Driver

Abstract

:1. Introduction

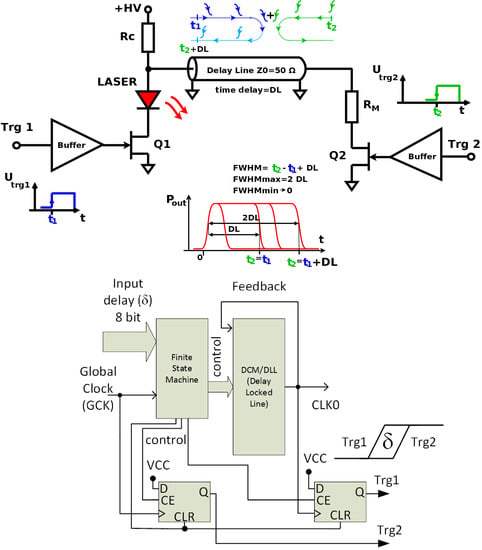

2. Foundation of Charge-Line Pulsed Laser Driver

2.1. Dual-FET Output Stage Topology

2.2. Circuit Timing

3. System Implementation

3.1. Tranistor Switches

3.2. Delay Line and Charging Resistor

RC < 500 Ω

3.3. Matching Resistor of the Line

3.4. Input Buffers

3.5. +HV DC–DC Converter

3.6. PCB Layout

4. Test Results

4.1. Preliminary Tests of the System

4.2. Pulsed Laser Driver Integrated with Infra-Red Laser

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Hintikka, M.; Hallman, L.; Kostamovaara, J. Comparison of the leading-edge timing walk in pulsed TOF laser range finding with avalanche bipolar junction transistor (BJT) and metal-oxide-semiconductor (MOS) switch based laser diode drivers. Rev. Sci. Instrum. 2017, 88, 123109. [Google Scholar] [CrossRef] [PubMed]

- Glaser, J. High Power Nanosecond Pulse Laser Driver Using an GaN FET. In Proceedings of the PCIM Europe 2018, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 5–7 June 2018; pp. 1–8. [Google Scholar]

- Masters, B.M. Fluorescence Lifetime Spectroscopy and Imaging: Principles and Applications in Biomedical Diagnostics. J. Biomed. Opt. 2014, 19, 119–121. [Google Scholar] [CrossRef]

- Walker, R.J. Quantum Cascade Laser Spectroscopy: Developments and Applications. Ph.D. Thesis, University of Oxford, Oxford, UK, 2011; pp. 17–51. [Google Scholar]

- Chen, S.; Sato, A.; Ito, T.; Yoshita, M.; Akiyama, H.; Yokoyama, H. Sub-5-ps optical pulse generation from a 1.55-µm distributed-feedback laser diode with nanosecond electric pulse excitation and spectral filtering. Opt. Express 2012, 20, 24843–24849. [Google Scholar] [CrossRef] [PubMed]

- Lanz, B. Compact Current Pulse-Pumped GaAs–AlGaAs Laser Diode Structures for Generating High Peak-Power (1–50 Watt) Picosecond-Range Single Optical Pulses. Ph.D. Thesis, University of Oulu, Oulu, Finland, 2016; pp. 47–83. [Google Scholar]

- Upadhyay, J.; Navathe, C.P. A fast high-voltage pulse generator wit variable amplitude and duration. Meas. Sci. Technol. 2006, 1, N25. [Google Scholar] [CrossRef]

- Żbik, M.; Wieczorek, P.Z. Versatile subnanosecond laser diode driver. Proc. SPIE 2016. [Google Scholar] [CrossRef]

- Miller, S.L.; Ebers, J.J. Alloyed junction avalanche transistors. Bell Syst. Techn. J. 1955, 34, 883–902. [Google Scholar] [CrossRef]

- Mohamad, S.; Tang, F.; Bermak, A.; Amira, A.; Benammar, M. A Low Power Temperature Sensor based on a Voltage to Time Converter Cell. In Proceedings of the 25th International Conference on Microelectronics (ICM), Beirut, Lebanon, 15–18 December 2013. [Google Scholar] [CrossRef]

- Osheroff, P.; Rue, G.S.L.; Gupta, S. A highly linear 4GS/s uncalibrated voltage-to-time converter with wide input range. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016; pp. 89–92. [Google Scholar]

- Kołodziejski, W.; Kuta, S.; Jasiełski, J. Current controlled delay line elements’ improvement study. In Proceedings of the International Conference on Signals and Electronic Systems (ICSES), Wroclaw, Poland, 18–21 September 2012. [Google Scholar]

- Xilinx. Available online: https://www.xilinx.com/support/documentation/data_sheets/ds160.pdf (accessed on 27 February 2019).

- Highland Technology. Available online: tps://www.highlandtechnology.com/DSS/T160DS.shtml (accessed on 28 February 2019).

- OSRAM Opto Semiconductors. Available online: https://www.osram.com/os/ecat/Radial%20T1%203-4%20SPL%20PL90/com/en/class_pim_web_catalog_103489/global/prd_pim_device_2220018/ (accessed on 27 February 2019).

- THORLABS. Available online: https://www.thorlabs.com/thorproduct.cfm?partnumber=DET08CFC (accessed on 27 February 2019).

| Parameter | Rating |

|---|---|

| UDS MAX | 84 V |

| ID SAT (UDS = 6 V, UGS = 2 V) | 2 A |

| RDS ON | <2 Ω |

| Operation frequency | DC to 6 GHz |

| Pdiss max | 8 W |

| Parameter | Symbol | Value |

|---|---|---|

| Threshold current | Ith | 0.75 A |

| Operating forward voltage | UF | 9 V |

| Wavelength | λpeak | 905 nm |

| Maximum output power | Po max | 75 W |

| Rise/fall time | tr/tf | 1 ns/1 ns |

| Optical Pulse Measurements | ||

|---|---|---|

| Amplitude [mW] | σA [mW] | SA = Amp./σA |

| 250 (U+HV = 45 V) | 6.5 | 38 |

| 520 (U+HV = 60 V) | 17.3 | 30 |

| 750 (U+HV = 80 V) | 28.6 | 26 |

| Electrical Pulse Measurements (RL = 33 Ω) | ||

| Amplitude [mA] | σC [mA] | Sc = Amp./σC |

| 510 (U+HV = 45 V) | 1.3 | 392 |

| 705 (U+HV = 60 V) | 1.8 | 391 |

| 960 (U+HV = 80 V) | 2.5 | 384 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Żbik, M.; Wieczorek, P.Z. Charge-Line Dual-FET High-Repetition-Rate Pulsed Laser Driver. Appl. Sci. 2019, 9, 1289. https://doi.org/10.3390/app9071289

Żbik M, Wieczorek PZ. Charge-Line Dual-FET High-Repetition-Rate Pulsed Laser Driver. Applied Sciences. 2019; 9(7):1289. https://doi.org/10.3390/app9071289

Chicago/Turabian StyleŻbik, Mateusz, and Piotr Zbigniew Wieczorek. 2019. "Charge-Line Dual-FET High-Repetition-Rate Pulsed Laser Driver" Applied Sciences 9, no. 7: 1289. https://doi.org/10.3390/app9071289

APA StyleŻbik, M., & Wieczorek, P. Z. (2019). Charge-Line Dual-FET High-Repetition-Rate Pulsed Laser Driver. Applied Sciences, 9(7), 1289. https://doi.org/10.3390/app9071289