# Article Interface Optimization and Transport Modulation of Sm<sub>2</sub>O<sub>3</sub>/InP Metal Oxide Semiconductor Capacitors with Atomic Layer Deposition-Derived Laminated Interlayer

Jinyu Lu<sup>1</sup>, Gang He<sup>1,\*</sup>, Jin Yan<sup>1</sup>, Zhenxiang Dai<sup>2</sup>, Ganhong Zheng<sup>1,\*</sup>, Shanshan Jiang<sup>3</sup>, Lesheng Qiao<sup>1</sup>, Qian Gao<sup>1</sup> and Zebo Fang<sup>4,\*</sup>

- <sup>1</sup> School of Materials Science and Engineering, Anhui University, Hefei 230601, China; lu19971210@outlook.com (J.L.); B01914070@ahu.edu.cn (J.Y.); B19201052@ahu.edu.cn (L.Q.); gaoq@ahu.edu.cn (Q.G.)

- <sup>2</sup> School of Physics and Optoelectronics Engineering, Anhui University, Hefei 230601, China; physdai@ahu.edu.cn

- <sup>3</sup> School of Integration Circuits, Anhui University, Hefei 230601, China; jiangshanshan@ahu.edu.cn

- <sup>4</sup> School of Mathematical Information, Shaoxing University, Shaoxing 312000, China

- \* Correspondence: ganghe01@issp.ac.cn (G.H.); ghzheng@ahu.edu.cn (G.Z.); csfzb@usx.edu.cn (Z.F.)

Citation: Lu, J.; He, G.; Yan, J.; Dai, Z.; Zheng, G.; Jiang, S.; Qiao, L.; Gao, Q.; Fang, Z. Interface Optimization and Transport Modulation of Sm<sub>2</sub>O<sub>3</sub>/InP Metal Oxide Semiconductor Capacitors with Atomic Layer Deposition-Derived Laminated Interlayer. *Nanomaterials* **2021**, *11*, 3443. https://doi.org/ 10.3390/nano11123443

Academic Editor: Sergio Brutti

Received: 14 November 2021 Accepted: 16 December 2021 Published: 19 December 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). **Abstract:** In this paper, the effect of atomic layer deposition-derived laminated interlayer on the interface chemistry and transport characteristics of sputtering-deposited Sm<sub>2</sub>O<sub>3</sub>/InP gate stacks have been investigated systematically. Based on X-ray photoelectron spectroscopy (XPS) measurements, it can be noted that ALD-derived Al<sub>2</sub>O<sub>3</sub> interface passivation layer significantly prevents the appearance of substrate diffusion oxides and substantially optimizes gate dielectric performance. The leakage current experimental results confirm that the Sm<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/InP stacked gate dielectric structure exhibits a lower leakage current density than the other samples, reaching a value of  $2.87 \times 10^{-6}$  A/cm<sup>2</sup>. In addition, conductivity analysis shows that high-quality metal oxide semiconductor capacitors based on Sm<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/InP gate stacks have the lowest interfacial density of states ( $D_{it}$ ) value of  $1.05 \times 10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup>. The conduction mechanisms of the InP-based MOS capacitors with different stacked gate dielectric structures, we placed samples for leakage current measurements at low varying temperatures (77–227 K). Based on the measurement results, Sm<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/InP stacked gate dielectric is a promising candidate for InP-based metal oxide semiconductor field-effect-transistor devices (MOSFET) in the future.

**Keywords:** MOS capacitors; Sm<sub>2</sub>O<sub>3</sub> high-k gate dielectric; atomic layer deposition; conduction mechanisms; interface state density

# 1. Introduction

As the integration of IC continues to increase, CMOS feature sizes will also continue to decrease in order to reduce the cost of individual transistors, increase the switching speed of transistors, and reduce the power consumption of the circuit. As the feature size of CMOS devices continues to decrease, it will also cause the SiO<sub>2</sub> gate dielectric and Si substrate used in conventional processes to decrease in size as well. When the size is smaller than a certain limit, the gate leakage current will grow exponentially, while the device will not operate properly due to the laws of quantum physics [1,2]. The use of high-k materials for the replacement of SiO<sub>2</sub> gate dielectrics is an option that has been shown to be feasible [3]. Among these high k materials, samarium oxide (Sm<sub>2</sub>O<sub>3</sub>) is considered as the next potential gate dielectric due to its high dielectric constant (~15) [4], sufficiently large band gap (5.1 eV) [5], low hygroscopicity, and high chemical and thermal stability [6]. Coulomb scattering and phonon scattering at the interface between the high-k gate dielectric and the channel material lead to a significant reduction in channel mobility, which severely affects

the further increase in the speed of CMOS logic devices. Selecting channel materials with high mobility is an effective way to solve this problem [7]. Compared with conventional Si-based material CMOS devices, III-V group semiconductors have advantages due to their large switching speed and small dynamic power consumption [8]. Among the group III-V semiconductors, InP has received more attention due to its higher carrier mobility and smaller band gap [9].

However, InP is prone to the formation of interfacial defects, which can limit the operating performance of the device [10]. Also, a surface with many chemical impurities can have a considerable impact on the performance of InP MOS capacitors [11]. High  $D_{it}$  leads to the frequency dispersion of the Fermi energy level pegging and capacitance, which also prevents the formation of inverse or accumulation layers in CMOS devices [12].

Different InP surface passivation methods have been investigated for a long time, including low-temperature processes [13], ozone treatment [14], chemical etching [15], and sulfide solution passivation [16,17]. A great deal of work has also been devoted to atomic layer deposition (ALD) passivation layers to modulate the InP interface [18]. It has been demonstrated that ALD-derived Al<sub>2</sub>O<sub>3</sub> films can effectively suppress the interfacial diffusion from the substrate to the high-k films. More importantly, the operating temperature can be kept low (~200  $^{\circ}$ C) when the Al<sub>2</sub>O<sub>3</sub> film is on the passivated substrate surface. There are previous reports confirming that the insertion of Al<sub>2</sub>O<sub>3</sub> between the high-k gate dielectric and GaAs can improve the thermal stability. However, even in the presence of an Al<sub>2</sub>O<sub>3</sub> passivation layer to improve the interface, the diffusion of In and P elements into the gate dielectric still has an impact on the electrical characteristics of the device when fabricating InP MOS capacitors. R. V. Galatage et al. reported that the In-O and P-O states at the interface lead to a degradation of the electrical characteristics [19]. Their results also demonstrated the effectiveness of ALD-derived Al<sub>2</sub>O<sub>3</sub> passivation layers between the gate dielectric and the InP substrate. Chee-Hong An et al. systematically analyzed that Al<sub>2</sub>O<sub>3</sub> can inhibit dissociation and reactant diffusion in InP substrates [20]. However, the effect of the position of the Al<sub>2</sub>O<sub>3</sub> passivation layer on the electrical properties and interfacial bonding state of InP MOS devices has not been reported systematically.

In this work, we deposited  $Sm_2O_3$  films by magnetron sputtering and obtained  $Al_2O_3$  passivation layers by ALD equipment to fabricate three different gate stacks on InP substrates, corresponding to  $Al_2O_3/Sm_2O_3/InP$ ,  $Al2_2O_3/Sm_2O_3/Al_2O_3/InP$ , and  $Sm_2O_3/Al_2O_3/InP$ , respectively. X-ray photoelectron spectroscopy (XPS) and electrical measurements were used to investigate the effect of  $Al_2O_3$  passivation position on the chemical composition and electrical parameters of the interface. In addition, the leakage current conduction mechanisms (CCMs) of InP-based MOS capacitors with three different laminated gate electrical stacks measured at room temperature and low temperature (77–227 K) were systematically investigated.

## 2. Materials and Methods

In this work, we chose sulfur-doped n-type InP wafers as the substrate for fabricating MOS capacitors. Before depositing the  $Sm_2O_3$  gate dielectric, the wafers were subjected to a standard degreasing process by sequential immersion in ethanol and acetone for 5 min each. After that, the wafers were immersed in 20% ammonium sulfide solution for 15 min to remove the native oxides. Then, the wafers are rinsed with deionized water and then blown dry with high purity nitrogen gas. The cleaned wafers are transferred to an ALD system (MNT-PD100Oz-L6S1G2, MNT Micro and Nanotech). On the ALD process, plasma  $O_2$  and trimethylaluminum (TMA) were selected as the oxidant and aluminum metal precursor, and a 2 nm Al<sub>2</sub>O<sub>3</sub> passivation layer was deposited on the InP substrate. The Al<sub>2</sub>O<sub>3</sub> passivation layers were deposited by using 30 pulse cycles of plasma  $O_2$  precursors  $[O_2(2s)/Ar purge (25s)]$  and 15 pulse cycles of trimethylaluminum (TMA) and plasma  $O_2$  [TMA (0.03s)/O<sub>2</sub> 2s/Ar purge (25s)], respectively. During this process, the chamber pressure and the deposition temperature were maintained at 35 Pa and 200 °C. After ALD Al<sub>2</sub>O<sub>3</sub> gase

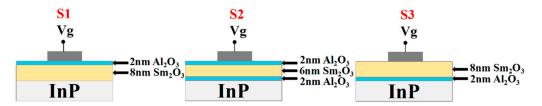

dielectrics by sputtering samarium target with purity of 99.9%. When the chamber pressure was 0.8 Pa,  $Sm_2O_3$  thin film was deposited under an Ar/O<sub>2</sub> (50/10 sccm) atmosphere. To explore the electrical characteristics of Sm<sub>2</sub>O<sub>3</sub>/InP MOS capacitors with different stacking positions of Al<sub>2</sub>O<sub>3</sub> passivation layers, a 200-µm-diameter Al electrode was deposited by thermal evaporation, while an aluminum electrode was grown on the back side to form an ohmic contact. Figure 1 demonstrates the schematics of InP-MOS capacitors based on different stacked gate dielectric structures. Sample S1 corresponds to Al<sub>2</sub>O<sub>3</sub> (2 nm)/Sm<sub>2</sub>O<sub>3</sub> (8 nm)/InP, sample S2 corresponds to  $Al_2O_3$  (2 nm)/ $Sm_2O_3$  (6 nm)/ $Al_2O_3$  (2 nm)/InP, and sample S3 corresponds to Sm<sub>2</sub>O<sub>3</sub> (8 nm)/Al<sub>2</sub>O<sub>3</sub> (2 nm)/InP, respectively. By using the ESCALAB 250Xi system, XPS (X-ray photoelectron spectroscopy) measurements were performed at Al Ka (1486.7 eV) to investigate the interfacial chemical properties of the  $Sm_2O_3/InP$  gate stack and the chemical function of the  $Al_2O_3$  passivation layer. Furthermore, the escape angle used in obtaining the XPS profiles is 50° and the corresponding probing depth is about 1–10 nm. Ultraviolet-visible spectroscopy (Shimadzu, UV-2550) was performed to obtain the samples' optical band gap. The physical thickness of the above samples was extracted by using spectroscopic ellipsometry measurements (SANCO Inc., Shanghai, China, SC630) with the help of the Cauchy-Urbach model. The Cascade Probe Station was connected to the semiconductor analysis equipment (Agilent B1500A) for capacitance-voltage (C-V), transconductance-voltage (G-V), and leakage current-voltage (I-V) measurements at room temperature. For low temperature (77–227 K) leakage current testing, the Lake Shore Cryotronics Vacuum Probing Station was used.

Figure 1. Schematics of InP-based MOS capacitors based on different stacked gate dielectrics.

## 3. Results and Discussion

#### 3.1. XPS Analyses

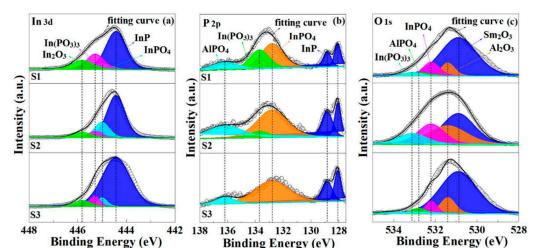

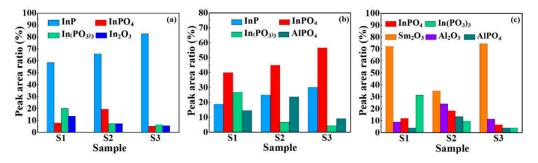

To evaluate the chemical bonding states of various stacked gate dielectrics, XPS measurements were carried out. Figure 2 displays the In 3d, P 2p, and O 1s XPS spectra of three samples with various stacked gate dielectrics. It can be noted that In 3d spectra can be deconvoluted into four components that represent the InP, InPO<sub>4</sub>, In(PO<sub>3</sub>)<sub>3</sub>, and  $In_2O_3$ , respectively. The relative intensity values of the different components have been extracted and are shown in Figure 3a. For S2 and S3, the contents of  $In(PO_3)_3$  and  $In_2O_3$ shows a decreasing trend, indicating that the ALD-derived Al<sub>2</sub>O<sub>3</sub> passivation layers prior to Sm<sub>2</sub>O<sub>3</sub> deposition can significantly prohibit the formation of In and P suboxides, which can be attributed to the interface cleaning function of plasma  $O_2$  [21]. Compared to S2, the peak areas of InPO<sub>4</sub> corresponding to S1 and S3 remain approximate at about 7.89% and 5.20%, which is much lower than that of S2 (19.41%), indicating that double deposition of ALD-derived  $Al_2O_3$  may accelerate the diffusion of oxygen in the substrate and the formation of indium phosphate. During the secondary deposition of Al<sub>2</sub>O<sub>3</sub>, more oxygen vacancies may generate, which can be ascribed to plasma  $O_2$  acting as an oxygen source, and promote the oxygen interdiffusion between Al<sub>2</sub>O<sub>3</sub> passivation layers and the InP substrate.  $In(PO_3)_3$  can react with In to produce InP and InPO<sub>4</sub> using the following reaction Equation [22].

$$8In + 4In(PO_3)_3 \rightarrow 3InP + 9InPO_4 \tag{1}$$

Figure 2. (a) In 3d, (b) P 2p, and (c) O 1s XPS spectra for S1, S2, and S3 sample.

Figure 3. Peak area ratio histograms of (a) In 3d, (b) P 2p, and (c) O 1s spectra.

More importantly, sample S3 shows a tendency to decrease the content of  $In(PO_3)_3$  and  $AIPO_4$  compared to sample S2, which can give a detailed illustration from the phenomenon of P 2p spectral changes. As shown in Figure 2b, it can be noted that P 2p spectra can be deconvoluted into four components, which represent InP, InPO<sub>4</sub>,  $In(PO_3)_3$ , and  $AIPO_4$ , respectively. No P<sub>2</sub>O<sub>5</sub> was detected in all samples, which can be attributed to the fact that gaseous P<sub>2</sub>O<sub>5</sub> generated during the deposition can easily diffuse through the defects in the gate dielectric [22]. The peak area ratio of  $In(PO_3)_3$  for S2 and S3 showed a significant decreasing trend compared to S1, indicating that  $Al_2O_3$  prior to the deposition of  $Sm_2O_3$  gate dielectric can inhibit the formation of P-O bound states and improve the interfacial quality. The detection of  $AIPO_4$  in P 2p spectra can be attributed to the reaction equation described below [23].

$$4Al + 7O_2 + 2In(PO_3)_3 + 2InP \rightarrow 4AlPO_4 + 4InPO_4$$

<sup>(2)</sup>

Based on the mentioned reaction above, it can be inferred that two depositions of  $Al_2O_3$  passivation layers increase the formation of  $AIPO_4$ , which is confirmed by the change in peak area ratio shown in Figure 3c. In order to systematically explore the interfacial chemistry of various stacked gate dielectrics, O 1s spectra were investigated and are shown in Figure 2c. O 1s spectra can be deconvoluted into  $Sm_2O_3$ ,  $Al_2O_3$ ,  $InPO_4$ ,  $In(PO_3)_3$ , and  $AIPO_4$ . According to the reaction Equation (2), in the plasma  $O_2$  atmosphere,  $In(PO_3)_3$  can react with  $O_2$  to produce  $AIPO_4$  and  $InPO_4$  and leads to the disappearance of  $In(PO_3)_3$ . In agreement with the previous In 3d and P 2p spectra, S1 has the largest  $In(PO_3)_3$  content, leading to a decrease in interfacial quality and deterioration of  $Al_2O_3$ . For S3 sample, the contents of  $InPO_4$ ,  $AIPO_4$ , and  $In_2O_3$  were significantly controlled, indicating that the addition of an ALD-derived  $Al_2O_3$  layer prior to the deposition of  $Sm_2O_3$  gate dielectric could reduce the generation of suboxides and improve the interfacial quality.

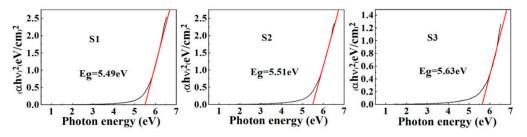

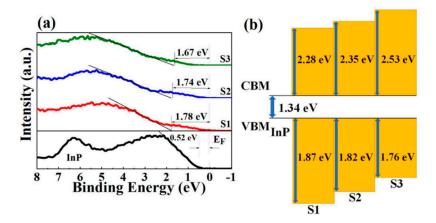

#### 3.2. Band Alignment Characteristics

To assess the optical characteristics of the three various stacked gate dielectrics, UV-Vis spectroscopy was used to obtain the absorption spectra and the optical bandgap values (Figure 4) of samples S1, S2, and S3 were determined to be 5.49, 5.51, and 5.63 eV, respectively, based on the Tauc relationship [24]. Compared with pure Sm<sub>2</sub>O<sub>3</sub> and pure Al<sub>2</sub>O<sub>3</sub>, the band gaps of three various stacked gate dielectrics showed a value balance [25]. Also, this section investigates the valence band maximum (VBM) of various stacked gate dielectrics, as the valence band alignment is crucial for assessing the interface quality. As shown in Figure 5a, the band gap values of InP substrates were derived from XPS measurements, while the valence bands of samples S1, S2, and S3 were deduced from the absorption spectra by linear extrapolation. Based on Kraut's method [26], we also calculated the valence band shift ( $\Delta E_V$ ) to evaluate the valence band electronic structure of the samples. By using Sm  $3d_{5/2}$  and In 3d core-level spectra, the  $\Delta E_V$  of high-k/InP gate stacks was determined based on the following formula:

$$\Delta E_{\rm V} = (E_{\rm In \ 3d} - E_{\rm V})_{\rm InP} - (E_{\rm Sm \ 3d} - E_{\rm V})_{\rm high-k} - (E_{\rm In \ 3d} - E_{\rm Sm \ 3d})_{\rm high-k/InP}$$

(3)

where  $E_{In 3d}$  (InP) and  $E_{Sm 3d}$  (high-k) corresponding to the core-level positions are extracted to be 445.8 and 1084.3 eV. In addition, the  $E_v$  (InP) and  $E_v$  (high-k) represent the VBM (Valence-Band Maximum) of the bulk materials. The values of  $\Delta E_v$  are calculated as 1.87, 1.82, and 1.76 eV, respectively, based on the binding energy difference in the high-k/InP structure. Meanwhile, the value of the conduction band offset ( $\Delta E_c$ ) is obtained by subtracting the extracted  $\Delta E_v$  and the band gap of the InP (1.34 eV) from the band gap of dielectric layers [27].

$$\Delta E_{\rm C} ({\rm high} - {\rm k/InP}) = E_{\rm g} ({\rm high} - {\rm k}) - \Delta E_{\rm V} ({\rm High} - {\rm k/InP}) - E_{\rm g} ({\rm InP})$$

(4)

As shown in Figure 5b, the  $\Delta E_c$  values for the three samples were calculated as 2.28, 2.35, and 2.53 eV. According to previous reports in the literature,  $\Delta E_c$  is related with the tunneling leakage current. The higher  $\Delta E_c$  indicates that the leakage current of the Sm<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/InP samples is smaller.

Figure 4. The determination of band gaps for sample S1, S2, and S3.

#### 3.3. Electrical Properties of InP-MOS Capacitors

## 3.3.1. Capacitance-Voltage Measurements

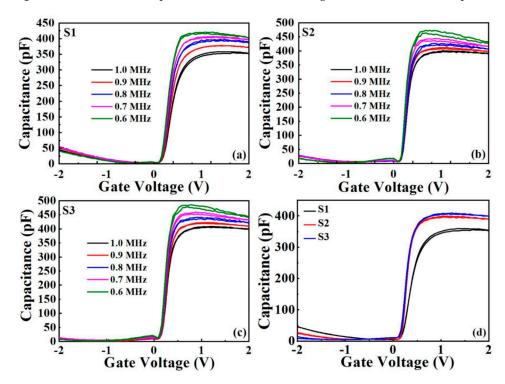

The frequency dependent capacitance-voltage curves of sample S1, S2, and S3 with double sweep mode are shown in Figure 6a–c. When the frequency increases, all samples show a decreased accumulation capacitance.

Figure 5. (a) Valence band spectra; (b) Schematic band diagram of S1, S2, and S3 sample.

**Figure 6.** (**a**–**c**) Capacitance–voltage (C–V) curves for S1–S3 measured at different frequency (0.6–1 MHz). (**d**) Capacitance–voltage (C–V) curves for all samples measured at 1 MHz.

Meantime, at high frequency conditions, the series resistance will deviate from the predetermined theoretical value due to the disappearance of the interface trap charge. On the contrary, at low frequencies, when the oxide capacitance ( $C_{ox}$ ) connects with the space charge capacitance ( $C_{sc}$ ), the value of the accumulation region increases with the series resistance due to the interface state showing frequency-dependent properties [28–30].

The decrease in the accumulation capacitance can be attributed to the fact that the interfacial traps do not have enough time to respond to the voltage frequency [30]. The maximum accumulation capacitance and minimum hysteresis voltage were observed in the S3 sample, indicating that the Al<sub>2</sub>O<sub>3</sub> passivation layer suppressed the appearance of In and P oxides and the formation of low-K interfacial layers. To evaluate the interface quality, important electrical parameters such as equivalent oxide thickness (EOT), dielectric constant (k), flat band voltage (V<sub>fb</sub>), hysteresis voltage ( $\Delta V_{fb}$ ), oxidation charge density ( $Q_{ox}$ ), and boundary trapped oxide charge density ( $N_{bt}$ ) were extracted from the test curves, and these data are presented in Table 1. The variation of V<sub>fb</sub> depends on the values of oxide capacitance and bulk oxide charge [31]. The k values corresponding to samples S1, S2,

and S3 are calculated to be 12.96, 14.39, and 14.75, which are consistent with the previous investigation [4].

| Table 1. MOS capacitors elect | trical parameters obtained | from C–V and <i>J</i> – <i>V</i> Curves. |

|-------------------------------|----------------------------|------------------------------------------|

|-------------------------------|----------------------------|------------------------------------------|

| Sample | EOT (nm) | k     | V <sub>fb</sub><br>(V) | ∆V <sub>fb</sub><br>(mV) | Q <sub>ox</sub><br>(cm <sup>-2</sup> ) | N <sub>bt</sub><br>(cm <sup>-2</sup> ) | J<br>(A/cm <sup>-2</sup> ) |

|--------|----------|-------|------------------------|--------------------------|----------------------------------------|----------------------------------------|----------------------------|

| S1     | 3.01     | 12.96 | 0.25                   | 3.44                     | $-1.62 	imes 10^{12}$                  | $-2.46	imes10^{10}$                    | $1.07 \times 10^{-5}$      |

| S2     | 2.71     | 14.39 | 0.21                   | 5.16                     | $-1.43	imes10^{12}$                    | $-4.11	imes10^{10}$                    | $8.42 	imes 10^{-6}$       |

| S3     | 2.65     | 14.75 | 0.19                   | 1.55                     | $-1.30	imes10^{12}$                    | $-1.26	imes10^{10}$                    | $2.87	imes10^{-6}$         |

A small  $V_{fb}$  of 0.19 V was observed for sample S3. This phenomenon can be explained by the following statement: electrons are easily captured by oxygen vacancies to form negatively charged interstitial oxygen atoms [32] and as fewer oxygen vacancies exist at the interface, the smaller the positive flat voltage required to maintain the band unbent [33]. Also, the hysteresis voltage depends on the boundary trap caused by the intermixing of the high K layer and the interfacial layer [34]. The value of the hysteresis voltage reaches a minimum (1.55 mV) for S3, indicating that the boundary trapping charge becomes weaker after the insertion of Al<sub>2</sub>O<sub>3</sub> between the gate dielectric and the substrate. The  $Q_{ox}$ and  $N_{bt}$  values were calculated from the obtained  $V_{fb}$  and  $\Delta V_{fb}$  values by the following equations [35].

$$Q_{ox} = -\frac{C_{\max}\left(v_{fb} - \varphi_{ms}\right)}{qA} \tag{5}$$

$$N_{bt} = -\frac{C_{\max} \bigtriangleup V_{fb}}{qA} \tag{6}$$

where  $\varphi_{ms}$  is the contact potential difference between Al electrode and InP substrate, *q* is the electronic charge, and *A* is the Al electrode areas. According to Table 1, it can be noticed that S3 has the lowest  $Q_{ox}$  and  $N_{bt}$ , which implies the reduction of interfacial trap defects and the optimization of interfacial properties.

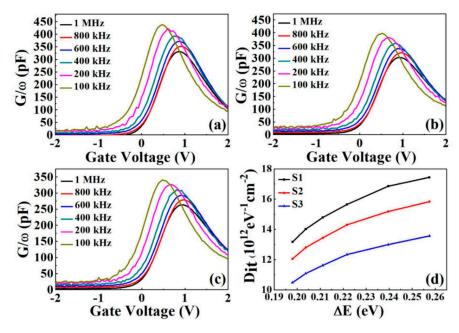

# 3.3.2. Conductivity-Voltage Measurements

Moreover, to quantify the interface defect distribution for all samples, the interface state density ( $D_{it}$ ) has been extracted by the conductivity-voltage measurements with frequencies varying from 100 kHz to 1 MHz.  $D_{it}$  is related to the parallel interfacial trap capacitance ( $C_{it}$ ) and parallel conductivity (G). At the same time,  $C_{it}$  can be related by the following equation.  $C_{it} = qD_{it}$ , while the conductivity measurements is to analyze level does not change  $D_{it}$ . The basic principle of conductivity measurements is to analyze the losses due to the diversity of charge states at the trap level. Near the Fermi level, the synchronous conductivity occupancy is mobilized by the interfacial traps to produce a regular variation. The maximum loss occurs when the interface trap is resonantly shifted with the applied AC signal ( $\omega \tau = 1$ ). The response time of the characteristic trap changes the frequency,  $\tau = 2\pi/\omega$ . The capture and emission rates from Shockley-Redhall theory modulate the response time [36]:

$$\tau = \frac{exp[\Delta E/k_B T]}{\sigma v_{th} D_{dos}} \tag{7}$$

where there is an energy difference  $\Delta E$  between the trap level  $E_T$  and the edge of the majority carrier band,  $v_{th}$  is the majority carrier being thermally activated to obtain the average velocity,  $D_{dos}$  is the effective density of states of the majority carrier band,  $k_B$  is the Boltzmann constant, and T is the temperature [37]. The curves between conductivity (G/ $\omega$ ) and gate voltage for all samples are shown in Figure 7a–c. The apparent shift of the conductivity peak proves the validity of the Fermi-level shift and confirms the existence of

the Fermi-level deconvolution effect [38]. Assuming that the underlying surface oscillations can be neglected, the value of  $D_{it}$  is inferred using the normalized parallel conductivity peak  $(G_P/\omega)_{max}$  [39].

$$D_{it} \approx \frac{2.5}{Aq} \left(\frac{G_p}{\omega}\right)_{max} \tag{8}$$

where *A* is the device area. It is necessary to confirm the transformation law between the band bending potential of the energy location  $E_T$  and the trap energy level distribution. Furthermore, the values of  $E_T$  can be determined by the frequency of  $(G_P/\omega)_{max}$ , where Equation (8) is used to calculate  $D_{it}$  and to correspond its value to  $\Delta E$  [40].

$$\Delta E = (E_{\rm C} - E_{\rm T}) = \frac{k_B T}{q} In \left(\frac{\sigma v D_{dos}}{2\pi f_{max}}\right)$$

(9)

Figure 7d shows the variation of  $D_{it}$  for the three samples. With the increase of  $\Delta E$ , the value of  $D_{it}$  shows an increasing trend. However, S3 possesses a lower density of interfacial states compared to S1 and S2, which indicates that the insertion of an Al<sub>2</sub>O<sub>3</sub> passivation layer between the Sm<sub>2</sub>O<sub>3</sub> gate dielectric and the InP substrate can suppress the formation of In and P suboxides and improve the quality of MOS capacitors.

We compared some of the data obtained from this work with some previously published work. As can be seen in Table 2, the  $Sm_2O_3$  dielectric has a smaller leakage current density than TiO<sub>2</sub> and HfO<sub>2</sub>, indicating that the  $Sm_2O_3$  stacked gate dielectric has a larger conduction band shift, resulting in an increased barrier height and thus a reduced leakage current density. The  $Sm_2O_3$  stacked gate dielectric has the smallest hysteresis value, indicating that the trapped charge in the gate dielectric is not very sensitive to the frequency response of the voltage, and will trap fewer electrons to keep the energy band from being bent, while the device maintains a consistent response to different test voltages in the antipattern region. In the interface state density, it is smaller than HfO<sub>2</sub> as the gate dielectric directly deposited in InP, but it seems to be higher than TiO<sub>2</sub> gate dielectric, considering the different testing methods, the interface state density of the current work is obtained directly by conductivity method with accuracy, the previous work is by C–V curve, there may be some differences.

**Figure 7.** Multi-frequency G–V characteristics of InP-based MOS capacitors of (**a**) S1, (**b**) S2, and (**c**) S3. (**d**) Energy distributions of Dit for S1, S2, and S3.

|                                                               | Sm <sub>2</sub> O <sub>3</sub> /Al <sub>2</sub> O <sub>3</sub> /InP<br>(This Work) | PMA-TiO <sub>2</sub> /S-InP [41]                       | TiO <sub>2</sub> /S-InP [41]                            | 10 Å Si IPL/51 Å<br>HfO <sub>2</sub> /InP [42] | 70 Å HfO <sub>2</sub> /InP<br>[42] | HfO <sub>2</sub> (10 nm)/Al <sub>2</sub> O <sub>3</sub><br>(0.2 nm)/InGaAs/InP [43] |

|---------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------|

| Leakage current density (A/cm <sup>2</sup> )                  | $2.87\times10^{-6}$ at 1 V                                                         | $1.9\times10^{-7}$ at 2 V $2.7\times10^{-5}$ at $-2$ V | $5.01\times10^{-6}$ at 2 V $1.5\times10^{-2}$ at $-2$ V | $1.32\times10^{-3}$ at 1 V                     | $3.94\times10^{-2}$ at 1 V         | $2.4	imes10^{-2}$                                                                   |

| k                                                             | 14.75                                                                              | 39                                                     | 34                                                      | /                                              | /                                  | /                                                                                   |

| $\Delta V fb (mV)$                                            | 1.55                                                                               | 40                                                     | 250                                                     | 240                                            | 280                                | /                                                                                   |

| $\mathrm{D}_{\mathrm{it}}~(\mathrm{cm}^{-2}\mathrm{eV}^{-1})$ | (G-V)<br>$1.05 \times 10^{13}$                                                     | (C-V) $3.1 \times 10^{11}$                             | $(	ext{C-V})$<br>$5	imes 10^{11}$                       | (C-V)<br>$3-8 \times 10^{12}$                  | (C-V)<br>$2-9 \times 10^{13}$      | (C-V)<br>$2 \times 10^{12}$                                                         |

Table 2. Comparison of different InP MOS capacitor parameters.

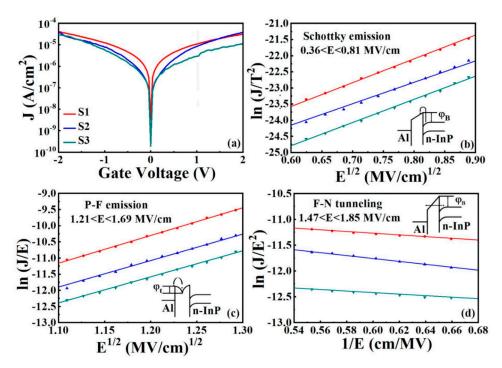

3.3.3. J-V Analyses and Conduction Mechanisms at Room Temperature

Figure 8a shows the leakage current characteristics of all samples measured at room temperature. The leakage current density (*J*) values for S1, S2, and S3 at 1 V are  $1.07 \times 10^{-5}$ ,  $8.42 \times 10^{-6}$ , and  $2.87 \times 10^{-6}$  A/cm<sup>2</sup>, respectively. It can be seen that S1 has a higher leakage current density, which can be attributed to larger interface traps and the border traps that deteriorate the interface quality and degrade the device performance [44]. For the S3 sample, the minimum leakage current density has been observed, which is due to the higher  $\Delta E_c$  and the suppressed tunneling in the Sm<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/InP gate stack [45].

To investigate the leakage current characteristics of various stacked gate dielectrics, we systematically studied three different current conduction mechanisms (CCMs) under substrate injection, as shown in Figure 8b–d. The extracted important electrical parameters are listed in Table 3.

**Figure 8.** (**a**) J–V characteristics measured at room temperature. (**b**) SE emission, (**c**) PF emission, and (**d**) FN tunneling plots for all the samples under substrate injection.

Table 3. Extracted MOS capacitors electrical parameters measured at room temperature.

| Sample | J (A/cm <sup>2</sup> ) | ε <sub>r</sub> | n    | ε <sub>ox</sub> | φ <sub>t</sub> (eV) |

|--------|------------------------|----------------|------|-----------------|---------------------|

| S1     | $1.07 	imes 10^{-5}$   | 4.00           | 2.00 | 11.90           | 0.53                |

| S2     | $8.42 	imes 10^{-6}$   | 4.96           | 2.23 | 13.01           | 0.54                |

| S3     | $2.87	imes10^{-6}$     | 4.23           | 2.06 | 13.41           | 0.55                |

Schottky emission (*SE*) is a typical type of thermal ionization emission in which charges gain energy to overcome barriers to migration into the dielectric. The standard *SE* can be described as [46]:

$$J_{SE} = A^* T^2 exp\left[\frac{-q(\varphi_B - \sqrt{qE/4\pi\varepsilon_0\varepsilon_r})}{k_B T}\right]$$

(10)

$$A^* = \frac{4\pi q k_B^2 m_{ox} *}{h^3} = 120 \frac{m_{ox} *}{m_0} \tag{11}$$

where  $A^*$  is the effective Richardson constant, the free electron mass and the effective mass of electrons in the gate dielectric correspond to  $m_o$  and  $m_{ox^*}$ , E is the electric field,  $q\varphi_B$  is the Schottky barrier height, and  $\varepsilon_o$  and  $\varepsilon_r$  represent the vacuum dielectric constant and the optical dielectric constant, respectively [47]. It is observed in Figure 8b that at lower electric fields (0.36–0.81 MV/cm), there is a good linear relationship between  $\ln(J/T^2)$  and  $E^{1/2}$  for S1, S2, and S3. The slope of the SE diagram is denoted as  $\sqrt{q^3/4\pi\varepsilon_0\varepsilon_r}/k_BT$ . The fitted  $\varepsilon_r$  and the refractive index n ( $n = \varepsilon_r^{1/2}$ ) for S1, S2, and S3 are (4, 2), (4.96, 2.23), and (4.23, 2.06), respectively. All the fits are consistent with the previously reported values [48], revealing that CCM (current conduction mechanism) at room temperature is dominated by SE emission in the low electric field region.

The Poole–Frenkel (*PF*) emission can be ascribed to the thermally excited electrons obtaining sufficient energy to escape from traps into the conduction band of the dielectric at a higher electric field, which can be expressed by the following formula [49]:

$$J_{PF} = AE \exp\left[\frac{-q(\varphi_t - \sqrt{qE/\pi\varepsilon_0\varepsilon_{ox}})}{k_BT}\right]$$

(12)

where *A* represents a constant, the trap energy level of the conduction band corresponds to  $\varphi_t$ , and  $\varepsilon_{ox}$  represents the dielectric constant. According to the previous theory,  $\ln(J/E)$  should have a good proportionality with  $E^{1/2}$ , as shown in Figure 8c. The  $\varepsilon_{ox}$  extracted from the slope of the fitted line for all samples was calculated as 11.90, 13.01, and 13.41, which is in agreement with the reported reference [4]. It can be concluded that at higher electric fields (1.21–1.69 MV/cm), the PF emission dominates the CCM of all samples. Also, the value of the trap energy level ( $\varphi_t$ ) can be extracted based on the intercept point of the fitted curve described as  $lnB - \frac{q\varphi_t}{k_BT}$ . As shown in Figure 8c, the calculated values of  $\varphi_t$  are 0.53, 0.54, and 0.55 eV, corresponding to S1, S2, and S3. S3 has the largest  $\varphi_t$  value in the three samples, indicating that the electrons obtain more energy to cross the trap, leading to present the smallest leakage current density in the S3 sample.

The high-field dependent conduction mechanism is represented by Fowler-Nordheim tunneling, which is manifested by the fact that the insulating layer can be penetrated by electrons, which enter the conduction band of the gate dielectric in a high electric field. The leakage current density is linked to other parameters of Fowler-Nordheim (*FN*) tunneling and is described by the following Equation [46]:

$$J_{FN} = \frac{q^3 E^2}{16\pi^2 \hbar \varphi_{ox}} \exp\left[-\frac{4\sqrt{2m_T^* \varphi_B^{3/2}}}{3\hbar q E}\right]$$

(13)

where  $\varphi_{ox}$  is oxide barrier height;  $m_T^*$  is the tunneling effective electron mass in the gate oxide film, and the other notations remain unchanged from the previous definitions. Figure 8d shows the curve of  $\ln(J/E2)$  versus 1/E. The slope of the linear fit for the above samples shows an increase in current with increasing electric field, indicating that at high electric fields (1.47–1.85 MV/cm), all three samples are consistent with the *FN* tunneling conduction mechanism. Based on the previous analysis, it can be concluded that all samples are dominated by three main conduction mechanisms. In the lower electric fields,

SE emission dominates, however, in the higher electric fields, PF emission dominates together with FN tunneling.

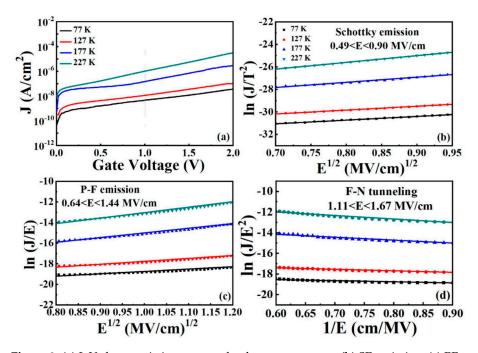

## 3.3.4. Low Temperature J–V Analyses and Conduction Mechanisms

To investigate the variation of CCMs in Sm<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/InP MOS capacitor, low temperature (77-227 K) measurements were performed. The leakage current densities of Sm<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/InP MOS capacitors measured at 1 V were extracted as  $4.64 \times 10^{-9}$ ,  $1.48 \times 10^{-8}$ ,  $1.13 \times 10^{-7}$ , and  $1.02 \times 10^{-6}$  A/cm<sup>2</sup>, corresponding to the temperature range of 77-227 K, respectively. By observing the leakage current densities at different temperatures, the  $Sm_2O_3/Al_2O_3/InP$  gate stack exhibits nearly three orders of magnitude lower leakage current density at 77 K than that measured at room temperature, indicating that the low temperature is favorable for the MOS capacitor to exhibit optimized *J–V* characteristics. Figure 9b-d show the variation of the CCM under substrate injection along with the temperature trend. The extracted important electrical parameters are listed in Table 4. Figure 9b shows the fitted lines for the vertical temperature range suitable for SE emission at lower electric fields (0.49–0.90 MV/cm). The extracted important electrical parameters are listed in Table 4. With increasing temperature, the values of  $\varepsilon_r$  and n calculated from the slope and intercept are (20.39, 4.52), (18.53, 4.31), (10.40, 3.22), and (6.10, 2.47). It can be noted that at extremely low temperature of 77–177 K, these values are completely different from the theoretical values, indicating that SE emission is not the dominant conduction mechanism at lower temperatures. Figure 9c shows the curves in the temperature range 77–227 K compatible with PF emission at higher electric fields (0.64-1.44 MV/cm). Again, it can be noted that  $\varphi_t$  and  $\varepsilon_{0x}$  are not in the expected range of values, indicating that the PF emission is not compatible for all samples at intermediate electric fields of 0.64–1.44 MV/cm. FN tunneling is a potential conduction mechanism because of its dependence on the electric field at low temperatures. Figure 9d shows the fitted line of FN tunneling with a temperature range of 77–227 K at higher electric fields (1.11–1.67 MV/cm), and the established slope indicates that FN tunneling is dominant at low temperatures. In conclusion, the effects of SE emission and PF emission are attenuated due to low temperature, and FN tunneling is used to explain the Sm<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/InP stacked gate dielectric structure showing low drain current density.

**Figure 9.** (a) J–V characteristics measured at low temperature. (b) SE emission, (c) PF emission, and (d) FN tunneling plots for all the samples under substrate injection.

| Т     | J (A/cm <sup>2</sup> ) | ε <sub>r</sub> | п    | ε <sub>ox</sub> | φ <sub>t</sub> (eV) |

|-------|------------------------|----------------|------|-----------------|---------------------|

| 77 K  | $4.64	imes10^{-9}$     | 20.39          | 4.52 | 164.88          | 0.54                |

| 127 K | $1.13	imes10^{-8}$     | 18.53          | 4.31 | 108.14          | 0.53                |

| 177 K | $1.48	imes10^{-7}$     | 10.40          | 3.22 | 42.66           | 0.50                |

| 227 K | $1.02 	imes 10^{-6}$   | 6.10           | 2.47 | 31.05           | 0.47                |

Table 4. S3's MOS capacitors electrical parameters measured at low temperature.

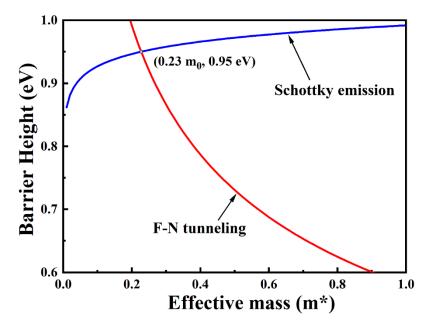

Additionally, the integrated dielectric properties in MOS capacitors can be estimated from two important values, including the electron effective mass  $m_{ox}^*$  and the barrier height  $q\varphi_B$  [50]. The intercept of the SE emission fitting curve described as  $\ln\left(120\frac{m_{0x}^*}{m_0}\right) - \frac{q\varphi_B}{k_BT}$  and the slope of the FN tunneling fitting curve expressed as  $-6.83 \times 10^7 \sqrt{\left(\frac{m_T^*}{m_0}\right)} \varphi_B^3$  can be calculated together with the above two values. By setting the equation  $m_{0x}^* = m_T^*$ , the two key physical quantities  $m_{0x}^*$  and  $q\varphi_B$  of  $\mathrm{Sm}_2\mathrm{O}_3/\mathrm{Al}_2\mathrm{O}_3/\mathrm{InP}$  MOS capacitor are obtained by applying mathematical analysis, which are calculated as 0.23 m<sub>o</sub> and 0.95 eV, respectively. Figure 10 shows the determination of the electron effective mass and barrier height for S3 sample. The smaller  $m_{0x}^*$  and the higher  $q\varphi_B$  are beneficial to obtain better electrical properties and optimized interface quality.

**Figure 10.** The determination of the electron effective mass and barrier height for S3 sample under substrate injection.

## 4. Conclusions

In this work, we explore in detail the effect of ALD-derived laminated interlayers on the interfacial chemistry and transport properties of sputter-deposited  $Sm_2O_3/InP$ gate stacks. It has been found that  $Sm_2O_3/Al_2O_3/InP$  gate stack can obviously prevent the diffusion of the substrate diffusion oxide and substantially optimize the electrical properties of MOS capacitors, including a larger dielectric constant of 14.75, a larger accumulation capacitance, and a lower leakage current density of  $2.87 \times 10^{-6} \text{ A/cm}^2$ . Three different stacked gate dielectric structures are also evaluated by means of conductivity of the interfacial density of states. The results show that the  $Sm_2O_3/Al_2O_3/InP$  stacked gate dielectric achieves the lowest interfacial density of states of  $1.05 \times 10^{13} \text{ cm}^{-2}\text{eV}^{-1}$ . According to the analysis of CCMs, SE emission is dominant in lower electric fields and higher temperature environments, and PF emission as well as F-N tunneling is dominant in higher electric fields. Meanwhile, FN tunneling is the only dominant mechanism at lower temperatures. Also, to evaluate the properties of the whole MOS capacitor in low temperature environment,  $m_{0x}^*$  and  $q\varphi_B$  have been determined by a self-consistent method. These findings are of crucial importance for the future fabrication of high mobility InP-based MOSFET (Metal Oxide Semiconductor Field Effect Transistor) devices.

**Author Contributions:** G.H. and Z.F. conceived and designed the experiments; J.L., J.Y. and L.Q. performed the experiments; S.J., Z.D., Q.G. and G.Z. analyzed the data; J.L. and G.H. wrote the paper. All authors have read and agreed to the published version of the manuscript.

Funding: National Natural Science Foundation of China (11774001) and Anhui Project (Z010118169).

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

Data Availability Statement: The study did not report any data.

Acknowledgments: The authors acknowledge the support from National Natural Science Foundation of China (11774001) and Anhui Project (Z010118169).

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Pelella, M.M.; Fossum, J.G.; Suh, D.; Krishnan, S.; Jenkins, K.A.; Hargrove, M.J. Low-voltage transient bipolar effect induced by dynamic floating-body charging in scaled PD/SOI MOSFET's. *IEEE Electron Dev. Lett.* **1996**, *17*, 196–198. [CrossRef]

- Lauer, I.; Antoniadis, D.A. Enhancement of electron mobility in ultrathin-body silicon-on-insulator MOSFETs with uniaxial strain. IEEE Electron Dev. Lett. 2005, 26, 314–316. [CrossRef]

- 3. Robertson, J.; Wallace, R.M. High-K materials and metal gates for CMOS applications. Mater. Sci. Eng. R 2015, 88, 1–41. [CrossRef]

- 4. Chin, W.C.; Cheong, K.Y. Effects of post-deposition annealing temperature and ambient on RF magnetron sputtered Sm<sub>2</sub>O<sub>3</sub> gate on n-type silicon substrate. *J. Mater. Sci. Mater. Electron.* **2011**, 22, 1816–1826. [CrossRef]

- Stewart, A.D.; Gerger, A.; Gila, B.P.; Abernathy, C.R.; Pearton, S.J. Determination of Sm<sub>2</sub>O<sub>3</sub> GaAs heterojunction band offsets by X-ray photoelectron spectroscopy. *Appl. Phys. Lett.* 2008, *92*, 153511. [CrossRef]

- 6. Dakhel, A.A. Dielectric and optical properties of samarium oxide thin films. J. Alloy. Compd. 2004, 365, 233–239. [CrossRef]

- Mahata, C.; Oh, I.K.; Yoon, C.M.; Lee, C.W.; Seo, J.; Algadi, H. The impact of atomic layer deposited SiO<sub>2</sub> passivation for high-k Ta1-xZrxO on the InP substrate. *J. Mater. Chem. C* 2015, *3*, 10293–10301. [CrossRef]

- Sonnet, A.M.; Hinkle, C.L.; Jivani, M.N.; Chapman, R.A.; Pollack, G.P.; Wallace, R.M.; Vogel, E.M. Performance enhancement of n-channel inversion type In<sub>x</sub>Ga<sub>1-x</sub>As metal-oxide-semiconductor field effect transistor using ex situ deposited thin amorphous silicon layer. *Appl. Phys. Lett.* 2008, *93*, 122109. [CrossRef]

- 9. Yuan, Y.; Yu, B.; Ahn, J.; McIntyre, P.C.; Asbeck, P.M.; Rodwell, M.J.W.; Taur, Y. A Distributed Bulk-Oxide Trap Model for Al<sub>2</sub>O<sub>3</sub> InGaAs MOS Devices. *IEEE Trans. Electron Devices* **2012**, *59*, 2100–2106. [CrossRef]

- 10. Yen, C.F.; Yeh, M.Y.; Chong, K.K.; Hsu, C.F.; Lee, M.K. InP MOS capacitor and E-mode n-channel FET with ALD Al<sub>2</sub>O<sub>3</sub>-based high-k dielectric. *Appl. Phys. A* **2016**, *122*, 1–9. [CrossRef]

- 11. Sun, Y.; Liu, Z.; MacHuca, F.; Pianetta, P.; Spicer, W.E. Optimized cleaning method for producing device quality InP(100) surfaces. *J. Appl. Phys.* **2005**, *97*, 124902. [CrossRef]

- 12. He, G.; Gao, J.; Chen, H.S.; Cui, J.B.; Sun, Z.Q.; Chen, X.S. Modulating the Interface Quality and Electrical Properties of HfTiO/InGaAs Gate Stack by Atomic- Layer-Deposition-Derived Al<sub>2</sub>O<sub>3</sub> Passivation Layer. *ACS Appl. Mater. Interfaces* **2014**, *6*, 22013–22025. [CrossRef] [PubMed]

- 13. Wang, S.K.; Cao, M.; Sun, B.; Li, H.; Liu, H. Reducing the interface trap density in Al<sub>2</sub>O<sub>3</sub>/InP stacks by low-temperature thermal process. *Appl. Phys. Exp.* **2015**, *8*, 091201. [CrossRef]

- 14. Ingrey, S.; Lau, W.M.; McIntyre, N.S.; Sodhi, R. An X-ray photoelectron spectroscopy study on ozone treated InP surfaces. J. Vac. Sci. Technol. A 1987, 5, 1621–1624. [CrossRef]

- 15. Çetin, H.; Ayyildiz, E. The electrical properties of metal-oxide-semiconductor devices fabricated on the chemically etched n-InP substrate. *Appl. Surf. Sci.* 2007, 253, 5961–5966. [CrossRef]

- 16. Lebedev, M.V.; Serov, Y.M.; Lvova, T.V.; Endo, R.; Masuda, T.; Sedova, I.V. InP(1 0 0) surface passivation with aqueous sodium sulfide solution. *Appl. Surf. Sci.* 2020, 533, 147484. [CrossRef]

- 17. Carpenter, M.S.; Melloch, M.R.; Lundstrom, M.S.; Tobin, S.P. Effects of Na<sub>2</sub>S and (NH<sub>4</sub>)<sub>2</sub>S edge passivation treatments on the dark current-voltage characteristics of GaAs pn diodes. *Appl. Phys. Lett.* **1988**, *52*, 2157–2159. [CrossRef]

- 18. Driad, R.; Sah, R.E.; Schmidt, R.; Kirste, L. Passivation of InP heterojunction bipolar transistors by strain controlled plasma assisted electron beam evaporated hafnium oxide. *Appl. Phys. Lett.* **2012**, *100*, 014102. [CrossRef]

- 19. Galatage, R.V.; Dong, H.; Zhernokletov, D.M.; Brennan, B.; Hinkle, C.L.; Wallace, R.M.; Vogel, E.M. Effect of post deposition anneal on the characteristics of HfO<sub>2</sub>/InP metal-oxide-semiconductor capacitors. *Appl. Phys. Lett.* **2011**, *99*, 172901. [CrossRef]

- 20. An, C.H.; Byun, Y.C.; Cho, M.H.; Kim, H. Thermal instability of HfO<sub>2</sub> on InP structure with ultrathin Al<sub>2</sub>O<sub>3</sub> interface passivation layer. *Phys. Status Solidi Rapid Res. Lett.* **2012**, *6*, 247–249. [CrossRef]

- Kakiuchi, H.; Ohmi, H.; Harada, M.; Watanabe, H.; Yasutake, K. Significant enhancement of Si oxidation rate at low temperatures by atmospheric pressure Ar/O<sub>2</sub> plasma. *Appl. Phys. Lett.* 2007, *90*, 151904. [CrossRef]

- 22. Hollinger, G.; Bergignat, E.; Joseph, J.; Robach, Y. On the nature of oxides on InP surfaces. J. Vac. Sci. Technol. A 1985, 3, 2082–2088. [CrossRef]

- 23. Aguirre-Tostado, F.S.; Milojevic, M.; Hinkle, C.L.; Vogel, E.M.; Wallace, R.M.; McDonnell, S.; Hughes, G.J. Indium stability on InGaAs during atomic H surface cleaning. *Appl. Phys. Lett.* **2008**, *92*, 171906. [CrossRef]

- 24. Murphy, A.B. Band-gap determination from diffuse reflectance measurements of semiconductor films, and application to photoelectrochemical water-splitting. *Sol. Energy Mater. Sol. Cells* **2007**, *91*, 1326–1337. [CrossRef]

- 25. Jaggernauth, A.; Mendes, J.C.; Silva, R.F. Atomic layer deposition of high-: κ layers on polycrystalline diamond for MOS devices: A review. J. Mater. Chem. C 2020, 8, 13127–13153. [CrossRef]

- Kraut, E.A.; Grant, R.W.; Waldrop, J.R.; Kowalczyk, S.P. Precise Determination of the Valence-Band Edge in X Ray Photoemission Spectra. *Phys. Rev. Lett.* 1980, 44, 1620–1623. [CrossRef]

- 27. Mahata, C.; Byun, Y.-C.; An, C.-H.; Choi, S.; An, Y.; Kim, H. Comparative study of atomic-layer-deposited stacked (HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>) and nanolaminated (HfAlO<sub>x</sub>) dielectric on In0.53Ga0.47As. *ACS Appl. Mater. Interfaces* **2013**, *5*, 4195–4201. [CrossRef]

- Çiçek, O.; Durmuş, H.; Altındal, Ş. Identifying of series resistance and interface states on rhenium/n-GaAs structures using C-V-T and G/ω-V-T characteristics in frequency ranged 50 kHz to 5 MHz. J. Mater. Sci. Mater. Electron. 2020, 31, 704–713. [CrossRef]

- 29. Yoshioka, H.; Nakamura, T.; Kimoto, T. Accurate evaluation of interface state density in SiC metal-oxide-semiconductor structures using surface potential based on depletion capacitance. *J. Appl. Phys.* **2012**, *111*, 04C100. [CrossRef]

- Mutale, A.; Deevi, S.C.; Yilmaz, E. Effect of annealing temperature on the electrical characteristics of Al/Er<sub>2</sub>O<sub>3</sub>/n-Si/Al MOS capacitors. *J. Alloy. Compd.* 2021, 863, 158718. [CrossRef]

- Varzgar, J.B.; Kanoun, M.; Uppal, S.; Chattopadhyay, S.; Tsang, Y.L.; Escobedo-Cousins, E.; Olsen, S.H.; O'Neill, A.; Hellström, P.E.; Edholm, J.; et al. Reliability study of ultra-thin gate oxides on strained-Si/SiGe MOS structures. *Mater. Sci. Eng. B* 2006, 135, 203–206. [CrossRef]

- 32. Foster, A.S.; Lopez Gejo, F.; Shluger, A.L.; Nieminen, R.M. Vacancy and interstitial defects in hafnia. *Phys. Rev. B* 2002, 65, 1741171–17411713. [CrossRef]

- Liu, J.W.; Oosato, H.; Da, B.; Koide, Y. Fixed charges investigation in Al<sub>2</sub>O<sub>3</sub>/hydrogenated-diamond metal-oxide-semiconductor capacitors. *Appl. Phys. Lett.* 2020, 117, 163502. [CrossRef]

- 34. Shahinur Rahman, M.; Evangelou, E.K.; Konofaos, N.; Dimoulas, A. Gate stack dielectric degradation of rare-earth oxides grown on high mobility Ge substrates. *J. Appl. Phys.* **2012**, *112*, 094501. [CrossRef]

- 35. Wang, D.; He, G.; Hao, L.; Qiao, L.; Fang, Z.; Liu, J. Interface Chemistry and Dielectric Optimization of TMA-Passivated high-k/Ge Gate Stacks by ALD-Driven Laminated Interlayers. *ACS Appl. Mater. Interfaces* **2020**, *12*, 25390–25399. [CrossRef] [PubMed]

- 36. Engel-Herbert, R.; Hwang, Y.; Stemmer, S. Comparison of methods to quantify interface trap densities at dielectric/III-V semiconductor interfaces. J. Appl. Phys. 2010, 108, 124101. [CrossRef]

- Lin, H.C.; Wang, W.E.; Brammertz, G.; Meuris, M.; Heyns, M. Electrical study of sulfur passivated In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitor and transistor with ALD Al<sub>2</sub>O<sub>3</sub> as gate insulator. *Microelectron. Eng.* 2009, *86*, 1554–1557. [CrossRef]

- 38. Martens, K.; Wang, W.; De Keersmaecker, K.; Borghs, G.; Groeseneken, G.; Maes, H. Impact of weak Fermi-level pinning on the correct interpretation of III-V MOS C-V and G-V characteristics. *Microelectron. Eng.* 2007, *84*, 2146–2149. [CrossRef]

- Qiao, L.; He, G.; Hao, L.; Lu, J.; Gao, Q.; Zhang, M.; Fang, Z. Interface Optimization of Passivated Er<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/InP MOS Capacitors and Modulation of Leakage Current Conduction Mechanism. *IEEE Trans. Electron Devices* 2021, 68, 2899–2905. [CrossRef]

- Carter, A.D.; Mitchell, W.J.; Thibeault, B.J.; Law, J.J.M.; Rodwell, M.J.W. Al<sub>2</sub>O<sub>3</sub> growth on (100) In<sub>0.53</sub>Ga<sub>0.47</sub> as initiated by cyclic trimethylaluminum and hydrogen plasma exposures. *Appl. Phys. Exp.* **2011**, *4*, 091102. [CrossRef]

- Yen, C.-F.; Lee, M.-K. Very Low Leakage Current of High Band-Gap Al<sub>2</sub>O<sub>3</sub> Stacked on TiO<sub>2</sub>/InP Metal–Oxide–Semiconductor Capacitor with Sulfur and Hydrogen Treatments. *Jpn. J. Appl. Phys.* 2012, *51*, 081201.

- 42. Chen, Y.-T.; Zhao, H.; Yum, J.H.; Wang, Y.; Lee, J.C. Metal-oxide-semiconductor field-effect-transistors on indium phosphide using HfO<sub>2</sub> and silicon passivation layer with equivalent oxide thickness of 18 Å. *Appl. Phys. Lett.* **2009**, *94*, 213505. [CrossRef]

- Suzuki, R.; Taoka, N.; Yokoyama, M.; Lee, S.; Kim, S.H. 1-nm-capacitance-equivalent-thickness HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/InGaAs metaloxide-semiconductor structure with low interface trap density and low gate leakage current density. *Appl. Phys. Lett.* 2012, 100, 132906. [CrossRef]

- 44. Shahrjerdi, D.; Rotter, T.; Balakrishnan, G. Fabrication of Self-Aligned Enhancement-Mode MOSFETs With Gate Stack. *IEEE Electron Dev. Lett.* 2008, *29*, 557–560. [CrossRef]

- 45. He, G.; Zhang, L.D.; Liu, M.; Sun, Z.Q. HfO<sub>2</sub>-GaAs metal-oxide-semiconductor capacitor using dimethylaluminumhydridederived aluminum oxynitride interfacial passivation layer. *Appl. Phys. Lett.* **2010**, *97*, 223501. [CrossRef]

- Yang, M.; Wang, H.; Ma, X.; Gao, H.; Wang, B. Effect of nitrogen-accommodation ability of electrodes in SiN<sub>x</sub>-based resistive switching devices. *Appl. Phys. Lett.* 2017, 111, 223510. [CrossRef]

- 47. Kim, J.; Krishnan, S.A.; Narayanan, S.; Chudzik, M.P.; Fischetti, M.V. Thickness and temperature dependence of the leakage current in hafnium-based Si SOI MOSFETs. *Microelectron. Reliab.* **2012**, *52*, 2907–2913. [CrossRef]

- 48. Sadeq, M.S.; Morshidy, H.Y. Effect of samarium oxide on structural, optical and electrical properties of some alumino-borate glasses with constant copper chloride. *J. Rare Earths* **2020**, *38*, 770–775. [CrossRef]

- 49. Paskaleva, A.; Bauer, A.J.; Lemberger, M.; Zürcher, S. Different current conduction mechanisms through thin hlgh-k Hf <sub>x</sub>Ti<sub>y</sub>Si<sub>z</sub>O films due to the varying Hf to Ti ratio. *J. Appl. Phys.* **2004**, *95*, 5583–5590. [CrossRef]

- 50. Chiu, F.C. Interface characterization and carrier transportation in metal/ HfO<sub>2</sub>/silicon structure. *J. Appl. Phys.* 2006, 100, 114102. [CrossRef]