Article

# Low Temperature (Down to 6 K) and Quantum Transport Characteristics of Stacked Nanosheet Transistors with a High-K/Metal Gate-Last Process

Xiaohui Zhu <sup>1,2,3</sup>, Lei Cao <sup>1,2,3</sup>, Guilei Wang <sup>4</sup> and Huaxiang Yin <sup>1,2,3,\*</sup>

- <sup>1</sup> Integrated Circuit Advanced Process R&D Center, Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China; zhuxiaohui@ime.ac.cn (X.Z.); caolei@ime.ac.cn (L.C.)

- <sup>2</sup> School of Integrated Circuits, University of Chinese Academy of Sciences, Beijing 100049, China

- <sup>3</sup> Key Laboratory of Fabrication Technologies for Integrated Circuits, Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China

- <sup>4</sup> Hefei National Laboratory, University of Science and Technology of China, Hefei 230088, China; wangguilei@hfnl.cn

- \* Correspondence: yinhuaxiang@ime.ac.cn

**Abstract:** Silicon qubits based on specific SOI FinFETs and nanowire (NW) transistors have demonstrated promising quantum properties and the potential application of advanced Si CMOS devices for future quantum computing. In this paper, for the first time, the quantum transport characteristics for the next-generation transistor structure of a stack nanosheet (NS) FET and the innovative structure of a fishbone FET are explored. Clear structures are observed by TEM, and their low-temperature characteristics are also measured down to 6 K. Consistent with theoretical predictions, greatly enhanced switching behavior characterized by the reduction of off-state leakage current by one order of magnitude at 6 K and a linear decrease in the threshold voltage with decreasing temperature is observed. A quantum ballistic transport, particularly notable at shorter gate lengths and lower temperatures, is also observed, as well as an additional bias of about 1.3 mV at zero bias due to the asymmetric barrier. Additionally, fishbone FETs, produced by the incomplete nanosheet release in NSFETs, exhibit similar electrical characteristics but with degraded quantum transport due to additional SiGe channels. These can be improved by adjusting the ratio of the channel cross-sectional areas to match the dielectric constants.

Keywords: SOI stacked nanosheet; cryo-CMOS; quantum transport; fishbone FET

# 1. Introduction

At present, constructing high-performance semiconductor quantum devices with advanced complementary metal oxide semiconductor (CMOS) technology is one of critical methods for developing modern quantum computing systems. There are a series of developed silicon qubits based on specific SOI planar, fin and nanowire (NW) field-effect transistors (FETs) that have achieved multi-quantum dot characteristics and high-fidelity gate operation behaviors based on general single-quantum theory [1–3]. These results suggest the feasibility of Si quantum dot devices developed for advanced Si MOS devices or processes.

With the continuous development of Moore's Law and the scaling of CMOS technology nodes, MOS transistor structures are continuing to evolve [4,5]. Si FinFETs with a high-k/metal gate-last (HK/MG-Last) process is a mainstream CMOS manufacturing technology currently being mass-fabricated [6,7]. Nanosheet (NS) FETs exhibit better gate control, higher integration density and good process compatibility with current massmanufacturing processes, and they are considered to be the next-generation mainstream MOSFET structure beyond FinFETs [8–10]. Exploring the implementation path of Si quantum devices by utilizing the low-temperature quantum properties of more advanced Si

Citation: Zhu, X.; Cao, L.; Wang, G.; Yin, H. Low Temperature (Down to 6 K) and Quantum Transport Characteristics of Stacked Nanosheet Transistors with a High-K/Metal Gate-Last Process. *Nanomaterials* **2024**, *14*, 916. https://doi.org/10.3390/ nano14110916

Academic Editor: Barbara Bonelli

Received: 9 April 2024 Revised: 8 May 2024 Accepted: 16 May 2024 Published: 23 May 2024

**Copyright:** © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). MOS devices can not only break through the integration scale challenges of traditional Si quantum devices with specific structures, but this can also promote the emergence of quantum computing with new possibilities in the future.

Due to the greater gate-field control of stacked ultra-thin Si channels, their quantum constraints are expected be more pronounced. Some first-principles and density functional theory (DFT) computational methods have been utilized to calculate the electrical properties of stacked NSs and have been employed to guide the design of stacked NS devices [11,12]. Unfortunately, although there have been some studies on the low-temperature characteristics of NS transistors for specific channel structures and customized processes [13–19], there is little research on the low-temperature carrier transport characteristics of NS transistors with a general structure using mainstream fabrication processes based on HK/MG-last technologies. Furthermore, data on the quantum transport characteristics and relative quantum dot operation behavior of NS devices are also lacking.

In this paper, based on the developed SOI stacked nanosheet (NS) transistors with a HK/MG-last process, the electrical and quantum transport characteristic of NS transistors are systematically investigated at ultra-low temperatures (down to 6 K). The differences in these characteristics under different process and structural conditions were also compared, which are well explained with hybrid simulation methods.

#### 2. Materials and Methods

The stacked nanosheet (NS) transistors are fabricated on the 8-inch CMOS pilot line of the Institute of Microelectronics, Chinese Academy of Sciences, and the developed fabrication process is highly compatible with those adopted for future mass-manufacturing processes [10,20]. The transistors are fabricated on an 8-inch SOI wafer with a diameter of 200 mm. Firstly, the top silicon thickness of the SOI substrate is reduced to 40 nm using the sacrificial oxidation method. Subsequently, three-layer SiGe/Si superlattice structures with a thickness of 12 nm/18 nm were grown on it using epitaxy technology. A fin is formed using sidewall transfer technology and the stacked portion is exposed, while a dummy ploy-Si gate stack is patterned by electron beam and reactive ion etching. The self-aligned source–drain is formed by using a silicon nitride spacer and HDD ion implantation (BF+, dose of  $5 \times 10^{20}$  and energy of 5 keV) along with an RTA at 850 °C for 30 s. Due to the absence of traditional LDD injection, a natural bottom-doping region is formed in the doping region, which may form a potential barrier under specific conditions.

After a poly open polish (POP) process and dummy gate-stack removal, the SiGe layers in the channel are highly selectively etched from the fin with a mixture of corrosion solutions, which finally cause the formation of stacked Si NS channels. Another innovated method has been developed in this process flow. With the partial etching of the SiGe layers in the channel, a special fishbone transistor structure was also developed for better NS device performance, which has been mentioned in our previous work [21]. After the nanosheet channel release, the multi-layered HK/MG structure was formed via the atomic layer deposition (ALD) process. Finally, the metal contact process for interconnection was performed.

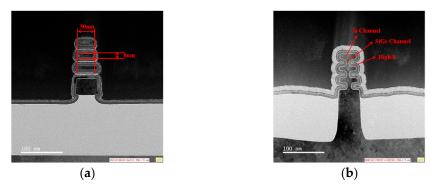

The device structures were observed by dark-field transmission electron microscopy (TEM), and the results obtained are depicted in Figure 1. Clear observation of triple-stacked channels is achieved in the stacked NS, while in the fishbone FET, residual SiGe channels are observed in addition to the stacked channels. The structural parameters of the stacked nanosheets and the distinct channels in the fishbone FET are also annotated. The electrical characteristics of this SOI stacked NS FET device were measured in the vacuum chamber at temperatures ranging from 6 K to 300 K with the Lake Shore CRX-4K system and 4200-SCS semiconductor parameter analyzer (Lake Shore Cryotronics, Westerville, OH, USA).

**Figure 1.** Cross-sectional TEM of the SOI stacked NS transistor with HK/MG process. (**a**) Ordinary SOI stacked NS transistor; (**b**) Fishbone transistor.

#### 3. Results

#### 3.1. Low-Temperature Electrical Characteristics of SOI Stacked NS FET

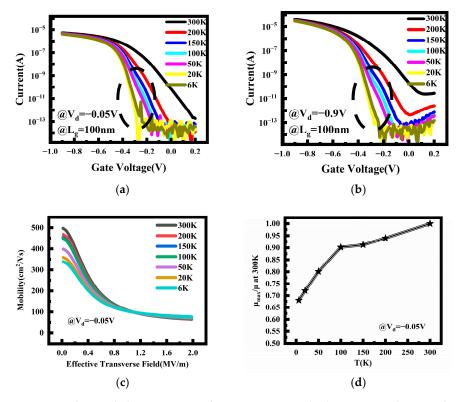

The transfer characteristics curves of a P-type SOI stacked NS FET with a gate length of 100 nm are depicted in Figure 2. Figure 2a,b corresponds to the device operation in the linear region ( $V_d = -0.05$  V) and saturation region ( $V_d = -0.9$  V), respectively. Both scenarios exhibit typical transistor current characteristics. Figure 2c displays the low-field mobility at  $V_d = -0.05$  V, revealing a rapid decrease in the low-field mobility with an increasing effective transverse electric field, along with the observation of a saturation electric field of 1.2–1.6 MV/m. The relationship between the maximum mobility and temperature is plotted in (d). Due to the higher doping concentration in the channel, the freeze-out effect of carriers predominates with regard to mobility, resulting in a decrease in the maximum mobility with decreasing temperature. The reduction in mobility is relatively minor at temperatures above 100 K. However, as the temperature drops below 100 K, the freeze-out effect of carriers intensifies, leading to a rapid decline in mobility.

**Figure 2.** Electrical characteristics of a P-type SOI stacked NS FET with a gate length of 100 nm; (a)  $V_d = -0.05$  V; (b)  $V_d = -0.9$  V; (c) Low-field carrier mobility vs. the effective transverse field at  $V_d = -0.05$  V; (d) The maximum value of the mobility vs. temperature at  $V_d = -0.05$  V.

As the temperature decreases from 300 K to 6 K, there is a noticeable decrease in the current within the device. In contrast, the off-state current decreases rapidly as the temperature decreases to 50 K. This is primarily due to the corresponding increase in the band-gap width of silicon material and the disappearance of some impurity energy levels as the temperature decreases. This implies the gradual closure of some originally open conduction channels. While the on-state current also decreases, its reduction rate is relatively slower. The main influencing factor is the rapid decrease in carrier concentration within the channel. This difference results in a rapid increase in the device's on–off ratio, which is the ratio of the on-state current to the off-state current, with decreasing temperature.

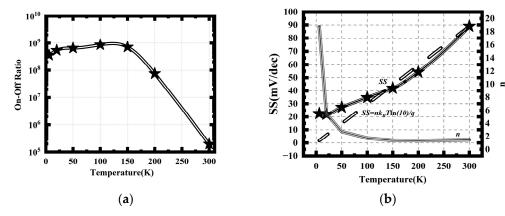

The on-off ratio increases rapidly with decreasing temperature above 150 K, ranging from  $10^5$  at 300 K to  $10^9$  at 150 K, as shown in Figure 3a. When the temperature drops below 100 K, the change in the off-state current with temperature becomes weaker, which is consistent with the best characteristics of CMOS mentioned in previous literature at liquidnitrogen temperature. Most conduction channels brought about by defects and impurity energy levels have already closed, which maximizes the on-off ratio. For temperatures below 100 K, the on-off ratio remains essentially constant. This is because both the off-state and on-state currents weaken in response to temperature, resulting in little variation in the on-off ratio.

Figure 3. Temperature dependence of CMOS parameters; (a) On-off ratio; (b) SS.

Due to the improvement in subthreshold characteristics, the SS of the SOI stacked NS FET decreases with decreasing temperature that is above approximately 50 K, as shown in Figure 3b. At 300 K, the device's *SS* is around 90 mV/dec, but at 50 K, it drops below 30 mV/dec, significantly below the physical limit at room temperature. In fact, SS exhibits a linear relationship with temperature, which can be expressed by the following formula [22]:

$$SS = nk_B T \frac{ln(10)}{q} \tag{1}$$

The coefficient *n* is related to the device interface defect charges, and for this device, *n* is 1.5 at 300 K. When the temperature decreases to 100 K, the variation in *n* is small, and the relationship between *SS* and temperature also exhibits a basically linear relationship. However, when the temperature drops to 50 K and below, attributed to enhanced interface state effects, the value of *n* starts to increase rapidly, and *SS* also saturates at about 20 K. It has been reported in previous literature that optimizing the interface can improve the *SS* [15]. The minimum value of the *SS* is approximately 22 mV/dec in this device, which is consistent with the findings obtained from testing traditional bulk silicon NS devices [19].

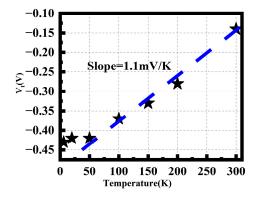

Threshold voltage is another crucial parameter for transistors. As the temperature decreases, the threshold voltage becomes more negative, as shown in Figure 4. Above 50 K, the threshold voltage exhibits a linear relationship with temperature, with a slope of

approximately 1.1 mV/K. The temperature dependence of the threshold voltage for p-type MOSFETs can be expressed by the following formula [23]:

$$\frac{dV_t}{dT} = \frac{d\Phi_F}{dT} \approx 8.63 \times 10^{-5} \left[ \ln N_d - 38.2 - \frac{3}{2} (1 + \ln T) \right]$$

(2)

The temperature coefficient slope values calculated for this device range from 0.84 to 1.31 mV/K within the temperature range of 50–300 K. These calculations validate the reasonableness of the fitted value of 1.1 mV/K. The temperature variation of the threshold voltage is primarily associated with the temperature change of the material's band gap. At extremely low temperatures, the band-gap width of silicon material increases, resulting in an increase in the threshold voltage. The saturation of the threshold voltage increase may be attributed to the influence of defect levels. Additionally, some significant quantum effects also begin to play a role, further weakening the temperature dependence of the threshold voltage, leading to saturation of the threshold voltage at extremely low temperatures.

Figure 4. Temperature dependence of the threshold voltage. Blue Line: Linear Fitting.

Overall, at low temperatures down to 6 K, the improved mobility of carriers within the crystal enhances the on-state current, while the closure of some leakage paths due to partial freezing results in a significant reduction in the off-state current. Consequently, this enhances the device's switching speed and characteristics. Simultaneously, the *SS* also decreases rapidly. Therefore, SOI stacked NS FET devices exhibit superior performance at low temperatures, potentially providing advantages for low-power electronic devices and high-performance computing.

## 3.2. Quantum Transport at Low Temperature for SOI Stacked NS FETs

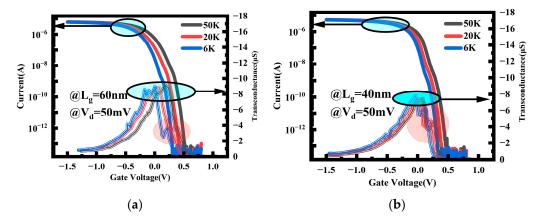

The transfer characteristics curves shown in Figure 2 reveal a unique current behavior, displaying step-like currents induced by quantum effects. This current characteristic is more pronounced in devices with shorter gate lengths. To further understand this phenomenon, the current characteristics of devices with gate lengths of 40 nm and 60 nm below 50 K are plotted in Figure 5, where the step-like currents generated by quantum effects can be clearly observed. The transconductance in two scenarios is also plotted in Figure 5, clearly demonstrating non-smooth transconductance peaks (highlighted in the red circles) resulting from current steps outside the main peak. This current characteristic is particularly significant for devices with shorter gate lengths (40 nm) and lower temperatures (6 K), indicating a quantum ballistic transport result.

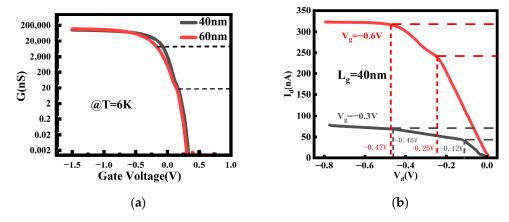

The channel conductance as a function of gate voltage at a temperature of 6 K was plotted in Figure 6, along with the  $I_d$ – $V_d$  graph for the device with a channel length of 40 nm. The current steps induced by quantum transport are observed to be more pronounced. The  $I_d$ – $V_d$  characteristic also exhibits a step-like behavior in Figure 6b, with different slopes of the channel current at different voltage regimes. This is because, as  $V_d$  changes, the drain's Fermi level also varies. When the Fermi level crosses the bottom of the sub-band available for current conduction, new current transport modes emerge. Consequently,

the slope of the current–voltage curve exhibits a discontinuity at this point. Due to the adoption of ultra-thin NS channels, compared with larger-sized nanowire and nanosheet channels [24,25], the quantum transport effect is more prominent, allowing for the more pronounced current steps resulting from ballistic transport to be observed.

Figure 5. Ballistic transport characteristics of 60 nm (a) and 40 nm (b) gate-length devices below 50 K.

**Figure 6.** (a) The channel conductance as a function of gate voltage at a temperature of 6 K; (b)  $I_d - V_d$  graph for the device with a channel length of 40 nm.

To further understand this phenomenon, the Wharam formula can be introduced to calculate channel conductance [26]:

$$G = \frac{2e^2}{h} \sum_i T_i \tag{3}$$

where  $T_i$  is the transmission coefficient of the *i* sub-band. This formula explicitly reveals the relationship between the conductivity and the transmission coefficients of each sub-band. For conductivity, as the gate voltage increases, new sub-bands are triggered to participate in current transport, leading to a significant change in channel conductivity. When the gate voltage is low, only the lowest energy level sub-band participates in transport, resulting in relatively low channel conductivity. However, as the gate voltage increases, more sub-bands are excited and participate in current transport, causing the conductivity to gradually increase, eventually exhibiting the observed step-like conductivity characteristic in Figure 6a.

Under fixed gate voltage conditions, the current variation in relation to the source– drain voltage can be described by a simple formula:

$$I_d = M \frac{2e^2}{h} V_d \tag{4}$$

where M is the number of sub-bands involved in current transport. A higher gate voltage implies the involvement of more sub-bands in transport, indicating a larger value of current, thereby resulting in a significant increase in the current. The value of M in this experiment can be calculated to be between 5 and 21, which slightly exceeds the typical range for one-dimensional transport (between 1 and 10) and demonstrating that the device exhibits non-typical partial one-dimensional transport characteristics. As  $V_d$  changes, the drain's Fermi level also varies. When the Fermi level crosses the bottom of the sub-band available for current conduction, new current transport modes emerge. Consequently, the slope of the current–voltage curve undergoes a discontinuity at this point.

In Figure 6b, it is observed that the height of the first step (about 43.35 nA for  $V_g = -0.3$  V and 242.93 nA for  $V_g = -0.6$  V) is approximately twice the height of the second step (about 23.51 nA for  $V_g = -0.3$  V and 103.28 nA for  $V_g = -0.6$  V). This is determined by the band structure of silicon. The first sub-band of the silicon conduction band has a doubly degenerate bottom, meaning that two energy levels at the bottom of the conduction band have the same energy. As the voltage increases, both of these degenerate levels must be filled simultaneously for electrons to enter the next transport sub-band. This is reflected in the current and conductivity plots as the height of the first step is approximately twice the height of the second step.

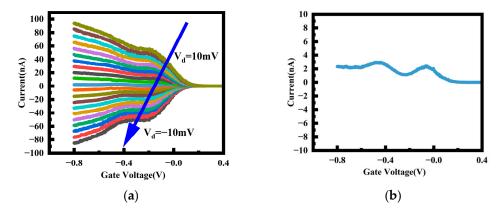

Furthermore, the device with a gate length of 40 nm was measured under low bias conditions to investigate its transport characteristics over a larger range in Figure 7a, revealing distinct step-like changes in the current with variations in the gate and drain voltages. This step-like current phenomenon directly reflects partial one-dimensional quantum transport. Notably, the situation is largely symmetric for both positive and negative values of  $V_d$ . However, Figure 7b displays the current at  $V_d = 0$  V, revealing that there is still a non-zero current present when the source–drain voltage is 0. This phenomenon has also been observed in other literature; for instance, in circular nanowires [23]. It arises from the asymmetric triangular potential barrier between the source and drain [27]. For a triangular potential barrier, the tunneling probabilities in the two directions are different. In this case, the triangular barrier provides a potential difference of about 1.3 mV. When the difference in tunneling probabilities on the two sides of the trapezoidal or triangular potential barrier is significant, this current can become quite substantial.

**Figure 7.** (a)  $I_d-V_g$  of a device with  $L_g = 40$  nm at 6 K temperature (The voltage  $V_d$  varies from 10 mV to -10 mV along the direction of the blue arrow); (b) Current at 0 V.

### 3.3. Comparison of Quantum Properties between NS and Fishbone Transistors

The structure of a fishbone FET is illustrated in Figure 1b. In a fishbone FET, there exists deliberately designed SiGe fin channels between stacked Si NS channels for the developed partial removal process of SiGe [21]. The proposed fishbone FET not only exhibits a significantly enhanced driving current but also provides a good balance between the performances of n-type and p-type Fishbone FETs with little extra process cost.

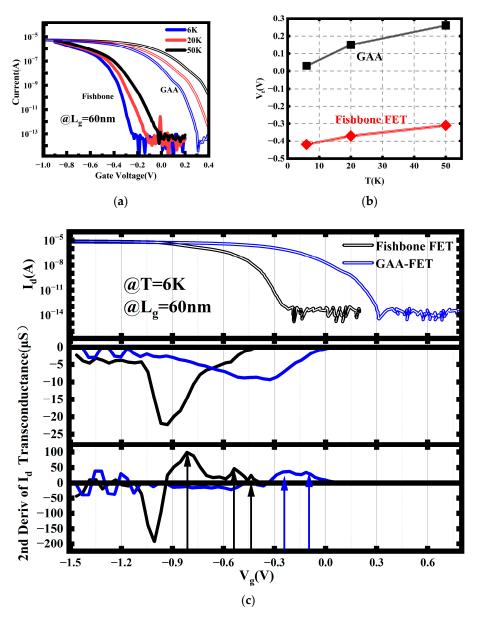

The characteristics of the fishbone FET at low temperatures are depicted in Figure 7a. The current of NS devices with the same gate length at 6 K is also plotted in the figure for

comparison. For the fishbone FET, its overall current trend is like that of the NS device with the same gate length. By utilizing the constant current method to extract the threshold voltage at a current of  $1 \times 10^{-8}$  A, a variation of the threshold voltage with temperature is obtained, as shown in Figure 7b. It can be observed that the threshold voltage of the fishbone FET is shifted further left compared with the NS device. This is because the gate is no longer fully surrounding, which results in weakened gate control over the channel that require higher voltages for device activation, thus shifting the threshold voltage to the left. As the temperature decreases, the threshold voltage of the fishbone FET slightly decreases. When the temperature decreases from 50 K to 6 K, the threshold voltage changes from -0.31 V to -0.42 V. In contrast, the threshold voltage of the NS FET changes from 0.26 V to 0.03 V. The temperature response of the fishbone FET is weaker compared with that of the NS FET, as the presence of the SiGe channel introduces additional interfaces and interface states. These additional interface states partially offset the threshold voltage shift caused by the temperature reduction.

Further observation of the current curves reveals that for the fishbone FET, there exists a current staircase region like that of the stacked NS FET, but the variation within the current staircase region is more complex compared with that of the stacked NS FET. To further investigate the current of the fishbone FET at 6 K and to better visualize its changes, the transconductance values were calculated. To provide a clearer representation of the transconductance variation, the derivative of the transconductance with respect to gate voltage, i.e., the second derivative of the current with respect to gate voltage, is also plotted in Figure 8c.

The current and transconductance of both the fishbone FET and the stacked NS FET exhibit similar characteristics; both currents gradually increase and tend to saturate at higher gate voltages, while the transconductance shows a prominent peak. However, their shapes differ; the transconductance peak of the stacked NS FET appears as a relatively flat and broad peak, whereas that of the fishbone FET is a narrower and sharper peak. This is because, for the stacked NS FET, strong electric fields exist at the four corners, causing them to open first. Then, as the gate voltage increases, other parts of the channel gradually open, resulting in a relatively long process and hence a broad, flat transconductance peak. In contrast, the presence of additional SiGe/Si interfaces and SiGe channels in the fishbone FET, along with more corners, leads to faster inversion at the corners due to the strong electric fields. As a result, the current quickly saturates after transistor turn-on, leading to a sharper transconductance peak.

The stacked NS FET, due to its high symmetry, exhibits fewer artifacts in its transconductance peak. The image presents typical features of partial one-dimensional ballistic transport. However, in contrast, the transconductance of the fishbone FET displays richer fine structures than the stacked NS FET, which is attributable to the disruption of vertical device symmetry by the additional SiGe channel. The intricate structure of the transconductance peak arises from the superposition of currents from various channels, such as the main channel and the vertical channels. This results in more peaks in the second derivative of the current and even finer structures between the two peaks in the fishbone FET.

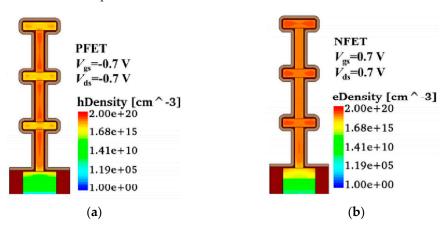

The electrical conductance characteristics were investigated with TCAD simulation tools. The simulation was conducted using Sentaurus TCAD 2017, developed by Synopsys. The structural parameters of the fishbone FET were set as follows. The width of the silicon nanosheet was 50 nm, and the height was 8 nm. The width of the SiGe channel was 8 nm, and the height was 75 nm. To qualitatively illustrate the distribution of carriers in the vertical channel, the height of the SiGe layer was set higher than in the experiments to make the carrier distribution clearer. It is evident that besides the main channel of the Si nanowire, the vertical SiGe channel also contributes to current transport. The carrier distribution maps in Figure 9 clearly show the carrier accumulation in the SiGe channel.

**Figure 8.** (a)  $I_d-V_g$  characteristics and (b) threshold voltage of the fishbone FET. (c) Current and transconductance and the second-order derivative of the current of the fishbone FET and the NS at 6 K. Arrows: The peak of the 2nd derivative of the current.

Figure 9. The carrier distribution of the fishbone FET. (a) PFET; (b) NFET.

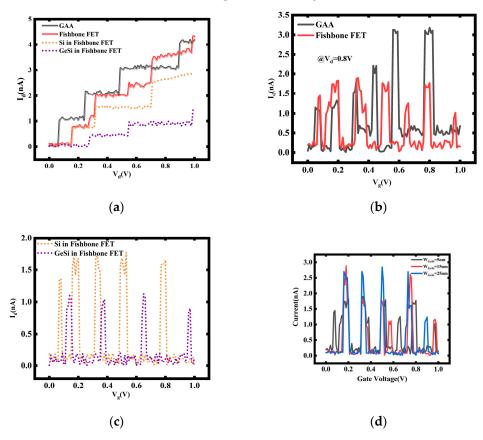

Another simulation was also conducted. In this case, the nanosheet width and height were set to 50 nm and 8 nm, respectively, and the height of the SiGe channel was set to 12 nm. The width of the SiGe channel,  $W_{SiGe}$ , was set to 5 nm. Two 2 nm thick SiO<sub>2</sub> layers were placed as potential barriers between the source–drain and the channel of the device, respectively. The stacked NS FET with the same nanosheet structural parameters was also included in the calculation. After performing simple TCAD simulations, we extracted the band structure and carrier distribution parameters from the results. Treating the device as a quantum dot, we utilized the Wentzel–Kramers–Brillouin (WKB) theory to calculate the tunneling capacitance and tunneling resistance. Subsequently, these parameters were incorporated into the quantum transport equations to obtain the quantum characteristics of the device [28–31]. The results are presented in Figure 10.

**Figure 10.** The current obtained through the master equation model simulation includes the following: (a)  $I_d - V_d$  for  $W_{SiGe} = 5 \text{ nm}$ ; (b)  $I_d - V_g$  for  $W_{SiGe} = 5 \text{ nm}$ ; (c) the contribution of Si and SiGe channels to  $I_d - V_g$  for  $W_{SiGe} = 5 \text{ nm}$ ; (d)  $I_d - V_g$  for different  $W_{SiGe}$  values.

The contributions of quantum current from the SiGe channel are evident from the dashed lines in Figure 10a,c. Due to the differing band structures of the Si main channel and the vertical SiGe channel, the positions of the current steps and conductance peaks resulting from quantum effects are also different. The superposition of these effects makes the current behavior of the fishbone transistor more complex compared with the stacked NS FET.

Furthermore, simulations are conducted with different widths of the SiGe channel, as shown in Figure 10d. It is observed that when the SiGe channel width  $W_{SiGe} = 25$  nm, the current peaks in the  $I_d$ – $V_g$  curve do not exhibit significant additional peaks, unlike the other two cases, where the peaks appear more scattered.

This is because with a SiGe channel width of 25 nm, the cross-sectional area of the SiGe channel is  $300 \text{ nm}^2$ , while the cross-sectional area of the Si channel is  $400 \text{ nm}^2$ . The ratio between them is 1.33, which is close to the ratio between the dielectric constants of SiGe and silicon (1.0~1.36). Therefore, their tunneling capacitance values are also

similar. As tunneling capacitance couples with the source–drain, it implies that the overall quantum characteristics of the two channels are similar, resulting in improved mixed current characteristics when combined. This suggests that adjusting the ratio of the cross-sectional areas of channels made of different materials to match the ratio of their dielectric constants can match their quantum characteristics, thus obtaining better device performance.

## 4. Conclusions

In summary, this study experimentally investigated the low-temperature electrical and quantum characteristics of SOI stacked NS and innovated fishbone transistors. The NS devices exhibit much improved switching characteristics, especially in the off-state leakage current at ultra-low temperatures (6 K). Additionally, the threshold voltage demonstrates a linear decrease with decreasing temperature above 50 K, exhibiting excellent agreement with theoretical predictions. A quantum ballistic transport characteristic is also observed in the transistor at ultra-low temperatures, particularly evident in shorter gate lengths and lower temperatures. An abrupt change in the slope of the current-voltage relationship occurs that reflects the involvement of new sub-bands in transport with the NS structure. Additionally, a current under zero bias exists, which is thought to be indicative of the presence of the asymmetric triangular potential barrier. The fishbone FETs demonstrate similar electrical behaviors to SOI NS devices but exhibit degraded quantum transport characteristics at ultra-low temperature due to the existence of SiGe fin channels between the Si NSs, which may result in the formation of additional peaks in the transconductance plot that arise from the different quantum effects in channels made of different materials. With a developed hybrid simulation approach by using TCAD and a simplified master equation, the quantum characteristics can be improved by adjusting the ratio of the cross-sectional areas of channels made of different materials to match the ratio of their dielectric constants.

**Author Contributions:** Conceptualization, X.Z.; methodology, X.Z. and L.C.; investigation, X.Z. and L.C.; data, X.Z.; writing—original draft preparation, X.Z.; writing—review and editing, H.Y. and G.W.; supervision, H.Y. and G.W.; project administration, H.Y.; funding acquisition, H.Y. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by the Strategic Priority Research Program of the Chinese Academy of Sciences (Grant No. XDA0330302) and Innovation Program for Quantum Science and Technology (Project ID: 2021ZD0302301).

**Data Availability Statement:** The data presented in this study are available on request from the corresponding author.

Acknowledgments: We thank the Integrated Circuit Advanced Process Center (ICAC) at the Institute of Microelectronics of the Chinese Academy of Sciences for the devices fabricated on their advanced 200 mm CMOS platform.

Conflicts of Interest: The authors declare no conflicts of interest.

# References

- Voisin, B.; Nguyen, V.H.; Renard, J.; Jehl, X.; Barraud, S.; Triozon, F.; Vinet, M.; Duchemin, I.; Niquet, Y.-M.; de Franceschi, S.; et al. Few-electron edge-state quantum dots in a silicon nanowire field-effect transistor. *Nano Lett.* 2014, 14, 2094–2098. [CrossRef] [PubMed]

- Zwerver, A.M.J.; Krähenmann, T.; Watson, T.F.; Lampert, L.; George, H.C.; Pillarisetty, R.; Bojarski, S.A.; Amin, P.; Amitonov, S.V.; Boter, J.M.; et al. Qubits made by advanced semiconductor manufacturing. *Nat. Electron.* 2022, *5*, 184–190. [CrossRef]

- Dzurak, A.S. Spin-based quantum computing in silicon CMOS-compatible platforms. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 13.2.1–13.2.2.

- 4. Moore, G. The future of integrated electronics. In *Understanding Moore's Law: Four Decades of Innovation;* Fairchild Semiconductor: San Jose, CA, USA, 1964; pp. 37–55.

- 5. Colinge, J.P. Multiple-gate soi mosfets. *Solid-State Electron.* 2004, 48, 897–905. [CrossRef]

- Wu, C.C.; Lin, D.W.; Keshavarzi, A.; Huang, C.H.; Chan, C.T.; Tseng, C.H.; Chen, C.L.; Hsieh, C.Y.; Wong, K.Y.; Cheng, M.L.; et al. High performance 22/20 nm FinFET CMOS devices with advanced high-K/metal gate scheme. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 27.1.1–27.1.4.

- 7. Auth, C. 45nm high-k + metal gate strain-enhanced CMOS transistors. In Proceedings of the 2008 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 21–24 September 2008; pp. 379–386.

- 8. Yang, J.; Huang, Z.; Wang, D.; Liu, T.; Sun, X.; Qian, L.; Pan, Z.; Xu, S.; Wang, C.; Wu, C.; et al. A Novel Scheme for Full Bottom Dielectric Isolation in Stacked Si Nanosheet Gate-All-Around Transistors. *Micromachines* **2023**, *14*, 1107. [CrossRef] [PubMed]

- Lim, J.; Han, D.; Seon, S.; Baac, H.W.; Shin, C. Design for Variability: Counter-Doped Source/Drain Epitaxy Pockets in Gate-All-Around FET. *IEEE Trans. Electron Devices* 2023, 71, 400–405. [CrossRef]

- 10. Qingzhu, Z.; Yongkui, Z.; Yanna, L.; Yin, H. New structure transistors for advanced technology node CMOS ICs. *Natl. Sci. Rev.* **2024**, *11*, nwae008.

- 11. Gueorguiev, G.K.; Stafström, S.; Hultman, L. Nano-wire formation by self-assembly of silicon–metal cage-like molecules. *Chem. Phys. Lett.* **2008**, *458*, 170–174. [CrossRef]

- 12. Dos Santos, R.B.; Mota, F.B.; Rivelino, R.; Gueorguiev, G.K. Electric-field control of spin-polarization and semiconductor-to-metal transition in carbon-atom-chain devices. *J. Phys. Chem. C* 2017, 121, 26125–26132. [CrossRef]

- Parihar, S.S.; van Santen, V.M.; Thomann, S.; Pahwa, G.; Chauhan, Y.S.; Amrouch, H. Cryogenic CMOS for quantum processing: 5-nm FinFET-based SRAM arrays at 10 K. *IEEE Trans. Circuits Syst. I Regul. Pap.* 2023, 70, 3089–3102. [CrossRef]

- Genssler, P.R.; Klemme, F.; Parihar, S.S.; Brandhofer, S.; Pahwa, G.; Polian, I.; Chauhan, Y.S.; Amrouch, H. Cryogenic Embedded System to Support Quantum Computing: From 5-nm FinFET to Full Processor. *IEEE Trans. Quantum Eng.* 2023, 4, 5500611. [CrossRef]

- 15. Han, Y.; Sun, J.; Bae, J.H.; Grützmacher, D.; Knoch, J.; Zhao, Q.-T. High Performance 5 nm Si Nanowire FETs with a Record Small SS = 2.3 mV/dec and High Transconductance at 5.5 K Enabled by Dopant Segregated Silicide Source/Drain. In Proceedings of the 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Kyoto, Japan, 11–16 June 2023; pp. 1–2.

- 16. Kiran Kumar, P.; Balaji, B.; Suman, M.; Sundar, P.S.; Padmaja, E.; Sravani, K.G. A detailed roadmap from conventional-MOSFET to nanowire-MOSFET. In *Machine Learning for VLSI Chip Design*; Wiley: Hoboken, NJ, USA, 2023; pp. 65–93.

- 17. Rohrbacher, C.; Rivard, J.; Ritzenthaler, R.; Bureau, B.; Lupien, C.; Mertens, H.; Horiguchi, N.; Dupont-Ferrier, E. Dual Operation of Gate-All-Around Silicon Nanowires at Cryogenic Temperatures: FET and Quantum Dot. *arXiv* 2023, arXiv:2312.00903.

- 18. Pott, V.; Moselund, K.E.; Bouvet, D.; De Michielis, L.; Ionescu, A. Fabrication and characterization of gate-all-around silicon nanowires on bulk silicon. *IEEE Trans. Nanotechnol.* **2008**, *7*, 733–744. [CrossRef]

- Han, Y.; Sun, J.; Richstein, B.; Allibert, F.; Radu, I.; Bae, J.-H.; Grutzmacher, D.; Knoch, J.; Zhao, Q.-T. Steep switching Si nanowire p-FETs with dopant segregated silicide source/drain at cryogenic temperature. *IEEE Electron Device Lett.* 2022, 43, 1187–1190. [CrossRef]

- 20. Zhang, Q.; Yin, H.; Meng, L.; Yao, J.; Li, J.; Wang, G.; Li, Y.; Wu, Z.; Xiong, W.; Yang, H.; et al. Novel GAA Si nanowire p-MOSFETs with excellent short-channel effect immunity via an advanced forming process. *IEEE Electron Device Lett.* **2018**, *39*, 464–467. [CrossRef]

- Cao, L.; Zhang, Q.; Luo, Y.; Gu, J.; Gan, W.; Lu, P.; Yao, J.; Xu, H.; Zhao, P.; Luo, K.; et al. Novel channel-first fishbone FETs with symmetrical threshold voltages and balanced driving currents using single work function metal process. *IEEE Trans. Electron Devices* 2022, 69, 5971–5977. [CrossRef]

- Han, H.C.; Jazaeri, F.; D'Amico, A.; Baschirotto, A.; Charbon, E.; Enz, C. Cryogenic characterization of 16 nm FinFET technology for quantum computing. In Proceedings of the ESSCIRC 2021-IEEE 47th European Solid State Circuits Conference (ESSCIRC), Grenoble, France, 13–22 September 2021; pp. 71–74.

- 23. Gu, J.; Zhang, Q.; Wu, Z.; Yao, J.; Zhang, Z.; Zhu, X.; Wang, G.; Li, J.; Zhang, Y.; Cai, Y.; et al. Cryogenic transport characteristics of P-type gate-all-around silicon nanowire MOSFETs. *Nanomaterials* **2021**, *11*, 309. [CrossRef] [PubMed]

- 24. Cheng, H.; Liu, T.; Zhang, C.; Liu, Z.; Yang, Z.; Nakazato, K.; Zhang, Z. Nanowire gate-all-around MOSFETs modeling: Ballistic transport incorporating the source-to-drain tunneling. *Jpn. J. Appl. Phys.* **2020**, *59*, 074002. [CrossRef]

- 25. Cheng, H.; Uno, S.; Nakazato, K. Analytic compact model of ballistic and quasi-ballistic transport for cylindrical gate-all-around MOSFET including drain-induced barrier lowering effect. *J. Comput. Electron.* **2015**, *14*, 321–328. [CrossRef]

- 26. Datta, S. Quantum Transport: Atom to Transistor; Cambridge University Press: Cambridge, UK, 2005.

- 27. Nakashima, H.; Uozumi, K. Zero-bias current in a single-electron transistor with identical trapezoidal tunnelling barriers for finite fixed gate voltages. *J. Phys. Condens. Matter* **1998**, *10*, 4291–4296. [CrossRef]

- 28. Ma, R.L.; Li, A.R.; Wang, C.; Kong, Z.-Z.; Liao, W.-Z.; Ni, M.; Zhu, S.-K.; Chu, N.; Zhang, C.; Liu, D.; et al. Single-spin-qubit geometric gate in a silicon quantum dot. *Phys. Rev. Appl.* **2024**, *21*, 014044. [CrossRef]

- 29. Zhu, X.; Gu, J.; Yin, H.; Wu, Z. Simulation of silicon quantum dots with diamond-channel by simplified ME model. *Results Phys.* **2022**, *38*, 105575. [CrossRef]

- 30. Merino, Z.D.; Khromets, B.; Baugh, J. Simulated Charge Stability in a MOSFET Linear Quantum Dot Array. *arXiv* 2024, arXiv:2402.15499.

- Chen, J.; Schmitz, A.; Kilin, D.S. Computational simulation of the p-n doped silicon quantum dot. *Int. J. Quantum Chem.* 2012, 112, 3879–3888. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.