Liuni Yang<sup>1</sup>, Qiang Liu<sup>1,\*</sup>, Haoyuan Liang<sup>1</sup>, Minming Geng<sup>1</sup>, Kejin Wei<sup>2</sup> and Zhenrong Zhang<sup>1</sup>

- <sup>1</sup> Guangxi Key Laboratory of Multimedia Communications and Network Technology, School of Computer, Electronics and Information, Guangxi University, Nanning 530004, China

- <sup>2</sup> Guangxi Key Laboratory for Relativistic Astrophysics, School of Physical Science and Technology, Guangxi University, Nanning 530004, China

- \* Correspondence: q.liu@gxu.edu.cn

Abstract: Optical logic devices are essential functional devices for achieving optical signal processing. In this study, we design an ultra-compact  $(4.92 \times 2.52 \ \mu\text{m}^2)$  reconfigurable optical logic gate by using inverse design method with DBS algorithm based on Sb<sub>2</sub>Se<sub>3</sub>-SOI integrated platform. By selecting different amorphous/crystalline distributions of Sb<sub>2</sub>Se<sub>3</sub> via programmable electrical triggers, the designed structure can switch between OR, XOR, NOT or AND logic gate. This structure works well for all four logic functions in the wavelength range of 1540–1560 nm. Especially at the wavelength of 1550 nm, the Contrast Ratios for XOR, NOT and AND logic gate are 13.77 dB, 11.69 dB and 3.01 dB, respectively, indicating good logical judgment ability of the device. Our design is robust to a certain range of fabrication imperfections. Even if performance weakens due to deviations, improvements can be obtained by rearranging the configurations of Sb<sub>2</sub>Se<sub>3</sub> without reproducing the whole device.

**Keywords:** inverse design; Sb<sub>2</sub>Se<sub>3</sub>; direct binary search algorithm; reconfigurable optical logic gate; integrated optics

Citation: Yang, L.; Liu, Q.; Liang, H.; Geng, M.; Wei, K.; Zhang, Z. Design of Ultra-Compact and Multifunctional Optical Logic Gate Based on Sb<sub>2</sub>Se<sub>3</sub>-SOI Hybrid Platform. *Nanomaterials* **2024**, *14*, 1317. https://doi.org/10.3390/ nano14151317

Academic Editor: Miguel A. Correa-Duarte

Received: 24 June 2024 Revised: 25 July 2024 Accepted: 30 July 2024 Published: 5 August 2024

**Copyright:** © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

## 1. Introduction

Optical logic gates are among the most important basic units in optical signal processing, as well as in optical communication networks. A series of logic gates based on various schemes, such as photonic crystals [1–6], plasmonic waveguides [7], and semiconductor optical amplifier [8–11], have been proposed and proven. However, logic gates based on these schemes are large, function unitary and non-adjustable.

Integrated optical devices or systems are a hot research topic and the inverse design method has been extensively applied in the researches of nanophotonic devices recently. Many integrated optical devices, such as polarization beam splitter [12], waveguide bends [13,14], reflector [15], optical power splitters [16–20] and logic gates [21,22], were designed by using inverse design method and then prepared. Compared with devices constructed using traditional methods, structures invented using inverse design have higher degree of freedom and more compact layouts. For instance, Q. Lu et al. [21] used inverse design method to compose a NOT gate and an AND gate, the individual size of both is only  $1.2 \times 1.2 \ \mu\text{m}^2$ . H. Qi et al. [22] designed an integrated photonic circuit with two all-optical switches controlling the input states of an all-optical XOR logic gate by using inverse design method and fabricated it out, the size of the whole circuit is  $2.5 \times 7 \ \mu m^2$ . The fundamental of inverse design is to determine the target performance of the device, then adopt diverse optimization algorithms to calculate and design the required configuration by using computer without manual participation [23]. By using this method, high performance devices can be easily developed under certain constraints (e.g., specified footprints or structures) without manually tedious parameter adjustment works, saving massive resources. Inverse design method can be based on genetic algorithm [15], direct binary search (DBS) algorithm [12,16,17,19,20,24], or deep learning algorithm [25], etc. Among

them, the DBS algorithm has received increasing attention due to its fast convergence speed and operation convenience. The optical devices mentioned in this paragraph have high integration, but their functions cannot be adjusted. In order to develop reconfigurable devices, phase change materials have been introduced into the device construction process using inverse design method.

Phase change materials have attracted widespread attention due to their multiple states, which enable the reconfiguration of optical devices. Usually, the phase change materials can be switched between two states: crystalline or amorphous. The conversion between these two states can be activated by external thermal, optical and electrical triggers. This conversion is reversible but non-volatile, once the state switches, there is no need to maintain continuous external triggering. The difference in refractive index between the amorphous and crystalline states of materials is significant, so that different functions can be achieved on the same device. So far, phase change materials have been used in creations of tunable optical devices like switches [26–29], power splitters [30,31], logic gates [32,33] and mode converters [34], etc. Especially, the complex refractive index at 1550 nm of phase change material  $Sb_2Se_3$  is 3.285 + 0.000i for amorphous state and 4.050 + 0.000i for crystalline [35], the corresponding extinction coefficient is 0 for both states. This means that Sb<sub>2</sub>Se<sub>3</sub> barely owns optical absorption at 1550 nm, indicating extremely low loss compared to the common phase-change materials Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) [26,29] and Ge<sub>2</sub>Sb<sub>2</sub>Se<sub>4</sub>Te<sub>1</sub> (GSST) [30]. There are a few photonic logic gates designed by using inverse design with DBS algorithm based on material  $Sb_2Se_3$ . For example, Z. Peng et al. [32] simulated a  $2 \times 2 \,\mu\text{m}^2$  optical logic gate, which could be used as an AND gate or a XOR gate when its  $Sb_2Se_3$  part was switched between amorphous or crystalline. Y. Zhang et al. [33] designed two logic gates, one of which exhibited the function of OR gate and NOT gate, and the other implemented XOR gate and AND gate when the state of Sb<sub>2</sub>Se<sub>3</sub> was changed. Sb<sub>2</sub>Se<sub>3</sub> can be prepared using various methods such as pulse laser deposition [36–38], magnetron sputtering [39,40], and thermal evaporation [39,41,42]. In addition, the refractive index of Sb<sub>2</sub>Se<sub>3</sub> in amorphous state is similar to that of silicon, which can be well integrated into standard silicon-on-insulator (SOI) integrated photonic platforms. Therefore, it can be considered to incorporate Sb<sub>2</sub>Se<sub>3</sub> into the SOI platform to form hybrid structures for reconfigurable optical logic gates.

In this paper, we demonstrate an ultra-compact (4.92  $\mu$ m  $\times$  2.52  $\mu$ m for the optimal region) and multifunctional optical logic gate based on Sb<sub>2</sub>Se<sub>3</sub>-SOI hybrid platform by using inverse design method with DBS algorithm. Once the structure is prepared, by selecting appropriate amorphous and crystalline distribution of Sb<sub>2</sub>Se<sub>3</sub> via external electrical triggers that are supplied by an application specific integrated circuit (ASIC) [30,43], the designed structure can switch between four types of logic gates that act as an OR gate, a XOR gate, a NOT gate or an AND gate. Unlike the optical logic gate design based on  $Sb_2Se_3$ material introduced above, in our design, each Sb<sub>2</sub>Se<sub>3</sub> rectangular deposited in the silicon layer is relatively independent and the corresponding amorphous/crystalline states can be controlled individually. This provides the possibility of achieving more device functions on the same structure. We also analyze the device robustness against manufacturing imperfections. The simulation results show that the device can still commendably perform the expected logic function within a certain fabrication deviation range. If the performance weakens due to manufacturing imperfections while the designed structure works as a logic XOR gate, a NOT gate, or an AND gate, improvement can be obtained by simply recalculating the distribution of Sb<sub>2</sub>Se<sub>3</sub> amorphous/crystalline states. In other words, improvement can be easily achieved by changing the states of Sb<sub>2</sub>Se<sub>3</sub> via external triggers without reproducing the whole device.

### 2. Inverse Design of the Multifunctional Optical Logic Gate

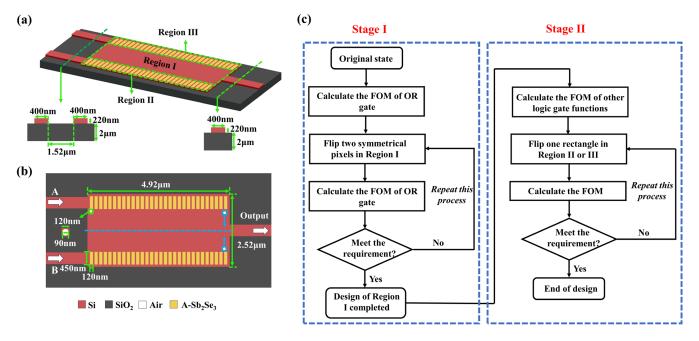

Our integrated optical logic gate was constructed by using the inverse design method with DBS algorithm and air cylindrical lattice structure. As shown in Figure 1a,b, the material for design was set as a 220 nm processable silicon (marked in red) layer on a 2  $\mu$ m

silica substrate (marked in grey). The  $4.92 \times 2.52 \ \mu\text{m}^2$  design area was divided into three regions. The Region I was divided into 480 (40 × 12) square pixels with an individual size of 120 × 120 nm<sup>2</sup>. Each pixel was assigned one of the following two states according to calculation: unetched and etched, which was equivalent to fill the corresponding pixel center with an air cylinder (marked in white) with a radius of 45 nm and a thickness of 220 nm. Region II and Region III each contained a column of Sb<sub>2</sub>Se<sub>3</sub> rectangles (marked in yellow) with 40 nm silicon gaps between them. The size of each rectangle was  $450 \times 120 \text{ nm}^2$  and its thickness was 220 nm. Rather than placing Sb<sub>2</sub>Se<sub>3</sub> thin film on the surface, we embedded the Sb<sub>2</sub>Se<sub>3</sub> rectangles into the silicon layer to pursue stronger light field control ability [26,29–34]. According to Ref. [16], we added a 60 nm protection layer around each region to avoid edge being etched through. The width of input/output waveguides was set as 400 nm [29,32,33] and the gap between two input ports was set as 1.52 µm. All simulations in this research were carried out used commercial software Ansys Lumerical FDTD 2020 R2.4. The wavelength of laser input was set as 1550 nm and the launched mode was set as TE<sub>0</sub> mode initially.

**Figure 1.** The basic structure and design process of the optical logic gate; (a,b) initial design layout and parameters, A-Sb<sub>2</sub>Se<sub>3</sub> stands for amorphous Sb<sub>2</sub>Se<sub>3</sub>, the white arrow in (b) represents the direction of light transmission, the blue arrow represents selecting two symmetrical pixels simultaneously by column and the selecting direction order when designing Region I; (c) DBS algorithm optimization process of our designed logic gate.

The DBS algorithm inverse design process for our designed logic gate is shown in Figure 1c. A critical step of inverse design was to set a figure-of-merit (*FOM*), which represented the approaching degree of the current configuration's performance to the target function when the states of pixels in Region I and Sb<sub>2</sub>Se<sub>3</sub> rectangles in Region II or III were changed. The *FOM* should approach a certain convergence value as the number of iterations increased to ensure the correctness of the device optimization. The entire optimization process is divided into two steps. In the Stage I, Region I is optimized separately to complete the logic OR gate design. In the Stage II, Region II and III are treated as a whole to complete the logic XOR gate, logic NOT gate and logic AND gate design, respectively. The original state of pixels in Region I was set as "unetched" and that for rectangles in Region II and III was set as "amorphous". During the simulation, the state of each pixel was flipped to "etched" sequentially and the corresponding *FOM* was calculated at the same time. If the *FOM* was improved, the state of the calculating pixel would be retained,

otherwise would return back to "unetched". One iteration was completed when all pixels were traversed and the next round would start with the current device structure as the new initial structure. The iterative process would stop when the *FOM* no longer grew with the number of iterations, i.e., the *FOM* converged. A similar process was carried out on Region II then Region III to determine the crystalline/amorphous state of each Sb<sub>2</sub>Se<sub>3</sub> rectangle. It is worth noting that when calculating the state of pixels in Region I, instead of selecting one pixel at a time, selecting two symmetrical pixels simultaneously for simulation obtained better performance devices and double computational efficiency. For XOR gate, NOT gate and AND gate, in order to obtain more possibilities during the simulation process, only one rectangle in Region II or III is flipped at a time. By changing the distribution of etched air holes and crystalline/amorphous Sb<sub>2</sub>Se<sub>3</sub> rectangle, the effective refractive index of the device can be adjusted, thereby regulating the output of optical signals to achieve different logic gate functions. Our simulation results can be reproduced using the same parameters and following the same steps. The figures shown in this paper are optimal results obtained after multiple calculations, thus eliminating the influence of stochastic uncertainties.

Normally, '0' is used to indicate no signal while '1' means a signal input. As a logic gate, there are four types of input pair via Port A and Port B of our design, namely '00', '01', '10' and '11'. Since we expect our design owns the function of an OR gate, a XOR gate, a NOT gate and an AND gate, and the output of any aforementioned logic gate is always '0' when the input is '00'. Hence the '00' input situation is not considered in subsequent simulations.

We first calculated the configuration (Region I only) of an OR gate according to the following *FOM*:

$$FOM_{OR} = T_{01} + T_{10} + T_{11} \tag{1}$$

where  $T_{01}$ ,  $T_{10}$  and  $T_{11}$  represent the light transmittance detected at the output port when the input is '01', '10', or '11', respectively. Based on the simulated configuration of OR gate, we further calculated the state of Sb<sub>2</sub>Se<sub>3</sub> rectangles in Region II and III according to following *FOM* formulas to achieve the function of XOR gate, NOT gate or AND gate:

$$FOM_{XOR} = 1 + T_{01} + T_{10} - T_{11} - |T_{01} - T_{10}|$$

<sup>(2)</sup>

$$FOM_{NOT} = 1 + T_{01} - T_{11} \tag{3}$$

$$FOM_{AND} = 1 - |T_{11} - 0.7| - |T_{01} - 0.35| - |T_{10} - 0.35|$$

(4)

When the output should be judged as logic '1', we expect a high transmittance and set it to a positive value, otherwise a negative value is set. The item  $|T_{01} - T_{10}|$  is used to balance the error of the outputs when inputting '01' and '10' for the XOR gate. When simulating the AND gate, we set the judging threshold as 0.5, the target value as 0.7 for  $T_{11}$  and 0.35 for  $T_{01}$  and  $T_{10}$ . Because the output corresponding to '11' input should equal to the sum of transmittances corresponding to '01' or '10' input due to the symmetrical structure of Region I.

Contrast Ratio (*CR*) [44] is a criterion to evaluate the difference between logic '1', and logic '0'. It is defined as:

$$CR = 10lg(T_1/T_0) \tag{5}$$

where  $T_1$  stands for the minimum optical transmittance of device for logic '1', and  $T_0$  means the maximum transmittance for logic '0' [1]. The higher the *CR* value, the stronger the device's ability to distinguish between logic '1' and logic '0'.

#### 3. Simulation Results

As described above, we designed an optical logic gate based on the Sb<sub>2</sub>Se<sub>3</sub>-SOI hybrid platform using the inverse design method with the DBS algorithm. The layout of Region I (SOI) in our design is fixed. By changing the state of Sb<sub>2</sub>Se<sub>3</sub> (Region II and III) to crystalline or amorphous, functions of OR gate, XOR gate, NOT gate and AND gate can be obtained. The function details of the logic gate we designed are as follows.

## 3.1. OR Logic Gate

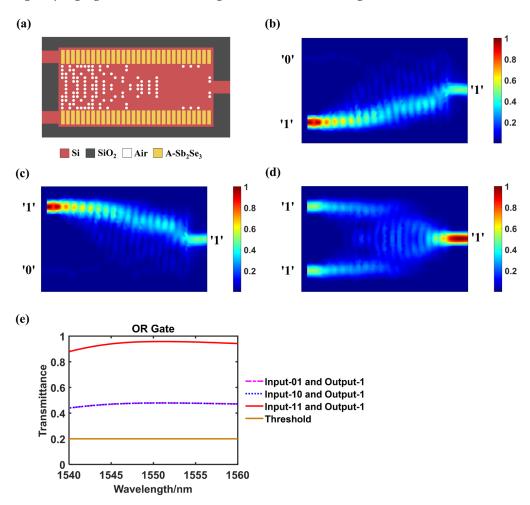

Figure 2a–d present the optimized layout and the simulated light field distribution when our designed structure act as an OR logic gate. As shown in Figure 2b–d, as long as there is input from either Port A or Port B, or both, there is an output that is higher than the logical judging threshold, achieving the function of an OR gate.

**Figure 2.** OR logic gate. (a) The configuration of the designed structure when act as an OR gate, A-Sb<sub>2</sub>Se<sub>3</sub> stands for amorphous Sb<sub>2</sub>Se<sub>3</sub>; (b–d) the simulated light field intensity distributions when inputting '01', '10' or '11' separately; (e) Transmittance variation curves of different output logic states within the wavelength range of 1540–1560 nm.

Figure 2e shows the transmittance changes of different output logic states in the wavelength range of 1540–1560 nm. Table 1 displays the normalized optical transmittances at 1550 nm wavelength and the binary output truth table when the device works as a logical OR gate. We set the logic judging threshold as 0.2. Transmittance larger than this value will be expressed as logic '1', otherwise it will be expressed as logic '0'. The device can effectively distinguish between logic '1' and '0' based on the design threshold within the wavelength range of 1540–1560 nm. At 1550 nm wavelength, when the input is '00' and there is no output, it is judged as logic '0'. When the input pairs are '01', '10' and '11', the corresponding transmittances are 0.478, 0.478 and 0.957, respectively, which are all larger than the threshold then can be determined as logic '1'. Logic '1' and '0' can be clearly distinguished that the functionality of the logical OR gate is realized.

| Input A | Input B | Threshold | Optical Transmittance | Binary Output |

|---------|---------|-----------|-----------------------|---------------|

| 0       | 0       | 0.2       | 0                     | 0             |

| 0       | 1       | 0.2       | 0.478                 | 1             |

| 1       | 0       | 0.2       | 0.478                 | 1             |

| 1       | 1       | 0.2       | 0.957                 | 1             |

**Table 1.** The normalized input, transmittance and the truth table for OR logic gate.

# 3.2. XOR Logic Gate

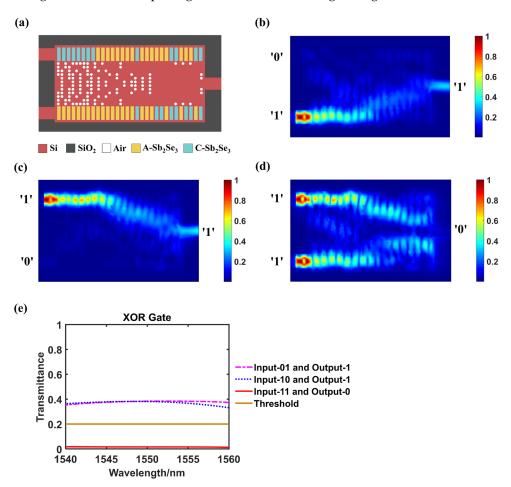

When the truth values at the input ends are different, the XOR gate should output logic '1', otherwise it should output logic '0'. Figure 3a–d show the optimized configuration and the simulated light field distributions of XOR logic gate. Figure 3e shows the transmittance changes of different output logic states in the wavelength range of 1540–1560 nm.

**Figure 3.** XOR logic gate. (a) The configuration of designed structure when act as a XOR gate, A-Sb<sub>2</sub>Se<sub>3</sub> stands for amorphous Sb<sub>2</sub>Se<sub>3</sub> and C-Sb<sub>2</sub>Se<sub>3</sub> stands for crystalline Sb<sub>2</sub>Se<sub>3</sub>; (**b**–**d**) The simulated light field intensity distributions when inputting '01', '10' or '11' separately; (**e**) Transmittance variation curves of different output logic states within the wavelength range of 1540–1560 nm.

Accordingly, Table 2 lists the key data and truth table of XOR gate. The judging threshold is also set as 0.2. As shown in Figure 3b–e and Table 2, When the input pair are '01' or '10', the outputs are 0.383 and 0.382, which are higher than the threshold that could be determined as logic '1'. When the input is '11', the transmittance is 0.016, which is too weak that can be judged as logic '0'. The judgement is valid in a wavelength range of 1540–1560 nm. The CR of photonic XOR logic gate is 13.77 dB, indicating a strong discriminative ability of this design.

| Input A | Input B | Threshold | Optical Transmittance | Binary Output |

|---------|---------|-----------|-----------------------|---------------|

| 0       | 0       | 0.2       | 0                     | 0             |

| 0       | 1       | 0.2       | 0.383                 | 1             |

| 1       | 0       | 0.2       | 0.382                 | 1             |

| 1       | 1       | 0.2       | 0.016                 | 0             |

Table 2. The normalized input, transmittance and the truth table for XOR logic gate.

### 3.3. NOT Logic Gate

Figure 4a–c present the optimized configuration and the simulated light field distributions of the NOT logic gate. We set Port B as a control waveguide with a constant light, so that there is still an output can be detected as logic '1' when no input (logic '0') from Port A (Figure 4b). While Port A has a signal input (logic '1'), there is almost no output that can be detected which is judged as logic '0' (Figure 4c). The NOT gate determination function is valid in the wavelength range of 1540–1560 nm (Figure 4d).

**Figure 4.** NOT logic gate. (a) The configuration of designed structure when act as a NOT gate, A-Sb<sub>2</sub>Se<sub>3</sub> stands for amorphous Sb<sub>2</sub>Se<sub>3</sub> and C-Sb<sub>2</sub>Se<sub>3</sub> stands for crystalline Sb<sub>2</sub>Se<sub>3</sub>; (b,c) The simulated light field intensity distributions when inputting '0' or '1' at Port A, respectively, Port B is used for control; (d) Transmittance variation curves of different output logic states within the wavelength range of 1540–1560 nm.

The exact data of the NOT gate operating at 1550 nm wavelength are listed in Table 3. The judging threshold is also set as 0.2. When the input at Port A is '0', the transmittance is 0.547, which is greater than the threshold that can be determined as logic '1'. While the input at port A is '1', the transmittance is only 0.037 then is judged as logic '0'. The CR of logic NOT gate is 11.69 dB.

Table 3. The normalized input, transmittance and the truth table for NOT logic gate.

| Input A | Input B for Control | Threshold | Optical Transmittance | <b>Binary Output</b> |

|---------|---------------------|-----------|-----------------------|----------------------|

| 0       | 1                   | 0.2       | 0.547                 | 1                    |

| 1       | 1                   | 0.2       | 0.037                 | 0                    |

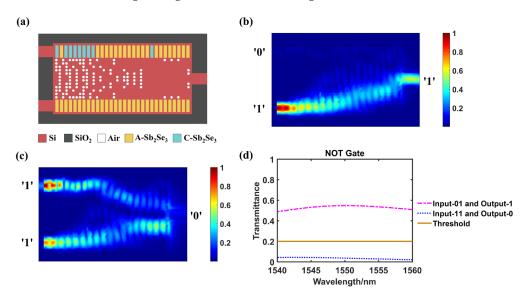

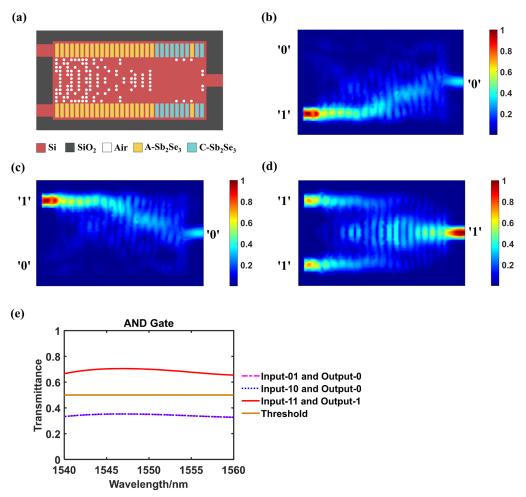

#### 3.4. AND Logic Gate

Figure 5a–d show the layout as well as the light field intensity distribution at 1550 nm wavelength of AND logic gate, and Table 4 displays its detail data. The transmittance changes of different output logic states in the wavelength range of 1540–1560 nm is shown

in Figure 5e. Slightly different from other logic gate functions, the judging threshold for AND gate is set as 0.5. Hence when inputting '01' or '10', the transmittances are 0.350 and 0.349, respectively, which are determined as logical '0' since they are below the threshold. While the input is '11', the transmittance is 0.700, which is larger than the threshold that is judged as logic '1'. The function of logical AND gate is implemented. The CR of AND gate is 3.01 dB.

**Figure 5.** AND logic gate. (a) The configuration of designed structure when act as an AND gate, A-Sb<sub>2</sub>Se<sub>3</sub> stands for amorphous Sb<sub>2</sub>Se<sub>3</sub> and C-Sb<sub>2</sub>Se<sub>3</sub> stands for crystalline Sb<sub>2</sub>Se<sub>3</sub>; (**b**–**d**) The simulated light field intensity distributions when inputting '01', '10' or '11' separately; (e) Transmittance variation curves of different output logic states within the wavelength range of 1540–1560 nm.

Table 4. The normalized input, transmittance and the truth table for AND logic gate.

| Input A | Input B | Threshold | Optical Transmittance | <b>Binary Output</b> |

|---------|---------|-----------|-----------------------|----------------------|

| 0       | 0       | 0.5       | 0                     | 0                    |

| 0       | 1       | 0.5       | 0.350                 | 0                    |

| 1       | 0       | 0.5       | 0.349                 | 0                    |

| 1       | 1       | 0.5       | 0.700                 | 1                    |

In practice, when the input pair for logic gate is '11', there may be inconsistencies in the amplitude or phase of the light launched at the two input ports. Therefore, we studied the impacts on outputs of different logic functions of our design when there is a  $\pm 5\%$  deviation in the amplitude of two inputs. Outcomes caused by phase differences ranging from 0 to  $\pi$  between two inputs were also investigated. The simulation results showed that the impact of inconsistent amplitude or phase input on device performance is minimal.

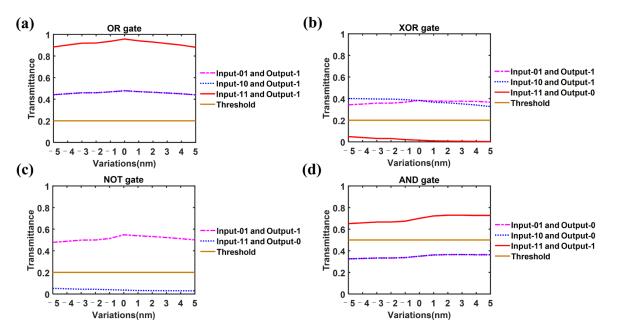

### 3.5. Manufacturing Tolerance Analysis

Because of the unavoidable fabrication imperfections in practice, it is essential to discuss the effect of fabrication tolerance on the designed logic gate. We simulated the performance changes of the device under different bias conditions and display them in Figure 6. The error range for the diameter of the holes in Region I as well as the length and width of the rectangles in Region II or III is set to  $\pm 5$  nm [45] (abscissa). As shown in Figure 6, the changes in transmittances of logic gate are not significant and all within the range that can be correctly determined. This suggests that even if there are offsets within the set range due to fabrication imperfections in practice, the designed logic gate can still complete the expected functions. It is worth noting that, in addition to simulating the case where the device manufacturing tolerance is a fixed value as described above, we also simulated the case where the manufacturing tolerance randomly varies obeyed a uniform statistical distribution within a  $\pm 5$  nm range. Compared to devices with fixed  $\pm 5$  nm manufacturing errors, devices with randomly distributed manufacturing tolerances have better performance, which proves strong device robustness.

**Figure 6.** Simulated light transmittance at the output port under certain fabrication deviations. The error range for the diameter of the holes in Region I as well as the length and width of the rectangles in Region II or III is  $\pm 5$  nm (abscissa). (a) output transmittance of logic OR gate; (b) output transmittance of logic XOR gate; (c) output transmittance of logic NOT gate; (d) output transmittance of logic AND gate.

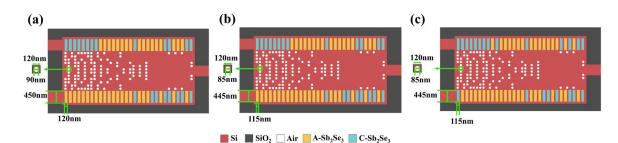

We found that there is a relatively obvious change in the transmittance under some bias conditions. When the device operates as a logic XOR gate and the diameter of the holes in Region I as well as the length and width of the rectangles in Region II or III (Figure 6b) gradually decreases, the transmittance corresponding to '11' input and logic '0' output increases that may lead to a decrease in CR, i.e., a weakening in device's performance. If such a situation occurs in actual preparation, in order to improve device performance, we can recalculate the state of Sb<sub>2</sub>Se<sub>3</sub> rectangles (Regions II and III) using the actual fabrication parameters based on the current designed structure (Figure 7). New optimal distribution of the amorphous/crystalline states of Sb<sub>2</sub>Se<sub>3</sub> rectangles can then be easily implemented using ASIC controlled by computer programming. On the other hand, the pattern of Region I, which needs to go through complex processes like laser engraving and etching during fabrication, requires no changes. As shown in Table 5, the CR of improved configuration is 11.26 dB.

**Figure 7.** (a) The configuration of XOR gate designed with set ideal parameters; (b) the configuration of XOR gate with parameter bias; (c) the configuration of XOR gate recalculated with deviations. The states of Sb<sub>2</sub>Se<sub>3</sub> rectangles in Region II and III are changed. A-Sb<sub>2</sub>Se<sub>3</sub> stands for amorphous Sb<sub>2</sub>Se<sub>3</sub> and C-Sb<sub>2</sub>Se<sub>3</sub> stands for crystalline Sb<sub>2</sub>Se<sub>3</sub>.

Table 5. Comparison of CR for XOR gate calculated with parameter deviations before or after optimization.

| Designed Structures | XOR Gate Designed   | XOR Gate with  | Optimized XOR       |

|---------------------|---------------------|----------------|---------------------|

|                     | with Set Parameters | Parameter Bias | Gate with Parameter |

|                     | (Figure 7a)         | (Figure 7b)    | Bias (Figure 7c)    |

| Contrast Ratio (CR) | 13.77 dB            | 8.43 dB        | 11.26 dB            |

Overall, the simulation results reveal that under certain fabrication imperfections, the device has good robustness and can still achieve the predetermined functions. Even if the device's performance is weakened due to fabrication deviation, improvement can still be achieved by simply rearranging the state of phase change materials Sb<sub>2</sub>Se<sub>3</sub>, which is trigger by computer programming ASIC, without reprocess the entire device.

# 4. Conclusions

In this research, we design an ultra-compact, reconfigurable multifunctional optical logic gate by using inverse design method with DBS algorithm based on Sb<sub>2</sub>Se<sub>3</sub>-SOI integrated platform. The device's footprint is only  $4.92 \times 2.52 \ \mu\text{m}^2$ . By arranging different crystalline/amorphous distributions of Sb<sub>2</sub>Se<sub>3</sub> rectangles via electrical heating provided by programmable ASIC, functions of OR, XOR, NOT and AND logic gate can be realized. The device works well in all four logic functions within the wavelength range of 1540–1560 nm. The CRs for XOR, NOT and AND logic gate function at 1550 nm wavelength are 13.77 dB, 11.69 dB and 3.01 dB, respectively, indicating good logical judgment ability. We also analyze the device robustness against fabrication imperfections. The preparation deviation range is specified as:  $\pm 5$  nm for the diameter of etched holes in Region I and the side length of rectangles in Region II or III of Sb<sub>2</sub>Se<sub>3</sub>. Under this circumstance, our design still maintains excellent performance, indicating a good manufacturing tolerance. Moreover, if the device's performance is weakened due to fabrication imperfections, improvements can be obtained by simply rearranging the distribution of Sb<sub>2</sub>Se<sub>3</sub> amorphous/crystalline states according to actual parameters. In summary, changes in functionality and improvements in performance can be easily achieved by changing the states of Sb<sub>2</sub>Se<sub>3</sub> via external triggers without reproducing the whole device.

**Author Contributions:** Conceptualization, L.Y. and H.L.; methodology, L.Y. and H.L.; software, L.Y.; resources, Q.L. and Z.Z.; writing—original draft preparation, L.Y. and Q.L.; supervision, Q.L., M.G., K.W. and Z.Z.; funding acquisition, Q.L., K.W. and Z.Z. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded by the National Natural Science Foundation of China (62365001, 61965003); Guangxi Key Research and Development Program (2021GXNSFDA076001).

Data Availability Statement: Data available in a publicly accessible repository.

Conflicts of Interest: The authors declare no conflicts of interest.

### References

- 1. Parandin, F.; Malmir, M.R.; Naseri, M.; Zahedi, A. Reconfigurable all-optical NOT, XOR, and NOR logic gates based on two dimensional photonic crystals. *Superlattices Microstruct*. **2018**, *113*, 737–744. [CrossRef]

- He, L.; Zhang, W.X.; Zhang, X.D. Topological all-optical logic gates based on two-dimensional photonic crystals. *Opt. Express* 2019, 27, 25841–25860. [CrossRef] [PubMed]

- 3. Masoud, A.M.; Ahmed, I.S.; El-Naggar, S.A.; Asham, M.D. Design and simulation of all-optical logic gates based on two-dimensional photonic crystals. *J. Opt.* **2021**, *51*, 343–351. [CrossRef]

- Caballero, L.P.; Povinelli, M.L.; Ramirez, J.C.; Guimarães, P.S.S.; Vilela Neto, O.P. Photonic crystal integrated logic gates and circuits. *Opt. Express* 2022, 30, 1976–1993. [CrossRef] [PubMed]

- 5. Anagha, E.G.; Jeyachitra, R.K. Optimized design of an all-optical XOR gate with high contrast ratio and ultra-compact dimensions. *Appl. Phys. B Lasers Opt.* **2022**, *128*, 21. [CrossRef]

- Soma, S.; Gowre, S.K.C.; Sonth, M.V.; Gadgay, B.; Jyoti, B. Design and simulation of reconfigurable optical logic gates for integrated optical circuits. *Opt. Quantum Electron.* 2023, 55, 340. [CrossRef]

- Fu, Y.; Hu, X.; Lu, C.; Yue, S.; Yang, H.; Gong, Q. All-Optical Logic Gates Based on Nanoscale Plasmonic Slot Waveguides. *Nano* Lett. 2012, 12, 5784–5790. [CrossRef] [PubMed]

- 8. Gayen, D.K.; Chattopadhyay, T. Designing of Optimized All-Optical Half Adder Circuit Using Single Quantum-Dot Semiconductor Optical Amplifier Assisted Mach-Zehnder Interferometer. J. Light. Technol. 2013, 31, 2029–2035. [CrossRef]

- Singh, P.; Tripathi, D.K.; Jaiswal, S.; Dixit, H.K. Designs of all-optical buffer and OR gate using SOA-MZI. *Opt. Quantum Electron*. 2013, 46, 1435–1444. [CrossRef]

- 10. Chen, X.; Huo, L.; Zhao, Z.; Zhuang, L.; Lou, C. Study on 100-Gb/s reconfigurable all-optical logic gates using a single semiconductor optical amplifier. *Opt. Express* **2016**, *24*, 30245–30253. [CrossRef]

- 11. Komatsu, K.; Hosoya, G.; Yashima, H. All-optical logic NOR gate using a single quantum-dot SOA-assisted an optical filter. *Opt. Quantum Electron.* **2018**, *50*, 131. [CrossRef]

- Shen, B.; Wang, P.; Polson, R.; Menon, R. An integrated-nanophotonics polarization beamsplitter with 2.4 × 2.4 μm<sup>2</sup> footprint. *Nat. Photonics* 2015, 9, 378–382. [CrossRef]

- 13. Liu, Y.; Sun, W.; Xie, H.; Zhang, N.; Xu, K.; Yao, Y.; Xiao, S.; Song, Q. Very sharp adiabatic bends based on an inverse design. *Opt. Lett.* **2018**, *43*, 2482–2485. [CrossRef]

- 14. Yang, S.; Jia, H.; Niu, J.; Fu, X.; Yang, L. CMOS-compatible ultra-compact silicon multimode waveguide bend based on inverse design method. *Opt. Commun.* **2022**, *523*, 128733. [CrossRef]

- Yu, Z.; Cui, H.; Sun, X. Genetically optimized on-chip wideband ultracompact reflectors and Fabry–Perot cavities. *Photonics Res.* 2017, 5, B15–B19. [CrossRef]

- 16. Lu, L.; Liu, D.; Zhou, F.; Li, D.; Cheng, M.; Deng, L.; Fu, S.; Xia, J.; Zhang, M. Inverse-designed single-step-etched colorless 3 dB couplers based on RIE-lag-insensitive PhC-like subwavelength structures. *Opt. Lett.* **2016**, *41*, 5051–5054. [CrossRef]

- 17. Xu, Y.; Ma, H.; Xie, T.; Yang, J.; Zhang, Z. Ultra-Compact Power Splitters with Low Loss in Arbitrary Direction Based on Inverse Design Method. *Photonics* **2021**, *8*, 516. [CrossRef]

- 18. Xu, K.; Liu, L.; Wen, X.; Sun, W.; Zhang, N.; Yi, N.; Sun, S.; Xiao, S.; Song, Q. Integrated photonic power divider with arbitrary power ratios. *Opt. Lett.* **2017**, *42*, 855–858. [CrossRef]

- 19. Chen, Y.; Chen, Y.; Lu, M.; Zhao, Y.; Hu, G.; Yun, B.; Cui, Y. Optimized inverse design of an ultra-compact silicon-based 2 × 2 3 dB optical power splitter. *Opt. Commun.* **2023**, 530, 129141. [CrossRef]

- Ma, H.; Huang, J.; Zhang, K.; Yang, J. Arbitrary-direction, multichannel and ultra-compact power splitters by inverse design method. *Opt. Commun.* 2020, 462, 125329. [CrossRef]

- Lu, Q.; Yan, X.; Wei, W.; Zhang, X.; Zhang, M.; Zheng, J.; Li, B.; Luo, Y.; Lin, Q.; Ren, X. High-speed ultra-compact all-optical NOT and AND logic gates designed by a multi-objective particle swarm optimized method. *Opt. Laser Technol.* 2019, 116, 322–327. [CrossRef]

- 22. Qi, H.; Du, Z.; Hu, X.; Yang, J.; Chu, S.; Gong, Q. High performance integrated photonic circuit based on inverse design method. *Opto-Electron. Adv.* **2022**, *5*, 210061. [CrossRef]

- 23. Molesky, S.; Lin, Z.; Piggott, A.Y.; Jin, W.; Vucković, J.; Rodriguez, A.W. Inverse design in nanophotonics. *Nat. Photonics* 2018, 12, 659–670. [CrossRef]

- 24. Ma, H.; Du, T.; Zhang, Z.; Jiang, X.; Fang, L.; Yang, J. Inverse design of an air-cladding and fully-etched silicon polarization rotator based on a taper-based mode hybridization. *Opt. Commun.* **2023**, *526*, 128912. [CrossRef]

- Tahersima, M.H.; Kojima, K.; Koike-Akino, T.; Jha, D.; Wang, B.; Lin, C.; Parsons, K. Deep Neural Network Inverse Design of Integrated Photonic Power Splitters. Sci. Rep. 2019, 9, 1368. [CrossRef]

- Ma, H.; Yang, J.; Huang, J.; Zhang, Z.; Zhang, K. Inverse-designed single-mode and multi-mode nanophotonic waveguide switches based on hybrid silicon-Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> platform. *Results Phys.* 2021, 26, 104384. [CrossRef]

- 27. Song, C.; Gao, Y.; Wang, G.; Chen, Y.; Xu, P.; Gu, C.; Shi, Y.; Shen, X. Compact nonvolatile 2×2 photonic switch based on two-mode interference. *Opt. Express* **2022**, *30*, 30430–30440. [CrossRef]

- 28. Quan, Z.; Wan, Y.; Ma, X.; Wang, J. Nonvolatile multi-level adjustable optical switch based on the phase change material. *Opt. Express* **2022**, *30*, 36096–36109. [CrossRef]

- 29. Yin, K.; Gao, Y.; Shi, H.; Zhu, S. Inverse Design and Numerical Investigations of an Ultra-Compact Integrated Optical Switch Based on Phase Change Material. *Nanomaterials* **2023**, *13*, 1643. [CrossRef]

- Yuan, H.; Wu, J.; Zhang, J.; Pu, X.; Zhang, Z.; Yu, Y.; Yang, J. Non-Volatile Programmable Ultra-Small Photonic Arbitrary Power Splitters. Nanomaterials 2022, 12, 699. [CrossRef]

- Shi, W.; Li, J.; Wang, M.; Chen, L.; Liu, Y.; Ye, H. Topology design of reconfigurable power splitter with pixelated Sb-based phase change materials. *Opt. Mater.* 2023, 136, 113448. [CrossRef]

- 32. Peng, Z.; Feng, J.; Yuan, H.; Cheng, W.; Wang, Y.; Ren, X.; Cheng, H.; Zang, S.; Shuai, Y.; Liu, H.; et al. A Non-Volatile Tunable Ultra-Compact Silicon Photonic Logic Gate. *Nanomaterials* **2022**, *12*, 1121. [CrossRef]

- 33. Zhang, Y.; Peng, Z.; Wang, Z.; Wu, Y.; Hu, Y.; Wu, J.; Yang, J. Non-Volatile Reconfigurable Compact Photonic Logic Gates Based on Phase-Change Materials. *Nanomaterials* **2023**, *13*, 1375. [CrossRef] [PubMed]

- 34. Chen, H.; Jia, H.; Yang, J.; Tian, Y.; Wang, T. Ultra-compact switchable mode converter based on silicon and optical phase change material hybrid metastructure. *Opt. Commun.* **2020**, *473*, 125889. [CrossRef]

- 35. Delaney, M.; Zeimpekis, I.; Lawson, D.; Hewak, D.W.; Muskens, O.L. A New Family of Ultralow Loss Reversible Phase-Change Materials for Photonic Integrated Circuits: Sb<sub>2</sub>S<sub>3</sub> and Sb<sub>2</sub>Se<sub>3</sub>. *Adv. Funct. Mater.* **2020**, *30*, 200447–200456. [CrossRef]

- 36. Yang, K.; Li, B.; Zeng, G. Structural, morphological, compositional, optical and electrical properties of Sb<sub>2</sub>Se<sub>3</sub> thin films deposited by pulsed laser deposition. *Superlattices Microstruct.* **2020**, *145*, 106618. [CrossRef]

- Yang, K.; Li, B.; Zeng, G. Sb<sub>2</sub>Se<sub>3</sub> thin film solar cells prepared by pulsed laser deposition. J. Alloys Compd. 2020, 821, 153505. [CrossRef]

- Jain, A.K.; Gopalakrishnan, C.; Malar, P. Study of pulsed laser deposited antimony selenide thin films. J. Mater. Sci. Mater. Electron. 2022, 33, 10430–10438. [CrossRef]

- 39. Lei, K.; Wei, M.; Chen, Z.; Wu, J.; Jian, J.; Du, J.; Li, J.; Li, L.; Lin, H. Magnetron-sputtered and thermal-evaporated low-loss Sb-Se phase-change films in non-volatile integrated photonics. *Opt. Mater. Express* **2022**, *12*, 2815–2823. [CrossRef]

- 40. Turkoglu, F.; Ekren, M.E.; Cantas, A.; Yakinci, K.; Gundogan, H.; Koseoglu, H.; Aygun, G.; Ozyuzer, L. Structural and optical characteristics of antimony selenosulfide thin films prepared by two-step method. *J. Korean Phys. Soc.* 2022, *81*, 278–284. [CrossRef]

- Haque, F.; Elumalai, N.K.; Wright, M.; Mahmud, M.A.; Uddin, A.J.M.R.B. Annealing Induced Microstructure Engineering of Antimony Tri-selenide Thin Films. *Mater. Res. Bull.* 2017, 99, 232–238. [CrossRef]

- 42. El Radaf, I.M. Structural, optical, optoelectrical and photovoltaic properties of the thermally evaporated Sb<sub>2</sub>Se<sub>3</sub> thin films. *Appl. Phys. A* **2019**, *125*, 832. [CrossRef]

- 43. Yuan, H.; Wang, Z.; Peng, Z.; Wu, J.; Yang, J. Ultra-Compact and NonVolatile Nanophotonic Neural Networks. *Adv. Opt. Mater.* **2023**, *11*, 2300215–2300224. [CrossRef]

- 44. Eslami, M.R.; Piran, P.; Bakhtiari, S.; Rezaei, M.H. Implementation of all two-input/one-output logical operations using a simple electro-optical graphene-based plasmonic structure. *Opt. Quantum Electron.* **2022**, *54*, 411. [CrossRef]

- 45. You, J.; You, G.; Li, S.; Hou, J.; Yang, C.; Chen, S.; Gao, D. Ultra-compact and low loss onchip higher order mode pass filter based on topology optimization. *Appl. Phys. Express* **2020**, *13*, 022005. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.