# Article Demonstration of Steep Switching Behavior Based on Band Modulation in WSe<sub>2</sub> Feedback Field-Effect Transistor

Seung-Mo Kim<sup>1</sup>, Jae Hyeon Jun<sup>1</sup>, Junho Lee<sup>1</sup>, Muhammad Taqi<sup>2</sup>, Hoseong Shin<sup>2</sup>, Sungwon Lee<sup>2</sup>, Haewon Lee<sup>1</sup>, Won Jong Yoo<sup>2</sup> and Byoung Hun Lee<sup>1,\*</sup>

- <sup>1</sup> Center for Semiconductor Technology Convergence, Department of Electrical Engineering, Pohang University of Science and Technology, Cheongam-ro 77, Nam-gu, Pohang 37673, Gyeongbuk, Republic of Korea; kimsm2110@postech.ac.kr (S.-M.K.); jhjun@postech.ac.kr (J.H.J.); jhlee21@postech.ac.kr (J.L.); haewon2612@postech.ac.kr (H.L.)

- <sup>2</sup> Department of Nano Science and Engineering, Sungkyunkwan University, 2066, Seobu-ro, Jangan-gu, Suwon 16419, Gyeonggi-do, Republic of Korea; mtaqi\_baiq@naver.com (M.T.); shs98753@skku.edu (H.S.); physw35@gmail.com (S.L.); yoowj@skku.edu (W.J.Y.)

- \* Correspondence: bhlee1@postech.ac.kr

**Abstract:** Feedback field-effect transistors (FBFETs) have been studied to obtain near-zero subthreshold swings at 300 K with a high on/off current ratio  $\sim 10^{10}$ . However, their structural complexity, such as an epitaxy process after an etch process for a Si channel with a thickness of several nanometers, has limited broader research. We demonstrated a FBFET using in-plane WSe<sub>2</sub> p—n homojunction. The WSe<sub>2</sub> FBFET exhibited a minimum subthreshold swing of 153 mV/dec with 30 nm gate dielectric. Our modeling-based projection indicates that the swing of this device can be reduced to 14 mV/dec with 1 nm EOT. Also, the gain of the inverter using the WSe<sub>2</sub> FBFET can be improved by up to 1.53 times compared to a silicon CMOS inverter, and power consumption can be reduced by up to 11.9%.

**Keywords:** feedback FET; 2D materials;  $WSe_2$ ; band modulation; p-n homojunction; oxygen plasma treatment

Citation: Kim, S.-M.; Jun, J.H.; Lee, J.; Taqi, M.; Shin, H.; Lee, S.; Lee, H.; Yoo, W.J.; Lee, B.H. Demonstration of Steep Switching Behavior Based on Band Modulation in WSe<sub>2</sub> Feedback Field-Effect Transistor. *Nanomaterials* **2024**, *14*, 1667. https://doi.org/ 10.3390/nano14201667

Academic Editor: Mingsheng Xu

Received: 6 October 2024 Accepted: 10 October 2024 Published: 17 October 2024

**Copyright:** © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

## 1. Introduction

Rapid advances in integrated circuit (IC) technology have inevitably been accompanied by various challenges, such as a worse leakage current and high standby power consumption [1–3]. Various countermeasures have been introduced to alleviate these problems, but they have been limited by the physical mechanisms inherent in MOSFETs, particularly by the theoretical limitation (e.g., the thermionic emission process) of subthreshold swing with a minimum of ~60 mV/dec at room temperature [2].

Steep switching devices with novel operating mechanisms have been explored to overcome the theoretical limitations of MOSFETs' operation [4–17]. In particular, Si channel feedback field-effect transistors (FBFETs) have attracted attention for their near-zero subthreshold swing (~0 mV/dec at 300 K) and their high on/off current ratio (~10<sup>10</sup>) [18–32]. The device structure of the FBFET includes a channel region divided into gated and ungated regions on the top of the intrinsic silicon on the oxide (SOI) body and the back gate on the bottom of the buried oxide (BOX) [33–36]. Although swing values lower than 60 mV/dec have been demonstrated for optimized FBFETs, their structural complexity, such as the epitaxy process after the etching process for channels a few nanometers thick, has significantly limited broader research.

Another approach to overcome this structural complexity is using 2D material-based homojunctions. Especially,  $WSe_2$  has been attracting attention as a 2D material capable of implementing a p–n homojunction [37–41].

In this paper, we report on a FBFET using an in-plane  $WSe_2$  p–n homojunction. Our device exhibited a minimum SS value of 153 mV/dec at room temperature with an on/off

ratio of ~ $10^3$ . Even though this value appears to be higher than the lower limit of the swing of a silicon MOSFET (~60 mV/dec), the abrupt transition from the off to the on state exhibited by this device demonstrates that positive feedback by potential barriers and potential wells is feasible in 2D material-based channels, as well as in Si channels, and the absolute value of swing can be scaled down by reducing the thickness of the gate dielectric. We show that the swing of the WSe<sub>2</sub> FBFET can be scaled down to 14 mV/dec by reducing the equivalent oxide thickness (EOT) of the gate dielectric down to 1 nm. The theoretical projection of the performance of the inverter using the scaled WSe<sub>2</sub> FBFET demonstrated up to 1.53 times higher gain and 11.9% lower power consumption compared to those of a silicon CMOS inverter. These results indicate that the WSe<sub>2</sub> FBFET can be useful in targeting low-power applications.

#### 2. Experiments

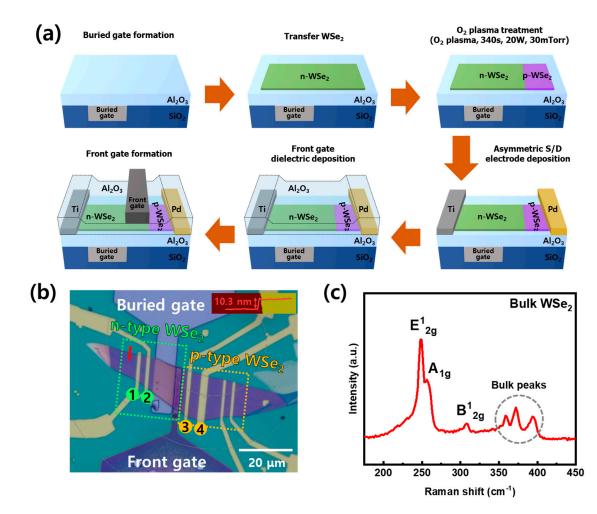

The fabrication process of the WSe<sub>2</sub> FBFET is schematically shown in Figure 1a. The buried gate structure was employed for reliable gate control, and the non-uniform electrical field due to the geometrical structure of the gate was minimized. After patterning a 9  $\mu$ m long trench on the 300 nm SiO<sub>2</sub>/Si substrate to form the buried gate, reactive-ion etching (RIE) (KVET-12000L, Korea Vacuum Tech., Daegu, Republic of Korea) was performed to form a 60 nm oxide trench pattern. To fill the gate trench, 10 nm Ti/50 nm Pt was deposited using an e-beam evaporator, and the lift-off process was performed to define the gate electrode. After the lift-off process, a chemical mechanical polishing (CMP) process was performed to level the oxide substrate and gate electrodes and remove the residual metal layer near the gate edge. Then, 30 nm thick  $Al_2O_3$  was deposited as a gate dielectric using atomic layer deposition (ALD). WSe<sub>2</sub> flakes (HQ graphene, Groningen, The Netherlands) were mechanically exfoliated using the Scotch tape technique and transferred to the  $Al_2O_3$ layer on the targeted buried gate electrode using a dry transfer method. Plasma treatment was performed to enable p-type operation in the thick WSe<sub>2</sub> flake that typically exhibits n-type characteristics. Plasma treatment was performed on the partially patterned  $WSe_2$ channel between the front gate and drain electrode at 20 W for 340 s in O<sub>2</sub> ambient, as shown in the third step of fabrication process. The device pattern was patterned using electron beam lithography (EBL), and an electron beam evaporator was used to deposit Ti on n-type WSe<sub>2</sub> and Pd on p-type WSe<sub>2</sub> to form asymmetric low-resistance S/D contacts, followed by a 30 nm Al<sub>2</sub>O<sub>3</sub> gate dielectric. Then, a highly doped 30 nm ZnO front gate layer was deposited using ALD and a 3 µm front gate pattern was formed by lithography and wet etching. For device modeling and logic circuit simulation, WSe2 FBFET modeling and logic circuit simulations were performed using HSPICE (Synopsys). The device characteristics of the WSe<sub>2</sub> FBFET were modeled by calibrating the device parameters for a thin-film transistor model (V<sub>th</sub>, SS, I<sub>on</sub>, I<sub>off</sub>). Using the developed WSe<sub>2</sub> FBFET model, the theoretical projections of scaled WSe<sub>2</sub> FBFETs were predicted, and the gain and power consumption of scaled WSe<sub>2</sub> FBFET-based logic circuits were extracted.

**Figure 1.** (a) Fabrication process of WSe<sub>2</sub> FBFET. (b) Optical image of top view of WSe<sub>2</sub> FBFET. This device includes not only FBFET but also n-/p-type WSe<sub>2</sub> FET. Red line at boundary of WSe<sub>2</sub> indicates location measured with AFM, and thickness result is shown in upper right corner. (c) Raman spectrum by 514 nm excitation of pristine WSe<sub>2</sub>.

#### 3. Results and Discussions

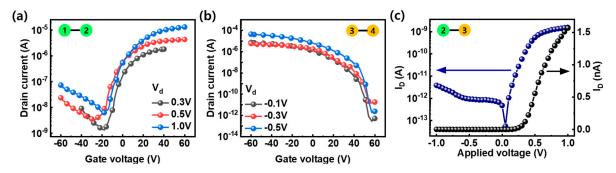

Figure 1b shows an optical microscope image of the fabricated device. This device has electrode patterns to verify the electrical characteristics of the WSe2 channel. The electrodes marked 1-2, 2-3, and 3-4 shown in the optical image are used as indicators to verify the electrical characteristics of n-type WSe<sub>2</sub>, p-n homojunction of WSe<sub>2</sub>, and p-type WSe<sub>2</sub>, respectively. The inset in Figure 1b shows the thickness of the transferred WSe<sub>2</sub> measured with an Atomic Force Microscope (AFM). The measurement location is indicated by the red line in Figure 1b. The thickness of WSe<sub>2</sub> was 10.3 nm. Figure 1c shows the Raman spectrum of the WSe<sub>2</sub> flake obtained by 514 nm excitation measured after the transfer. In the frequency range of 200–450 cm<sup>-1</sup>, three Raman peaks ( $E_{2g}^1$ ,  $A_{1g}$ ,  $B_{2g}^1$ ) characterizing WSe<sub>2</sub> are located at 247.8, 256.4, and 307.6  $cm^{-1}$ , respectively, and the other small peaks observed in the 350–400 cm<sup>-1</sup> range are the peaks from thick WSe<sub>2</sub>, related to second-order and combination Raman modes [42,43]. Figure 2 shows the electrical characteristics of the device with a channel between the electrodes indicated by numbers in the optical image in Figure 1b. Figure 2a shows the I<sub>d</sub>-V<sub>g</sub> curves of transferred pristine WSe<sub>2</sub> measured at  $V_d = 0.3, 0.5, and 1.0 V$ . The pristine  $WSe_2$  FET behaved like a depletion-mode nFET with an electron current of 13  $\mu$ A at V<sub>G</sub> = + 60 V, V<sub>d</sub> = 1.0 V. These are the typical characteristics of thick WSe<sub>2</sub> above ~5 nm [44]. The plasma-treated WSe<sub>2</sub> channel and Pd electrodes marked 3 and 4 show a p-type behavior where the current changes from  $10^{-12}$  A to  $10^{-5}$  A in the gate range from 60 V to -60 V, as shown in Figure 2b. The polarity conversion from n-type

to p-type behavior after the plasma treatment process was successfully confirmed even though both devices operate in depletion mode. As shown in Figure 2c, the output curve of the device formed between the electrodes marked 2 and 3 behaves like a forward-rectifying diode and exhibits 1.6 nA at forward bias ( $V_d = 1.0 V$ ), about 400 times higher than at reverse bias ( $V_d = -1.0 V$ ), confirming the successful formation of a p–n homojunction in WSe<sub>2</sub>.

**Figure 2.**  $I_d-V_g$  characteristics of FET composed of (a) Ti electrodes (1, 2) and the transferred pristine WSe<sub>2</sub> channel; (b) Pd electrodes (3, 4) and O<sub>2</sub> plasma-treated WSe<sub>2</sub> channel. (c) Diode characteristics of the p–n homojunction of WSe<sub>2</sub> between the Ti electrode (2) and Pd electrode (3). The numbers in the green and yellow circles on the graph represent the electrodes shown in the optical image of the device, as shown in Figure 1b.

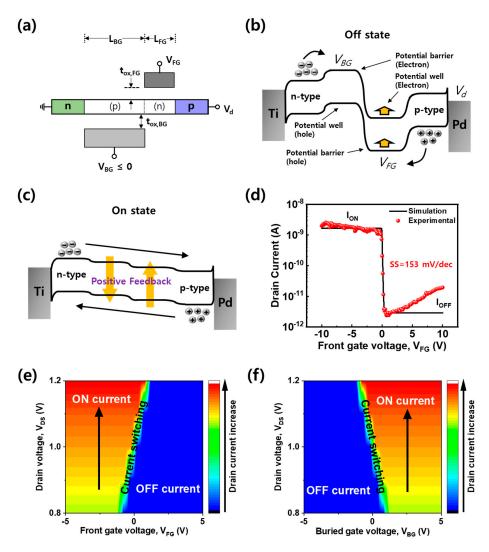

A cross-sectional schematic of the WSe<sub>2</sub> FBFET is shown in Figure 3a. When a forward bias is applied to the drain (Pd electrode), the forward current of the p-n junction flows from drain to source. In the off state of the FBFET, a buried gate bias ( $V_{BG}$ ) and a front gate bias  $(V_{FG})$  modulate the WSe<sub>2</sub> channels to p-type and n-type, respectively. These gate voltages form the potential barriers and wells of holes and electrons that turn off the FBFET in the ideal band diagram, as shown in Figure 3b. When  $V_{FG}$  sweeps from the voltage forming the potential barrier to the opposite polarity (in this case, from 10 V to -10 V), the potential barrier for hole injection from drain to channel is lowered, and some of the holes are injected and accumulate in the potential well for hole. As holes are accumulated in the potential well, the potential barrier for electrons is lowered. As a result, electrons are injected into the channel from the source and accumulate in the electron potential well, further lowering the potential barrier for holes. When VFG lowers the potential barrier enough to enter the feedback loop, this cycle occurs quickly and spontaneously, causing dramatic barrier modulation and switching to the on state, as shown in Figure 3c. Figure 3d shows the  $I_d$ -V<sub>FG</sub> curve measured from the WSe<sub>2</sub> FBFET at  $V_d$  = 1.0 V,  $V_{BG}$  = 0 V. The on/off ratio is  $\sim 10^3$ . The minimum SS value is 153 mV/dec. Even though this value is higher than the lower limit of silicon MOSFET ~60 mV/dec, an abrupt current increase due to the feedback mechanism at the homojunction is successfully demonstrated, even in the 2D material channel. The simulation confirmed that abrupt current switching behavior follows the feedback mechanism. Since the current switching point is affected by the barrier structure, it can vary depending on  $V_d$  and  $V_{BG}$ . The fitting did not work for the negative-bias region because the high leakage current at the negative-bias region due to band-to-band tunneling was not included in the modeling. A simulated correlation map between the front gate bias and the drain bias is shown in Figure 3e. V<sub>d</sub> determines the initial number of carriers that cannot cross the barrier formed by the front gate bias. At a high  $V_d$ , the drain current increases, and the number of carriers crossing the barrier increases, making it easier to enter the feedback mechanism. Therefore, when  $V_d$  is larger than 1.0 V, current switching can occur at  $V_{FG} > 0$  V. Figure 3f shows the simulated correlation map between the buried gate bias and the drain bias. When  $V_{bg}$  sweeps (in this case from -5 V to 5 V), the potential barrier for electrons controls the carriers, so electrons become the majority carriers. The device can be operated as an n-type feedback FET.

**Figure 3.** (a) Configuration of the WSe<sub>2</sub> FBFET considering  $L_{BG} = 9 \ \mu m$ ,  $L_{FG} = 3 \ \mu m$ ,  $t_{ox,FG} = t_{ox,BG} = 30 \ nm$ . (p) and (n) are charged carrier types by band modulation. Band alignment of the (b) off state and (c) on state for the WSe<sub>2</sub> FBFET. (d) I<sub>d</sub>-V<sub>FG</sub> characteristics of the WSe<sub>2</sub> FBFET at V<sub>d</sub> = 1.0 V, V<sub>BG</sub> = 0 V. The simulated correlation map of drain current between (e) V<sub>FG</sub> and (f) V<sub>BG</sub> at different V<sub>d</sub>.

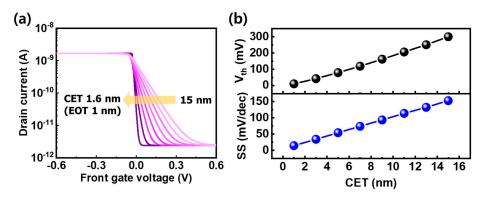

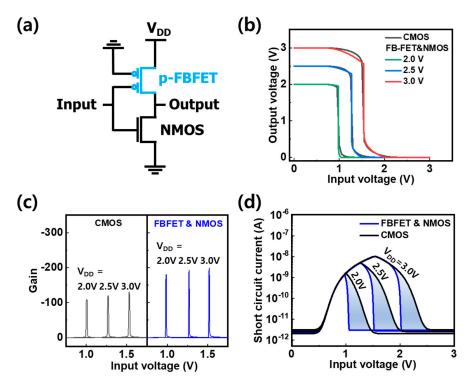

Since the high swing value of the WSe<sub>2</sub> FBFET is due to the thick gate dielectric, a theoretical projection of swing was obtained using the device model fitted to the experimental data shown in Figure 3d. Figure 4a shows the simulated I–V characteristics as a function of gate dielectric thickness. The capacitance equivalent thickness (CET) of the 30 nm  $Al_2O_3$  front gate dielectric is ~15 nm. As the CET of the gate dielectric targeting 1 nm of EOT is scaled down to 1.6 nm, the threshold voltage decreases to 10 mV from 300 mV, and the swing decreases to 14 mV/dec from 153 mV/dec, as shown in Figure 4b. Figure 5a shows a schematic of the inverter circuit, which consists of a pull-down WSe<sub>2</sub> FBFET with a gate dielectric scaled down to 1 nm EOT (p-FBFET) and an n-type pull-up MOSFET. The n-type and p-type MOSFETs used in the simulation for the inverters had a 3 nm thick SiO<sub>2</sub> gate dielectric, a length of 300  $\mu$ m, and a width of 1  $\mu$ m and 2 µm, respectively. Unlike the p-MOSFET, the p-FBFET, which has two gates, applies the input voltage to the front gate, which is responsible for abrupt current transition, and grounds the buried gate in the circuit configuration. In the WSe<sub>2</sub> FBFET, the buried gate functions as the back gate. The inverter characteristics for supply voltages at 2.0, 2.5, and 3.0 V composed of p-FBFET were compared with an inverter using silicon CMOS technology (Figure 5b). The transfer curve of the inverter using the p-FBFET is similar to the transfer curve of a silicon CMOS inverter, but the abrupt voltage transition caused by the characteristics of the p-FBFET improves the gain of the inverter. The small-signal gain of the inverter using the FBFET was 199 at  $V_{DD}$  = 3.0 V, while that of the CMOS inverter was 130, as shown in Figure 5c. The gain of the inverter using p-FBFET was about 1.53 times higher than that of the CMOS inverter. Because of the abrupt transition, the power consumption during the state transition decreased, as shown in Figure 5d. The blue area represents the current difference between the two inverters at each supply voltage. The power consumptions of the inverter using p-FBFET and of the CMOS inverter were 5.24 nW and 5.86 nW at  $V_{DD}$  = 3.0 V, respectively, with the inverter using p-FBFET showing a difference in power consumption of -11.9% compared to the CMOS inverter. Table 1 compares the gain and power consumption between the WSe<sub>2</sub> FBFET inverters at various EOTs and the CMOS inverter. When the EOT decreases from 5 nm to 1 nm, the ratio of the gain between those inverters increases to 1.53 times from 1.42 times, and the difference in power consumption is reduced to -11.9% compared to the CMOS inverter.

**Figure 4.** (a)  $I_d$ – $V_{FG}$  characteristics, (b) threshold voltage ( $V_{th}$ ), and subthreshold swing (SS) values for WSe<sub>2</sub> FBFET when the capacitance equivalent thickness (CET) of the front gate dielectric is reduced from 15 to 1.6 nm.

**Figure 5.** (a) Schematic of the inverter circuit based on WSe<sub>2</sub> FBFET (p-FBFET) and n-MOSFET. Comparison of inverter characteristics composed of p-FBFET with an EOT of 1 nm and p-MOSFET with CMOS technology. (b) Output vs. input voltage curve. (c) Voltage gain vs. input voltage curve. (d) Short-circuit current vs. input voltage curve.

| Pull-Up Devices        | EOT (nm) | Comparison with Performance of CMOS Inverter |                   |

|------------------------|----------|----------------------------------------------|-------------------|

|                        |          | Gain                                         | Power Consumption |

| WSe <sub>2</sub> FBFET | 1        | 1.53 times                                   | -11.9%            |

|                        | 3        | 1.44 times                                   | -6.8%             |

|                        | 5        | 1.42 times                                   | -3.4%             |

**Table 1.** Comparison between WSe<sub>2</sub> FBFET and CMOS inverters for gain and power consumption at various EOTs.

This table is a performance comparison at  $V_{DD}$  = 3.0 V.

## 4. Conclusions

A FBFET using an in-plane WSe<sub>2</sub> p–n homojunction has been demonstrated, and the performance of the p-FBFET has been theoretically estimated at a 1 nm EOT gate dielectric. The abrupt current switching behaviors of the WSe<sub>2</sub>-based p-type FBFET confirmed that the electrically modulated p–n homojunction can be used for the feedback mechanism, even in 2D materials. The theoretically projected inverter performance with a 1 nm EOT gate dielectric indicates that the gain is 1.53 times higher than that of a CMOS inverter, with a 11.9% lower power consumption. Considering that TMDC-based devices are being seriously considered for middle-of-line or backend-of-line co-integration, WSe<sub>2</sub>-based FBFETs are promising candidates for such applications.

Author Contributions: Conceptualization, investigation, S.-M.K., J.L., M.T. and H.S.; software, J.H.J.; validation, S.-M.K., J.L. and H.L.; resources, methodology, S.-M.K., J.L., M.T., H.S., S.L. and W.J.Y.; writing—original draft preparation, S.-M.K. and J.H.J.; supervision, writing—review and editing, B.H.L. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was supported by the Nanomaterials Development Program (2022M3H4A1A04096496) and the Innovative Research Center Program (No. RS-2023-00260527) through the National Research Foundation of Korea (NRF), funded by the Ministry of Science and ICT (MSIT), Korea.

Data Availability Statement: Data are contained within the article.

Conflicts of Interest: The authors declare no conflict of interest.

### References

- 1. Thompson, S.E.; Srivatsan, P. Moore's law: The future of Si microelectronics. Mater. Today 2006, 9, 20–25. [CrossRef]

- 2. Takayasu, S. Perspectives of low-power VLSI's. IEICE Trans. Electron. 2004, 87, 429-436.

- 3. Jo, J.; Shin, C. Study of Temperature Effects on Negative Capacitance Field-Effect Transistor. IEEK 2014, 37, 70–72.

- 4. Khan, A.I.; Chatterjee, K.; Wang, B.; Drapcho, S.; You, L.; Serrao, C.; Bakaul, S.R.; Ramesh, R.; Salahuddin, S. Negative capacitance in a ferroelectric capacitor. *Nat. Mater.* **2015**, *14*, 182–186. [CrossRef]

- Ko, E.; Lee, J.W.; Shin, C. Negative Capacitance FinFET with Sub-20-mV/decade Subthreshold Slope and Minimal Hysteresis of 0.48 V. IEEE Electron. Device Lett. 2017, 38, 418–421. [CrossRef]

- Ko, E.; Shin, J.; Shin, C. Steep switching devices for low power applications: Negative differential capacitance/resistance field effect transistors. *Nano Converg.* 2017, 5, 306–309. [CrossRef] [PubMed]

- Jo, J.; Choi, W.Y.; Park, J.-D.; Shim, J.W.; Yu, H.-Y.; Shin, C. Negative Capacitance in Organic/Ferroelectric Capacitor to Implement Steep Switching MOS Devices. *Nano Lett.* 2015, 15, 4553–4556. [CrossRef]

- Ko, E.; Shin, C. Effective drive current in steep slope FinFET (vs. conventional FinFET). *Appl. Phys. Lett.* 2017, 111, 152105. [CrossRef]

- Shukla, N.; Tjathachary, A. A steep-slope transistor based on abrupt electronic phase transition. *Nat. Commun.* 2015, 6, 7812. [CrossRef]

- 10. Shin, J.; Ko, E.; Shin, C. Analysis on the Operation of Negative Differential Resistance FinFET with Pb(Zr<sub>0.52</sub>Ti<sub>0.48</sub>)O<sub>3</sub> Threshold Selector. *IEEE Trans. Electron Devices* **2018**, *65*, 19–22. [CrossRef]

- 11. Liu, T.J.K.; Markovic, D.; Stojanovic, V.; Alon, E. The relay reborn. IEEE Spectr. 2012, 49, 40-43. [CrossRef]

- 12. Dennard, R.; Gaensslen, F.; Yu, H.-N.; Rideout, V.; Bassous, E.; LeBlanc, A. Design of ion-implanted MOSFET's with very small physical dimensions. *IEEE J. Solid-State Circuits* **1974**, *9*, 256–268. [CrossRef]

- 13. Gopalakrishnan, K.; Griffin, P.B.; Plummer, J.D. Impact ionization MOS (I-MOS)-Part I: Device and circuit simulations. *IEEE Trans. Electron Devices* 2005, 52, 69–76. [CrossRef]

- Gopalakrishnan, K.; Griffin, P.B.; Plummer, J.D. I-MOS: A novel semiconductor device with a subthreshold slope lower than kT/q. In Proceedings of the IEDM—International Electron Devices Meeting, Technical Digest, San Francisco, CA, USA, 8–11 December 2002; pp. 289–292.

- Choi, W.Y.; Park, B.-G.; Lee, J.D.; Liu, T.-J.K. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. *IEEE Electron Device Lett.* 2007, 28, 743–745. [CrossRef]

- 16. Choe, K.; Shin, C. Adjusting the operating voltage of an nanoelectromechanical relay using negative capacitance. *IEEE Electron Device Lett.* **2017**, *64*, 5270–5273. [CrossRef]

- 17. Ning, C.; Renrong, L.; Jing, W.; Wei, Z.; Xu, J. A PNPN tunnel field-effect transistor with high-k gate and low-k fringe dielectrics. *J. Semiconduct.* **2012**, *33*, 084004.

- 18. Jing, W.; Cristoloveanu, S.; Royer, C.L.; Zaslavsky, A. A systematic study of the sharp-switching Z2-FET device: From mechanism to modeling and compact memory applications. *Solid-State Electron.* **2013**, *90*, 2–11.

- 19. El Dirani, H.; Fonteneau, P.; Solaro, Y.; Legrand, C.A.; Marin-Cudraz, D.; Ferrari, P.; Cristoloveanu, S. Legrand. Sharp-switching band-modulation back-gated devices in advanced FDSOI technology. *Solid-State Electron.* **2017**, *128*, 180–186. [CrossRef]

- Joe, S.; Kang, H.; Choi, N.; Kang, M.; Park, B.; Lee, J. Diode-Type NAND Flash Memory Cell String Having Super-Steep Switching Slope Based on Positive Feedback. *IEEE Trans. Electron Devices* 2016, 63, 1533–1538. [CrossRef]

- Choi, K.; Woo, S.; Kang, W.; Lee, S.; Kim, C.; Bae, J.; Lim, S.; Lee, J. A Split-Gate Positive Feedback Device With an Integrate-and-Fire Capability for a High-Density Low-Power Neuron Circuit. *Front. Neurosci.* 2018, 12, 704. [CrossRef]

- Choi, N.; Joe, S.; Park, B.; Lee, J. Design Consideration of Diode-Type NAND Flash Memory Cell String Having Super-Steep Switching Slope. *IEEE J. Electron Devices Soc.* 2016, 4, 328–334. [CrossRef]

- 23. Cristoloveanu, S.; Wan, J.; Le Royer, C.; Zaslavsky, A. Innovative Sharp Switching Devices. ECS Trans. 2013, 54, 65–75. [CrossRef]

- 24. Wan, J.; Cristoloveanu, S.; Le Royer, C.; Zaslavsky, A. A feedback silicon-on-insulator steep switching device with gate-controlled carrier injection A. *Solid-State Electron.* **2012**, *76*, 109–111. [CrossRef]

- 25. Cristoloveanu, S.; Wan, J.; le Royer, C. Sharp-Switching SOI Devices. In Proceedings of the 223rd ECS Meeting, Toronto, ON, Canada, 12–17 May 2013.

- 26. El Dirani, H.; Solaro, Y.; Fonteneau, P.; Ferrari, P.; Cristoloveanu, S. Sharp-switching Z2-FET device in 14 nm FDSOI technology. In Proceedings of the 45th European Solid State Device Research Conference (ESSDERC), Graz, Austria, 14–18 September 2015.

- 27. Dirani, H.E.; Solaro, Y.; Fonteneau, P.; Ferrari, P.; Cristoloveanu, S. Properties and mechanisms of Z2-FET at variable temperature. *Solid State Electron.* **2016**, *115*, 201–206. [CrossRef]

- Navarro, S.; Marquez, C.; Lee, K.H.; Navarro, C.; Parihar, M.; Park, H.; Galy, P.; Bawedin, M.; Kim, Y.T.; Cristoloveanu, S.; et al. Investigation of thin gate-stack Z<sup>2</sup>-FET devices as capacitor-less memory cells. *Solid-State Electron.* 2019, 159, 12–18. [CrossRef]

- Marquez, C.; Navarro, S.; Navarro, C.; Salazar, N.; Galy, P.; Cristoloveanu, S.; Gamiz, F. Temperature and gate leakage influence on the Z<sup>2</sup>-FET memory operation. In Proceedings of the 49th European Solid-State Device Research Conference (ESSDERC), Cracow, Poland, 23–26 September 2019.

- El Dirani, H.; Solaro, Y.; Fonteneau, P. A sharp-switching gateless device (Z<sup>3</sup>-FET) in advanced FDSOI technology. In Proceedings of the 2016 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), Vienna, Austria, 25–27 January 2016.

- 31. Solaro, Y.; Fonteneau, P. A sharp-switching device with free surface and buried gates based on band modulation and feedback mechanisms. *Solid State Electron.* **2016**, *116*, 8–11. [CrossRef]

- El Dirani, H.; Fonteneau, P.; Solaro, Y.; Ferrari, P.; Cristoloveanu, S. Novel FDSOI band-modulation device: Z<sup>2</sup>-FET with Dual Ground Planes. In Proceedings of the 46th European Solid-State Device Research Conference (ESSDERC), Lausanne, Switzerland, 12–15 September 2016.

- 33. Kwon, S.; Navarro, C.; Gamiz, F.; Cristoloveanu, S.; Galy, P.; Choi, M.; Kim, Y.-T.; Ahn, J. Characteristics of band modulation FET on sub 10 nm SOI. *Jpn. J. Appl. Phys.* **2019**, *58*, SBBB07. [CrossRef]

- Kwon, S.; Navarro, C.; Galy, P.; Cristoloveanu, S.; Gamiz, F.; Ahn, J.; Kim, Y.-T. Memory Operations of Zero Impact Ionization, Zero Subthreshold Swing FET Matrix Without Selectors. *IEEE Electron Device Lett.* 2020, *41*, 361–364. [CrossRef]

- Kwon, S.; Navarro, C.; Gamiz, F.; Galy, P.; Cristoloveanu, S.; Kim, Y.-T.; Ahn, J. Improved Retention Characteristics of Z<sup>2</sup>-FET Employing Half Back-Gate Control. *IEEE Trans. Electron Devices* 2021, 68, 1041–1044. [CrossRef]

- Kwon, S.; Navarro, C.; Gamiz, F.; Cristoloveanu, S.; Kim, Y.-T.; Ahn, J. Memory Operation of Z<sup>2</sup>-FET Without Selector at High Temperature. *IEEE J. Electron Devices Soc.* 2021, 9, 658–662. [CrossRef]

- Mitta, S.B.; Ali, F.; Yang, Z.; Moon, I.; Ahmed, F.; Yoo, T.J.; Lee, B.H.; Yoo, W.J. Gate-Modulated Ultrasensitive Visible and Near-Infrared Photodetection of Oxygen Plasma-Treated WSe<sub>2</sub> Lateral pn-Homojunctions. ACS Appl. Mater. Interfaces 2020, 12, 23261–23271. [CrossRef] [PubMed]

- Thi, H.Y.L.; Ngo, T.D.; Phan, N.A.N.; Yoo, W.J.; Watanabe, K.; Taniguchi, T.; Aoki, N.; Bird, J.P.; Kim, G.-H. Self-Forming p–n Junction Diode Realized with WSe<sub>2</sub> Surface and Edge Dual Contacts. *Small* 2022, *18*, 2204547. [CrossRef] [PubMed]

- Shin, H.; Taqi, M.; Ali, F.; Lee, S.; Choi, M.S.; Kim, C.; Lee, B.-H.; Liu, X.; Sun, J.; Oh, B.; et al. Self-Powered 2D MoS<sub>2</sub>/WO<sub>x</sub>/WSe<sub>2</sub> Heterojunction Photodetector Realized by Oxygen Plasma Treatment. *Adv. Mater. Interfaces* 2022, *9*, 2201785.

- Moon, I.; Lee, S.; Lee, M.; Kim, C.; Seol, D.; Kim, Y.; Kim, K.H.; Yeom, G.Y.; Teherani, J.T.; Hone, J.; et al. The device level modulation of carrier transport in a 2D WSe<sub>2</sub> field effect transistor via a plasma treatment. *Nanoscale* 2019, *11*, 17368. [CrossRef] [PubMed]

- 41. Yang, S.; Lee, G.; Kim, J.; Yang, S.; Lee, C.-H.; Kim, J. An in-plane WSe<sub>2</sub> p–n homojunction two-dimensional diode by laser-induced doping. *J. Mater. Chem. C* 2020, *8*, 8393–8398. [CrossRef]

- 42. Del Corro, E.; Terrones, H.; Elias, A.; Fantini, C.; Feng, S.; Nguyen, M.A.; Mallouk, T.E.; Terrones, M.; Pimenta, M.A. Excited excitonic states in 1L, 2L, 3L, and bulk WSe<sub>2</sub> observed by resonant Raman spectroscopy. *ACS Nano* **2014**, *8*, 9629–9635. [CrossRef]

- 43. Wang, X.; Chen, X.; Zhou, Y.; Park, C.; An, C.; Zhou, Y.; Zhang, R.; Gu, C.; Yang, W.; Yang, Z. Pressure-induced iso-structural phase transition and metallization in WSe<sub>2</sub>. *Sci. Rep.* **2017**, *7*, 46694. [CrossRef]

- Pudasaini, P.R.; Oyedele, A.; Zhang, C.; Stanford, M.G.; Cross, N.; Wong, A.T.; Hoffman, A.N.; Xiao, K.; Duscher, G.; Mandrus, D.G.; et al. High-performance multilayer WSe<sub>2</sub> field-effect transistors with carrier type control. *Nano Res.* 2018, 11, 722–730. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.