Article

## Electrical and Hysteresis Characteristics of Top-Gate InGaZnO Thin-Film Transistors with Oxygen Plasma Treatment Prior to TEOS Oxide Gate Dielectrics

Tsung-Cheng Tien<sup>1</sup>, Tsung-Eong Hsieh<sup>1</sup>, Yih-Shing Lee<sup>2,\*</sup>, Yu-Hsin Wang<sup>2</sup> and Ming-Ling Lee<sup>2</sup>

- <sup>1</sup> Department of Materials Science and Engineering, National Yang Ming Chiao Tung University, Hsinchu 30010, Taiwan; ttt123175721@yahoo.com.tw (T.-C.T.); tehsieh@cc.nctu.edu.tw (T.-E.H.)

- <sup>2</sup> Department of Electro-Optical Engineering, Minghsin University of Science and Technology, Hsinchu 30401, Taiwan; zaiword@gmail.com (Y.-H.W.); mingling@must.edu.tw (M.-L.L.)

- \* Correspondence: yslee@must.edu.tw; Tel.: +886-3-5593142 (ext. 3383)

Abstract: We report the impact of oxygen (O<sub>2</sub>) plasma time on an amorphous indium–gallium–zinc oxide (a-IGZO) thin-film surface that was carried out before TEOS deposition in order to optimize the performance of thin-film transistors (TFTs). The  $O_2$  plasma time of 60 s possessed the largest on/off current ratio of >10<sup>8</sup>, with a field-effect mobility ( $\mu_{FE}$ ) of 8.14 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and the lowest subthreshold swing (S.S.) of 0.395 V/decade, with a threshold voltage ( $V_{th}$ ) of -0.14 V. However, increases in  $I_{off}$  and S.S. and decreases in the  $\mu_{FE}$  were observed for the longer O<sub>2</sub> plasma time of 120 s. As the O<sub>2</sub> plasma time increased, the reduction in the carrier concentration in the IGZO channel layer may have resulted in an increase in  $V_{th}$  for the IGZO TFT devices. With an increase in the O<sub>2</sub> plasma time, the surface roughness of the IGZO channel layer was increased, the carbon content in the TEOS oxide film was reduced, and the film stoichiometry was improved. The SIMS depth profile results showed that the O/Si ratio of TEOS oxide for the sample with the O<sub>2</sub> plasma time of 60 s was 2.64, and its IGZO TFT device had the best electrical characteristics. In addition, in comparison to the IGZO TFT device without  $O_2$  annealing, larger clockwise hysteresis in the transfer characteristics revealed that a greater number of electrons were trapped at the interface between TEOS oxide and the a-IGZO channel layer. However, hysteresis curves of the O<sub>2</sub>-annealed IGZO TFTs with various O<sub>2</sub> plasma times were greatly reduced, meaning that the electron traps were reduced by O<sub>2</sub> annealing.

**Keywords:** O<sub>2</sub> plasma time and annealing; hysteresis; top-gate IGZO thin-film transistors; TEOS oxide gate dielectrics

### 1. Introduction

Due to fast advances in optoelectronic technology, the next generation of displays will have thinner, lighter, and bigger screens. High-performance thin-film transistors (TFTs) have received a lot of interest [1–6]. Because of their great field-effect mobility ( $\mu_{FE}$ ) (>10 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) and lower processing temperatures, amorphous oxide semiconductors (AOSs) are suitable for TFT channel materials [7,8] and make it possible to drive TFTs in active-matrix organic light-emitting diode (AMOLED) displays. For amorphous indium–gallium–zinc oxide (a-IGZO) TFTs, the traditional bottom gate structure has been researched extensively [9,10] in our previous studies. However, due to large parasitic capacitance and low scalability, this structure is inappropriate to integrate into the system peripheral circuits on the glass and implement superior AMOLED displays. As a result, self-aligned top-gate a-IGZO TFTs devices with high performance and good stability are required for AMOLED display applications [11,12].

In general, the electrical properties of a-IGZO TFTs, including  $V_{th}$ , subthreshold swing (S.S.),  $\mu_{FE}$ , and  $I_{on}/I_{off}$  current ratio, can clearly be controlled by varying the partial pressure of oxygen (O<sub>2</sub>) during a-IGZO channel layer deposition with radio frequency

Citation: Tien, T.-C.; Hsieh, T.-E.; Lee, Y.-S.; Wang, Y.-H.; Lee, M.-L. Electrical and Hysteresis Characteristics of Top-Gate InGaZnO Thin-Film Transistors with Oxygen Plasma Treatment Prior to TEOS Oxide Gate Dielectrics. *Coatings* 2022, 12, 383. https://doi.org/10.3390/ coatings12030383

Academic Editor: Jiangwei Liu

Received: 27 January 2022 Accepted: 11 March 2022 Published: 14 March 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). sputtering [9,13]. Jeong et al. [14] reported that  $O_2$  plasma treatment on the a-IGZO channel layer decreases the oxygen vacancy density of the IGZO films at low processing temperatures, improving the IGZO channel layer material and the performance of IGZO TFT devices. Pu et al. reported [15] the effects of O<sub>2</sub> plasma treatment on solution-processed a-IGZO TFTs. The plasma-treated devices not only showed greater mobility and a greater on/off current ratio, but also a monotonic increase in the SS. with the plasma time. The effects of several plasma treatments on a-IGZO TFTs, including O<sub>2</sub>, nitrogen (N<sub>2</sub>), and argon (Ar), were observed [16] by Kim et al. They used X-ray photoelectron spectroscopy (XPS) to investigate oxygen stoichiometry in a-IGZO TFTs in diverse plasma conditions. The results indicated that  $O_2$  and  $N_2$  plasmas decreased oxygen vacancies, but Ar plasma treatment increased them. Liu et al. recently reported [17] on IGZO thin films that were treated with an Ar/O<sub>2</sub> plasma combination with various oxygen content ratios, resulting in the bottom-gate IGZO TFTs have improved device operation characteristics. Wang et al. reported [18] the O<sub>2</sub> plasma treatment on gate dielectrics (Al<sub>2</sub>O<sub>x</sub>) for a-IGZO TFTs and demonstrated that O<sub>2</sub> plasma treatment can improve the gate dielectric performance. The results were ascribed to passivating the interfacial and bulk traps by reducing the oxygen vacancies. Most notably, this was the first study to our knowledge that focused on the effects of the  $O_2$  plasma treatment prior to the tetraethyl-orthosilicate (TEOS) oxide gate dielectric deposition and O<sub>2</sub> annealing on the electrical characteristics of top-gate IGZO TFTs, wherein the compositions of TEOS oxide interfaces with a-IGZO films were reported.

In this study, top-gate IGZO TFT devices with various O<sub>2</sub> plasma times prior to TEOS gate dielectric and O<sub>2</sub> annealing after TEOS oxide deposition were fabricated using the same plasma-enhanced chemical vapor deposition (PECVD) system. Moreover, the electrical and hysteresis characteristics of the IGZO TFT devices using O<sub>2</sub> annealing after TEOS oxide deposition were evaluated. Additionally, atomic force microscope (AFM) and X-ray photoelectron spectroscopy (XPS) tests were performed to investigate the surface morphologies and compositions of the IGZO films. A depth profile analysis of the secondary ion mass spectrometer (SIMS) was conducted to verify the compositions of TEOS oxide interface with a-IGZO films treated by different O<sub>2</sub> plasma times. The best  $\mu_{FE}$  of 8.14 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>, S.S. of 0.395 V/decade,  $V_{th}$  of -0.14 V, and lower  $\Delta V_{th}$  of 0.5 V from the hysteresis curve were obtained in the IGZO TFTs that had been subjected to O<sub>2</sub> plasma treatment for 60 s and O<sub>2</sub> annealing.

#### 2. Experimental Methods

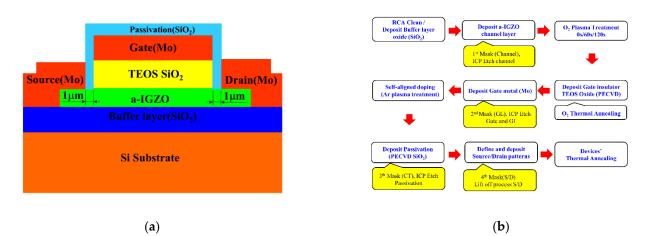

The cross-sectional schematic of the top-gate IGZO TFT structure employed in this investigation is shown in Figure 1a. Details of the devices' fabricating processes can be found elsewhere [19]. The O<sub>2</sub> plasma time was varied in order to verify the effects of O<sub>2</sub> plasma prior to depositing the TEOS gate dielectric on the electrical and hysteresis characteristics of the IGZO TFT devices. The O<sub>2</sub> plasma treatment was performed at various treatment times using an Oxford PECVD system prior to depositing TEOS oxide at 350 °C at a fixed deposition power of 40 W. The system working pressure was 700 m Torr with an O<sub>2</sub> flow of 250 sccm. After TEOS oxide deposition, the samples were annealed at 400 °C at a working pressure of 5 mTorr in an O<sub>2</sub> ambient atmosphere of 40 sccm for 1 h in the same PECVD system. Figure 1b summarizes the process charts for each step of the top-gate IGZO TFTs employed in this investigation. For the  $I_{DS}$ - $V_{GS}$  transfer characteristics and  $I_{GS}$ - $V_{GS}$ ,  $V_{GS}$  varied from -15 V to +15 V in 0.3 V steps for  $V_{DS}$  = 0.1 V in the tested devices. The Agilent 4156A precision semiconductor parameter analyzer was employed to thoroughly evaluate and compare the electrical and hysteresis characteristics of the tested devices, and the measurement temperature was maintained at 25 °C.

**Figure 1.** (a) Cross-sectional diagram of a top-gate IGZO thin-film transistor (TFT) structure. (b) Process charts of the top-gate IGZO TFTs used in this study.

In this experiment, the channel width  $W = 100 \mu m$  and the channel length  $L = 5 \mu m$  were used. Figure 1a shows the source and drain offsets, which were designed at 1  $\mu m$ . The  $\mu_{FE}$  was calculated using the following equation:

$$\mu_{FE} = \frac{L \times G_{m(max)}}{W \times C_{ox} \times V_{DS}} \tag{1}$$

where  $C_{ox}$  is the TEOS oxide capacitance per unit area and the maximum transconductance  $G_{m(max)} = (\partial I_{DS}/\partial V_{GS})_{max}$  at  $V_{DS} = 0.1$  V. The S.S. was taken as the value of  $(dlog (I_{DS})/d V_{GS})^{-1}$  when the  $I_{DS}$  was in the range of  $10^{-10}$ – $10^{-9}$  A.

Film thickness was examined and fitted using the spectroscopic ellipsometer (SE) (M-2000U) and CompleteEASE software (J. A. Woollam Co., Inc., Lincoln County, NE, United States), respectively. Surface morphology tests were employed using an atomic force microscope (AFM, Veeco Dimension 3100) at a scan area of  $2 \times 2 \mu m$ . X-ray photoelectron spectroscopy (XPS, Thermo Fisher Scientific Theta Probe (Waltham, MA, USA)) was also employed to characterize the composition of the IGZO films. The depth profile analysis of the secondary ion mass spectrometer (SIMS, CAMECA IMS 7F) was conducted to verify the compositions of the TEOS oxide interface with a-IGZO films treated with O<sub>2</sub> plasma. In order to compare the effect of O<sub>2</sub> annealing, we prepared the TEOS oxide on the a-IGZO film without O<sub>2</sub> annealing with an O<sub>2</sub> plasma time of 60 s to determine the hysteresis characteristics.

#### 3. Results and Discussion

#### 3.1. Surface Roughness Analysis of a-IGZO Films at Various O<sub>2</sub> Plasma Times

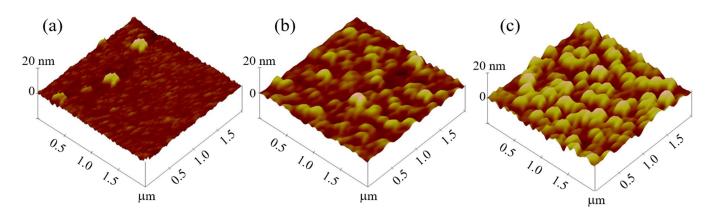

Figure 2a–c compares the AFM surface morphology characterizations of the a-IGZO channel layers with different  $O_2$  plasma times, and their z range, root mean square (RMS), and average roughness (Ra) are summarized in Table 1. Plasma bombardment of the channel surface is generally believed to increase surface roughness, as shown in Figure 2. Although the RMS and Ra roughness monotonically increased with the increase in the  $O_2$  plasma time, the z range of the a-IGZO films with the  $O_2$  plasma times of 0 and 60 s was lower than that of the  $O_2$  plasma time of 120 s. The deteriorated electrical properties of the IGZO TFTs were found to be reasonably useful for ascribing the cause of the longer  $O_2$  plasma time to the surface roughness in a later section following the presentation of results of the device characteristic analysis.

**Figure 2.** AFM surface morphology characterization of the a-IGZO films at the O<sub>2</sub> plasma times of (**a**) 0, (**b**) 60, and (**c**) 120 s.

**Table 1.** Z range, root mean square (RMS) roughness, and average roughness (Ra) of the a-IGZO films at various O<sub>2</sub> plasma times.

| O <sub>2</sub> Plasma Time (s) | Z Range (nm) | RMS (nm) | Ra (nm) |

|--------------------------------|--------------|----------|---------|

| 0                              | 8.329        | 0.671    | 0.458   |

| 60                             | 7.877        | 1.049    | 0.817   |

| 120                            | 11.14        | 1.857    | 1.531   |

#### 3.2. Electrical Characteristics of IGZO TFTs at Various O<sub>2</sub> Plasma Times

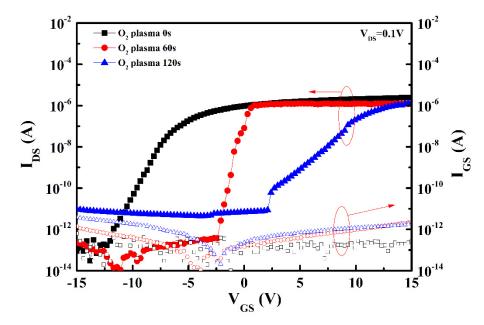

Figure 3 shows the typical  $I_{DS}$ - $V_{GS}$  transfer characteristics and  $I_{GS}$ - $V_{GS}$  curves of the IGZO TFTs at various O2 plasma times prior to the deposition of the TEOS oxide gate dielectrics.  $V_{th}$  is set as the gate voltage ( $V_{GS}$ ) when the drain current ( $I_{DS}$ ) is at a constant value ( $10^{-9} \times (W/L)$  A). Measurements were performed with more than three samples per device. The measured capacitance per unit area  $(C_{ox})$  of the gate dielectric was  $4.98 \times 10^{-8}$  F/cm<sup>2</sup> in this study. Table 2 shows the average values and standard variations in the electrical parameters extracted from the IGZO TFTs at various  $O_2$  plasma times. It is clearly confirmed in Figure 3 that the transfer curves shifted positively as the O<sub>2</sub> plasma time increased as a result of the lower on-current  $(I_{on})$  and higher off-current  $(I_{off})$  within the IGZO TFT channel. In addition, a compliance cut-off phenomenon that was clearly visible in the transfer curves at the  $O_2$  plasma times of 60 and 120 s was attributed to a higher total resistance between the source and drain electrodes as the O<sub>2</sub> plasma time increased. Moreover, the gate leakage current ( $I_{GS}$ ) gradually increased from  $10^{-13}$  to  $10^{-12}$  A, which occurred as the O<sub>2</sub> plasma time increased. As shown in Table 1, the a-IGZO film's roughness monotonically increased as the  $O_2$  plasma time increased; therefore, the gate leakage current ( $I_{GS}$ ) of the IGZO TFTs gradually increased by one order of magnitude from when the TEOS gate oxide was deposited after the O<sub>2</sub> plasma treatment. From the summary in Table 2, we determined that the  $O_2$  plasma time of 60 s possessed the largest on/off current ratio of >10<sup>8</sup>, a  $\mu_{FE}$  of 8.14 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and the lowest S.S. slope of 0.395 V/decade and a  $V_{th}$  of -0.14 V. However, increases in I<sub>off</sub> and S.S. and degradation in  $\mu_{FE}$  were observed at the longer O<sub>2</sub> plasma time of 120 s. It is reasonable to ascribe higher Ioff and S.S. deterioration to the higher surface roughness of the a-IGZO films after an O2 plasma time of 120 s, as shown in Figure 2. The effects of the various O2 plasma times and O<sub>2</sub> annealing on the hysteresis characteristics are discussed below.

**Figure 3.**  $I_{DS}$ - $V_{GS}$  transfer characteristics and  $I_{GS}$ - $V_{GS}$  of IGZO TFTs with O<sub>2</sub> plasma times of 0, 60, and 120 s.

Table 2. Electrical parameters extracted from the IGZO TFTs at various O<sub>2</sub> plasma times.

| O <sub>2</sub> Plasma Time (s) | $V_{th}$ (V)   | S.S. (V/Decade) | $\mu_{FE}$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | I <sub>on</sub> (A) | I <sub>off</sub> (A) | $ ho_{2.5V}$ (Ω·cm) |

|--------------------------------|----------------|-----------------|---------------------------------------------------------------|---------------------|----------------------|---------------------|

| 0                              | $-5.74\pm0.31$ | $1.045\pm0.036$ | $1.95\pm0.31$                                                 | $2.4	imes10^{-6}$   | $3.0 	imes 10^{-14}$ | 6.26                |

| 60                             | $-0.14\pm0.08$ | $0.395\pm0.031$ | $8.14\pm0.86$                                                 | $1.3	imes10^{-6}$   | $1.1 	imes 10^{-14}$ | 7.64                |

| 120                            | $5.14\pm0.51$  | $2.210\pm0.204$ | $2.98\pm0.31$                                                 | $1.3	imes10^{-6}$   | $4.4	imes10^{-12}$   | 8.26                |

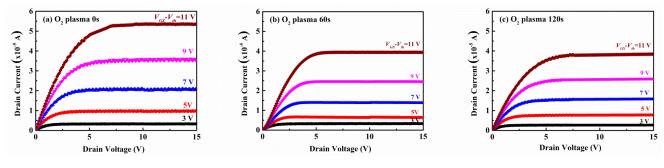

Figure 4 shows the typical output characteristics of the IGZO TFTs at various  $O_2$  plasma times under different gate overdrives:  $V_{GS}$ - $V_{th}$  = 3–11 V. It can be seen that the saturation current at the same gate overdrive clearly decreased as the  $O_2$  plasma time increased. All of the devices demonstrated ohmic behavior, indicating good contact between the a-IGZO channels and Mo electrodes. In a linear current model of a conventional metal oxide semiconductor field-effect transistor (MOSFET), the resistivity ( $\rho$ ) is expressed by the following equation [16,20]:

$$\rho = \frac{V_{DS}}{I_{DS}} \frac{Wt}{L} \approx \frac{1}{\mu_{FE} C_{ox} (V_{GS} - V_{th})} \approx \frac{1}{nq\mu_{FE}}$$

(2)

where  $C_{ox}$  is the oxide capacitance per unit area; *n* is the charge carrier concentration (cm<sup>-3</sup>); *q* is the electron unit charge; *W*, *L*, and *t* are the width, length, and thickness of the channel, respectively; and  $V_{DS}$  is the drain-source voltage. It should be noted that  $\rho$  is primarily associated with  $V_{th}$ , and its corresponding *n* is determined according to Equation (2). Table 2 indicates that  $\rho$  gradually increased from 6.26 to 8.26  $\Omega$ ·cm as the O<sub>2</sub> plasma treatment time increased at  $V_{DS} = 2.5$  V and  $V_{GS}$ - $V_{th} = 11$  V. Accordingly, the O<sub>2</sub> plasma treatment mainly affected the changes in *n* in the channel, and *n* was reduced by exposure to the O<sub>2</sub> plasma since it has already been demonstrated that oxygen atoms can fill oxygen vacancies after O<sub>2</sub> treatments in metal oxide-based semiconductors [15,16,21]. In addition, it is clearly confirmed in Figure 3 that the transfer curves shifted positively as the O<sub>2</sub> plasma time increased. Details of the changes in the carrier concentrations are presented in a later section and are based on the results of the XPS analysis.

Figure 4. Output characteristics  $I_{DS}$ - $V_{DS}$  of IGZO TFTs at O<sub>2</sub> plasma times of (a) 0, (b) 60, and (c) 120 s.

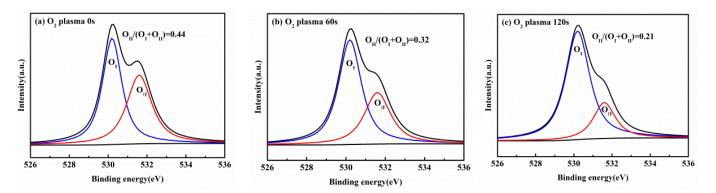

The chemical characteristics of the a-IGZO channel layers treated with different O2 plasma times were investigted by analyzing the XPS results. The effect of the O<sub>2</sub> plasma time on oxygen scarcity after plasma processing was studied extensively by compaing and analyzing from the O1s XPS data displayed in Figure 5. Figure 5a–c shows the XPS spectra of the O1s peak of the a-IGZO films with the O<sub>2</sub> plasma times of 0, 60, and 120 s, respectively. Generally, for IGZO TFTs, the O1s spectra are composed of double Gaussian distributions, the  $O_{I}$  peak is observed at 530.2 eV and the  $O_{II}$  peak is observed 531.6 eV [15,16,22,23]. The O<sub>I</sub> XPS signal peak shows covalent oxygen ion bonds with In, Ga, and Zn cations: and the  $O_{II}$  XPS signal peak represents oxygen scarcities in the IGZO film. As a result, the integrated peak ratio of the  $O_{II}/(O_I+O_{II})$  intensity ratio of the O1s core levels of the a-IGZO channel layer was employed to estimate the quality of the channel layer and the number of oxygen scarcities in the a-IGZO channel layer with  $O_2$  plasma treatment. The estimated XPS  $O_{II}/(O_I+O_{II})$  intensity ratios for the a-IGZO channel layer with increased  $O_2$  plasma times of 0, 60, and 120 s were 0.44, 0.32, and 0.21, respectively. When O<sub>2</sub> plasma treatment was performed for a longer time, the low  $O_{II}/(O_I + O_{II})$  XPS intensity ratios indicated a significant reduction in the oxygen scarcities and greater quality of the IGZO channel layer. Because oxygen vacancies are important for electron donation in the a-IGZO channel layer, the decreased O<sub>II</sub> peak intensity shown in the XPS analyses corresponded well with the reduced carrier concentration, which could be ascribed to a higher resistivity as a result of the increased O<sub>2</sub> plasma time, as shown in Table 2. Therefore, as the O<sub>2</sub> plasma time increased, the reduced carrier concentration in the IGZO channel layer may have resulted in an increase in the threshold voltage  $(V_{th})$  of the IGZO TFT devices [13,17,24].

**Figure 5.** XPS spectra of a-IGZO thin films at the  $O_2$  plasma times of (a) 0, (b) 60, and (c) 120 s.

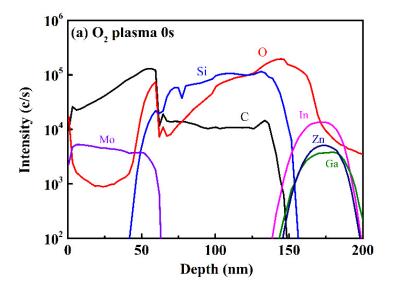

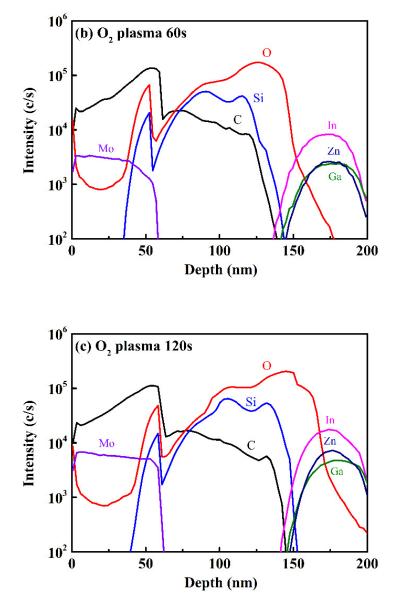

For the analysis of the SIMS depth profile results, we fabricated test samples with a 50 nm thick Mo/100 nm thick TEOS oxide/40 nm thick a-IGZO structure on silicon substrates that were the same as the structure of the top-gate IGZO TFT devices. First, the a-IGZO film was deposited on the silicon substrate, and then, it was subjected to  $O_2$  plasma treatment on the a-IGZO film prior to the depositing of the TEOS oxide and  $O_2$  annealing after TEOS oxide deposition in the same PECVD system. The SIMS analysis is able to observe information on the impurity content and compositions of the TEOS oxide interface with a-IGZO films treated with O<sub>2</sub> plasma. The area located 100–150 nm from the sample's surface was found to be related to the area across the TEOS oxide near the a-IGZO films. Figure 6a-c shows the SIMS depth profiles of the Mo, Si, O, C, In, Ga, and Zn elements for the test samples at various  $O_2$  plasma times. From analyzing the element intensities, we found that the ratios of the elements Mo, In, Ga, and Zn remained essentially unchangeable for these three samples. Figure  $_{6a}$  shows that the TEOS oxide film on the sample without  $O_2$  plasma treatment contained more carbon (3.91%) than the others. Because the TEOS oxide film reaction provided intermediate elements, such as the carbon impurity in the film caused by the inadequate dissociation of TEOS oxide, the carbon dissociation inside the TEOS oxide films of the O<sub>2</sub> plasma-treated samples was enhanced. With the increased O<sub>2</sub> plasma times of 60 and 120 s, the ratio of the carbon content in the TEOS oxide film decreased from 3.91% to the ratios of 2.42% and 2.71%, respectively, as shown in Figure 6a-c. Rhee et al. reported that the use of oxygen gas plasma treatment during TEOS oxide gate dielectric deposition was efficient in removing the impurities and in the densification of the film. The carbon impurity was reduced by cyclic  $O_2$  plasma treatment [25]. Since TEOS oxide is affected by O<sub>2</sub> plasma treatment, the Si and O contents of the TEOS oxide film clearly changed as the  $O_2$  plasma time increased. The O/Si ratios of TEOS oxide gradually increased from 1.15 to the ratios of 2.64 and 3.54 with increased  $O_2$  plasma times of 60 and 120 s, respectively, as shown in Table 3. This is because the impurities on the surface of the a-IGZO channel layer were mainly removed after O<sub>2</sub> plasma time of 60 s and because the low amount of  $O_2^+$  in the plasma has a tendency to catch electrons from shallow areas [15]. Therefore, applying the O<sub>2</sub> plasma treatment before gate dielectric deposition would affect the composition of the gate dielectric. In addition, increasing the  $O_2$  plasma time to 120 s may allow the  $O_2^+$  accumulating on the surface to provide more oxygen atoms for TEOS gate dielectrics. In this experiment, we observed that the O/Si ratio of TEOS oxide of the sample with the  $O_2$  plasma time of 60 s was 2.64, and its IGZO TFT device had the best electrical characteristics.

Figure 6. Cont.

**Figure 6.** SIMS depth profiles for Si, O, and C of the test samples at the O<sub>2</sub> plasma times of (**a**) 0, (**b**) 60, and (**c**) 120 s with O<sub>2</sub> annealing.

**Table 3.** SIMS analytical results for the Si, O, C, and O/Si ratio of the test samples at various  $O_2$  plasma times.

| O <sub>2</sub> Plasma Time (s) | Si (%) | O (%) | C (%) | O/Si |

|--------------------------------|--------|-------|-------|------|

| 0                              | 44.66  | 51.41 | 3.91  | 1.15 |

| 60                             | 26.77  | 70.80 | 2.42  | 2.64 |

| 120                            | 21.40  | 75.88 | 2.71  | 3.54 |

Because the conduction channel layer is mainly formed in a very thin layer near the interface, the electrical properties of a TFT are determined by the interface roughness between the a-IGZO and the TEOS oxide gate dielectric. The existence of defect states that may lead to electron trapping primarily affects the S.S. and  $\mu_{FE}$  of the a-IGZO channel layer [26,27].

For the sample with an  $O_2$  plasma time 60 s, a slight increase in the surface roughness of the a-IGZO channel layer was observed based on the AFM morphology, but the impurities on the surface of the a-IGZO channel layer were largely removed. In this case, the reaction

of atomic oxygen and oxygen vacancies in the channel layer increased the  $\mu_{FE}$  of the IGZO TFTs. Reductions in the oxygen vacancies and carbon content by the XPS and SIMS analyses, respectively, were observed. It has been reported that filling oxygen vacancies can enhance  $\mu_{FE}$  because interface traps can act as scattering centers [28]. Similarly, the interfacial roughness of the sample with an O<sub>2</sub> plasma time of 120 s increased three times, leading to enhanced carrier scattering and thus reduced fieled effect mobility. In addition, the accumulation of O<sub>2</sub><sup>+</sup> on the surface might clog the micropores and prevent the atoms from reaching deep into the channel layer as the O<sub>2</sub> plasma time increases, resulting in large interfacial traps and degraded S.S. [15].

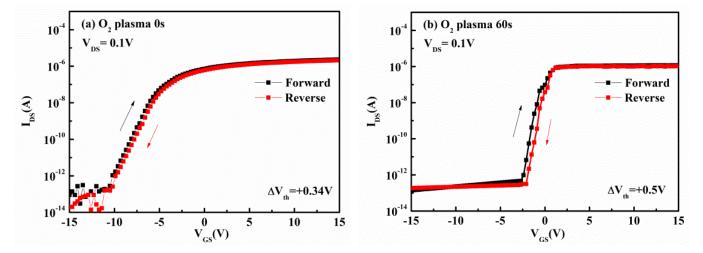

# 3.3. Effect of O<sub>2</sub> Annealing on Hysteresis Characteristics of IGZO TFTs at Various O<sub>2</sub> Plasma Times

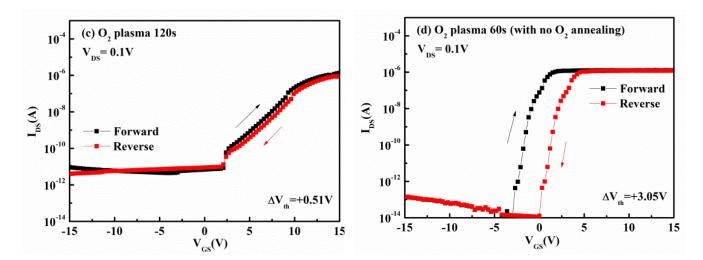

We investigated the hysteresis sweeps of the IGZO TFTs at various  $O_2$  plasma times prior to TEOS oxide deposition, thus studying the impacts of O<sub>2</sub> annealing following TEOS oxide deposition and their interaction with the a-IGZO channel layer. Figure 7a-c shows the hysteresis curves of the IGZO TFTs at the O<sub>2</sub> plasma times of 0, 60, and 120 s, respectively, with O<sub>2</sub> annealing being represented as  $V_{GS}$  ranging from -15 V to +15 V. The hysteresis curve of the IGZO TFT with the O<sub>2</sub> plasma time of 60 s without O<sub>2</sub> annealing and represented as  $V_{GS}$  ranging from -15 V to +15 V is shown in comparison with the effect of  $O_2$  annealing in Figure 7d. Figure 7 shows that the on-current appeared to be rather constant in the saturation region due to a compliance cut-off phenomenon, which was attributed to a higher total resistance between the source and drain electrodes after the  $O_2$  plasma treatment. In the lower threshold voltage shifts ( $\Delta V_{th} = 0.34, 0.5, \text{ and } 0.51 \text{ V}$ ) estimated from the individual hysteresis curves shown in Figure 7a-c with O<sub>2</sub> annealing after TEOS oxide deposition, a small number of electrons were trapped at or close to the interface of the TEOS oxide/a-IGZO channel layer [19]. The largest threshold voltage shift  $(\Delta V_{th} = 3.05 \text{ V})$  from the hysteresis curve without O<sub>2</sub> annealing revealed that a greater number of electrons were trapped at the interface between TEOS oxide and the a-IGZO channel layer. However, the lower  $\Delta V_{th}$  from the hysteresis curves displayed in Figure 7a–c shows that O<sub>2</sub> annealing after TEOS oxide deposition successfully limited the formation in interface traps and charge trapping between the TEOS oxide gate dielectrics and the IGZO channel layer. It has been already shown that the a-IGZO channel regions were patterned and thermally annealed in the  $O_2$  atmosphere or in air, and the hysteresis disappeared for the annealed bottom-gate IGZO TFTs, which suggests that thermal annealing reduces electron traps [29,30].

**Figure 7.** Hysteresis curves of IGZO TFTs at the  $O_2$  plasma times of (**a**) 0, (**b**) 60, and (**c**) 120 s; (**d**)  $O_2$  plasma time of 60 s, without  $O_2$  annealing.

## 4. Conclusions

In this study, O<sub>2</sub> plasma treatment was found to increase the surface roughness of the IGZO channel layer. The O<sub>2</sub> plasma time of 60 s possessed the largest on/off current ratio of >10<sup>8</sup>, with a  $\mu_{FE}$  of 8.14 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and the lowest S.S. slope of 0.395 V/decade, with a  $V_{th}$ of -0.14 V. However, increases in I<sub>off</sub> and S.S. and degradation in  $\mu_{FE}$  were observed for the longer O2 plasma time of 120 s. It is reasonable to ascribe the higher Ioff and deteriorated S.S. to the higher surface roughness of the a-IGZO channel layer for a longer O<sub>2</sub> plasma time of 120 s. The XPS observations of the  $O_{II}$  peak intensity coincided well with the lower carrier concentration due to larger resistivity with the increasing  $O_2$  plasma time. Therefore, the decrease in the carrier concentration of the IGZO channel layer may lead to an increase in  $V_{th}$  of the IGZO TFT device with the increasing O<sub>2</sub> plasma time. As the O<sub>2</sub> plasma time increased, the carbon content in the TEOS oxide film was reduced, and the film stoichiometry was improved. From the SIMS depth profile results, we found that the O/Si ratio of the TEOS oxide for the sample with the  $O_2$  plasma time of 60 s was 2.64, and its IGZO TFT device had the best electrical characteristics. In addition, compared to the IGZO TFT device without  $O_2$  annealing, more electrons were trapped at the interface between the TEOS oxide and the a-IGZO channel layer, as shown by a significant clockwise hysteresis in the transfer characteristics. However, the hysteresis curves of the O<sub>2</sub>-annealed IGZO TFTs with various  $O_2$  plasma times were greatly diminished, meaning that the electron traps were reduced by O<sub>2</sub> annealing.

Author Contributions: Conceptualization, T.-C.T., Y.-S.L. and T.-E.H.; methodology, T.-C.T. and Y.-S.L.; software, T.-C.T.; data curation, Y.-H.W.; writing—original draft preparation, Y.-S.L. and T.-C.T.; writing—review and editing, Y.-S.L., Y.-H.W., T.-C.T., T.-E.H. and M.-L.L. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded by the Ministry of Science Technology Project (MOST 110-2637-E-159-004-).

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

**Data Availability Statement:** The data presented in this study are available on request from the corresponding author.

Acknowledgments: The authors thank the National Yang Ming Chiao Tung University Nano Facility Center (NFC) for supplying the RF Magnetron Sputter and ICP systems and the Taiwan Semiconductor Research Institute (TSRI) for supplying the PECVD system.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Baek, G.; Bie, L.; Abe, K.; Kumomi, H.; Kanicki, J. Electrical Instability of Double-Gate a-IGZO TFTs With Metal Source/Drain Recessed Electrodes. *IEEE Trans. Electron Devices* **2014**, *61*, 1109–1115. [CrossRef]

- Cao, Q.; Kim, H.S.; Pimparkar, N.; Kulkarni, J.P.; Wang, C.; Shim, M.; Roy, K.; Alam, M.A.; Rogers, J.A. Medium-scale carbon nanotube thin-film integrated circuits on flexible plastic substrates. *Nature* 2008, 454, 495–500. [CrossRef] [PubMed]

- 3. Lin, C.-L.; Chang, W.-Y.; Hung, C.-C. Compensating Pixel Circuit Driving AMOLED Display With a-IGZO TFTs. *IEEE Electron Device Lett.* **2013**, 34, 1166–1168. [CrossRef]

- 4. Seok, M.J.; Choi, M.H.; Mativenga, M.; Geng, D.; Kim, D.Y.; Jang, J. A Full-Swing a-IGZO TFT-Based Inverter with a Top-Gate-Bias-Induced Depletion Load. *IEEE Electron Device Lett.* **2011**, *32*, 1089–1091. [CrossRef]

- Kang, D.H.; Kang, I.; Ryu, S.H.; Jang, J. Self-Aligned Coplanar a-IGZO TFTs and Application to High-Speed Circuits. *IEEE Electron Device Lett.* 2011, 32, 1385–1387. [CrossRef]

- Arias, A.C.; MacKenzie, J.D.; McCulloch, I.; Rivnay, J.; Salleo, A. Materials and applications for large area electronics: Solutionbased approaches. *Chem. Rev.* 2010, 110, 3–24. [CrossRef] [PubMed]

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. *Nature* 2004, 432, 488–492. [CrossRef]

- 8. Hosono, H. Ionic amorphous oxide semiconductors: Material design, carrier transport, and device application. *J. Non-Cryst. Solids* **2006**, 352, 851–858. [CrossRef]

- 9. Lee, Y.-S.; Yen, T.-W.; Lin, C.-I.; Lin, H.-C.; Yeh, Y. Electrical characteristics of amorphous In–Ga–Zn–O thin-film transistors prepared by radio frequency magnetron sputtering with varying oxygen flows. *Displays* **2014**, *35*, 165–170. [CrossRef]

- Lee, Y.-S.; Fan, S.-K.; Chen, C.-W.; Yen, T.-W.; Lin, H.-C. Temperature instability of amorphous In-Ga-Zn-O thin film transistors. In Proceedings of the 2013 6th IEEE/International Conference on Advanced Infocomm Technology (ICAIT), Hsinchu, Taiwan, 6–9 July 2013.

- 11. Park, J.; Song, I.; Kim, S.; Kim, S.; Kim, C.; Lee, J.; Lee, H.; Lee, E.; Yin, H.; Kim, K.-K.; et al. Self-aligned top-gate amorphous gallium indium zinc oxide thin film transistors. *Appl. Phys. Lett.* **2008**, *93*, 53501. [CrossRef]

- Chen, R.; Zhou, W.; Zhang, M.; Wong, M.; Kwok, H.S. Self-aligned top-gate InGaZnO thin film transistors using SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stack gate dielectric. *Thin. Solid Film.* 2013, 548, 572–575. [CrossRef]

- 13. Ahn, J.S.; Lee, K.B. Control of the threshold voltage by using the oxygen partial pressure in sputter-deposited InGaZnO<sub>4</sub> thin-film transistors. *J. Korean Phys. Soc.* **2012**, *60*, 1625–1628. [CrossRef]

- 14. Jeong, J.K. The status and perspectives of metal oxide thin-film transistors for active matrix flexible displays. *Semicond. Sci. Technol.* **2011**, *26*, 34008. [CrossRef]

- 15. Pu, H.; Zhou, Q.; Yue, L.; Zhang, Q. Investigation of oxygen plasma treatment on the device performance of solution-processed a-IGZO thin film transistors. *Appl. Surf. Sci.* 2013, 283, 722–726. [CrossRef]

- Kim, J.-S.; Joo, M.-K.; Xing Piao, M.; Ahn, S.-E.; Choi, Y.-H.; Jang, H.-K.; Kim, G.-T. Plasma treatment effect on charge carrier concentrations and surface traps in a-InGaZnO thin-film transistors. J. Appl. Phys. 2014, 115, 114503. [CrossRef]

- 17. Liu, W.-S.; Hsu, C.-H.; Jiang, Y.; Lai, Y.-C.; Kuo, H.-C. Improvement of device characteristics of plasma-treated indium gallium zinc oxide thin-film transistors through thermal annealing. *Semicond. Sci. Technol.* **2021**, *36*, 45007. [CrossRef]

- 18. Wang, H.; Xu, W.; Zhou, S.; Xie, F.; Xiao, Y.; Ye, L.; Chen, J.; Xu, J. Oxygen plasma assisted high performance solution-processed Al<sub>2</sub>O<sub>x</sub> gate insulator for combustion-processed InGaZnO<sub>x</sub> thin film transistors. *J. Appl. Phys.* **2015**, *117*, 35703. [CrossRef]

- Lee, Y.-S.; Wang, Y.-H.; Tien, T.-C.; Hsieh, T.-E.; Lai, C.-H. Electrical Characteristics and Stability Improvement of Top-Gate In-Ga-Zn-O Thin-Film Transistors with Al<sub>2</sub>O<sub>3</sub>/TEOS Oxide Gate Dielectrics. *Coatings* 2020, 10, 1146. [CrossRef]

- 20. Dimitrijev, S. Principle of Semiconductor Devices, 2nd ed.; Oxford University Press: New York, NY, USA, 2006.

- 21. Park, J.-W.; Baik, H.-K.; Lim, T.; Ju, S. Threshold voltage control of oxide nanowire transistors using nitrogen plasma treatment. *Appl. Phys. Lett.* **2010**, *97*, 203508. [CrossRef]

- 22. Liu, P.; Chen, T.P.; Liu, Z.; Tan, C.S.; Leong, K.C. Effect of O<sub>2</sub> plasma immersion on electrical properties and transistor performance of indium gallium zinc oxide thin films. *Thin Solid Film.* **2013**, *545*, 533–536. [CrossRef]

- Kim, J.; Bang, S.; Lee, S.; Shin, S.; Park, J.; Seo, H.; Jeon, H. A study on H<sub>2</sub> plasma treatment effect on a-IGZO thin film transistor. J. Mater. Res. 2012, 27, 2318–2325. [CrossRef]

- Liu, W.-S.; Hsu, C.-H.; Jiang, Y.; Lai, Y.-C.; Kuo, H.-C. Improving Device Characteristics of Dual-Gate IGZO Thin-Film Transistors with Ar–O<sub>2</sub> Mixed Plasma Treatment and Rapid Thermal Annealing. *Membranes* 2022, 12, 49. [CrossRef]

- 25. Yi, C.; Rhee, S.W. Cyclic plasma deposition of SiO<sub>2</sub> films at low temperature (80 °C) with intermediate plasma treatment. *J. Vac. Sci. Technol. A Vac. Surf. Film.* **2002**, *20*, 398–402. [CrossRef]

- Nomura, K.; Kamiya, T.; Ohta, H.; Hirano, M.; Hosono, H. Defect passivation and homogenization of amorphous oxide thin-film transistor by wet O<sub>2</sub> annealing. *Appl. Phys. Lett.* 2008, *93*, 192107. [CrossRef]

- Chung, W.-F.; Chang, T.-C.; Li, H.-W.; Chen, C.-W.; Chen, Y.-C.; Chen, S.-C.; Tseng, T.-Y.; Tai, Y.-H. Influence of H<sub>2</sub>O Dipole on Subthreshold Swing of Amorphous Indium–Gallium–Zinc-Oxide Thin Film Transistors. *Electrochem. Solid-State Lett.* 2011, 14, H114–H116. [CrossRef]

- Nayak, P.K.; Hedhili, M.N.; Cha, D.; Alshareef, H.N. High performance solution-deposited amorphous indium gallium zinc oxide thin film transistors by oxygen plasma treatment. *Appl. Phys. Lett.* 2012, 100, 202106. [CrossRef]

- 29. Nomura, K.; Kamiya, T.; Kikuchi, Y.; Hirano, M.; Hosono, H. Comprehensive studies on the stabilities of a-In-Ga-Zn-O based thin film transistor by constant current stress. *Thin Solid Film.* **2010**, *518*, 3012–3016. [CrossRef]

- 30. Kimura, M.; Nakanishi, T.; Nomura, K.; Kamiya, T.; Hosono, H. Trap densities in amorphous-InGaZnO<sub>4</sub> thin-film transistors. *Appl. Phys. Lett.* **2008**, *92*, 133512. [CrossRef]