Article

# Design of an Ultra-Low Voltage Bias Current Generator Highly Immune to Electromagnetic Interference †

Orazio Aiello 🗅

Department of Electronics and Computer Engineer, National University of Singapore, Singapore 117583, Singapore; orazio.aiello@nus.edu.sg

† This paper is a revised and extended version of the conference paper Aiello, O. Ultra-Low Voltage Current Biasing Highly Immune to EMI. In Proceedings of the 2019 IEEE International Circuits and Systems Symposium (ICSyS), Kuantan, Malaysia, 18–19 September 2019; pp. 1–4.

**Abstract:** The paper deals with the immunity to Electromagnetic Interference (EMI) of the current source for Ultra-Low-Voltage Integrated Circuits (ICs). Based on the properties of IC building blocks, such as the current-splitter and current correlator, a novel current generator is conceived. The proposed solution is suitable to provide currents to ICs operating in the sub-threshold region even in the presence of an electromagnetic polluted environment. The immunity to EMI of the proposed solution is compared with that of a conventional current mirror and evaluated by analytic means and with reference to the 180 nm CMOS technology process. The analysis highlights how the proposed solution generates currents down to nano-ampere intrinsically robust to the Radio Frequency (RF) interference affecting the input of the current generator, differently to what happens to the output current of a conventional mirror under the same conditions.

**Keywords:** Electromagnetic Interference (EMI); Ultra-Low-Voltage (ULV) ICs; current mirrors; current generators; current-splitter; current correlator

Citation: Aiello, O. Design of an Ultra-Low Voltage Bias Current Generator Highly Immune to Electromagnetic Interference. *J. Low Power Electron. Appl.* **2021**, *11*, 6. https://doi.org/10.3390/jlpea11010006

Received: 13 October 2020 Accepted: 15 January 2021 Published: 20 January 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2021 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

#### 1. Introduction

Ubiquitous electronics systems require low power consumption to reduce the dependence on batteries through energy harvesting techniques [1,2]. Thus, the electronic circuits need to properly operate at an ultra-low supply voltage [3–6]. This reduces the logic threshold and the noise margin accordingly, making the Integrated Circuits (ICs) more vulnerable to Electromagnetic Interference (EMI) [7–17]. Thus, the robustness of Ultra-Low-Voltage (ULV) ICs in any electromagnetic-polluted environment is an even more demanding task to be guaranteed in a safety-critical device where the need for ultra-low power consumption merges with the request of properly operate in any condition [18–20].

ICs for implanted devices can include on-chip bias current generators operating in subthreshold to improve current matching as well as allow easy bias current tuning [21,22]. For this reason, among the basic on-chip requirements, the current generation for ICs operating in sub-threshold in the presence of Radio Frequency Interference (RFI) is addressed in this paper.

To this purpose, the EMI robustness of conventional current mirrors operating in the saturation region is first briefly recalled in Section 2. Then, the properties of specific IC topologies operating in the sub-threshold region are summarized in Section 3. Based on such properties, a new current generator with an EMI immunity higher than those of existing current-mirror based schemes is proposed in Section 4. The respective EMI robustness is discussed and evaluated by means of time-domain computer simulations referring to the 180 nm technology process. The conclusions are finally drawn in Section 6.

# 2. RFI Effect on Current Mirrors

The susceptibility of current mirrors has been investigated, and some solutions to increase their EMI-robustness have been proposed in the literature [23–30]. The typical approach is based on capacitors properly placed to implement a filter and attenuate the EMI [23–28]. Anyhow, all these solutions refer to transistors nominally operating in the saturation region (above threshold).

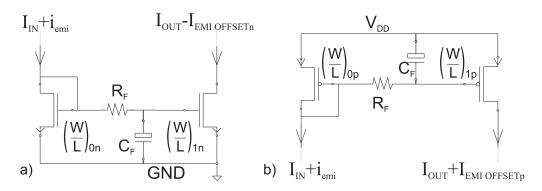

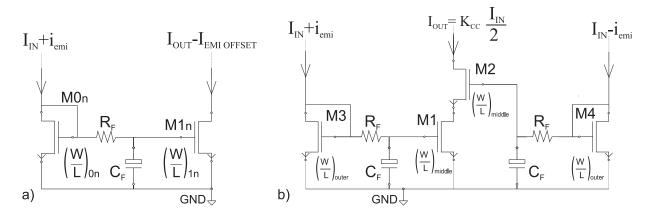

Figure 1 represents the conventional N and P-type current mirrors. The input current  $I_{\rm IN}$  is nominally translated into the output current  $I_{\rm OUT}$  according to the ratio  $K = \frac{\binom{W}{L}_1}{\binom{W}{L}_0}$ . The presence of an EMI current  $i_{\rm emi}$  superimposed on the input current  $I_{\rm IN}$  affects the output current  $I_{\rm OUT}$ . A low-pass filter ( $R_{\rm F}C_{\rm F}$ ) has been placed to highlight the EMI-induced (DC offset) current named  $I_{\rm EMI_{OFFSET_n}}$  and  $I_{\rm EMI_{OFFSET_p}}$  in Figure 1a,b respectively. Notice that along with the paper, the capitalization and lower cases used to name the currents refer to their DC and time-continuous signal values respectively.

Figure 1. N-type (a) and P-type (b) current mirrors.

In the presence of interference, the total current through the first branch of the current mirror can then be modeled as the sum of a Continuous Wave (CW) Radio Frequency (RF) current  $i_{\text{emi}}$  and the proper DC current  $I_{\text{IN}}$ . This results in an output current affected by EMI  $i_{\text{out}_{\text{emi}}}$  for an N-type mirror [28]:

$$i_{\text{out}_{\text{emi}}} = K \left[ I_{\text{IN}} - C_{\text{F}} \sqrt{\frac{1}{\frac{\mu C_{\text{ox}}}{2} \cdot (\frac{W}{L})_0}} \cdot \frac{d}{dt} (\sqrt{I_{\text{IN}} + i_{\text{emi}}}) \right]$$

(1)

where  $K = \frac{\binom{W}{L}_1}{\binom{W}{L}_0}$  is the ratio of the transistors' size,  $\mu$  is the charge-carrier effective mobility, and  $C_{\text{ox}}$  is the gate oxide capacitance per unit area.

Equation (1) shows that for an N-type mirror (P-type mirror), the DC level of the output current is lower (higher) than it should be, owing to the loading of the input node by capacitor  $C_{\rm F}$ . This means that, in turn, the output current  $i_{\rm out_{\rm emi}}$  can be modeled as the sum of the desired DC current  $I_{\rm OUT}$  and a negative (positive) current offset named as  $-I_{\rm EMI-OFFSET_n}$  ( $+I_{\rm EMI-OFFSET_p}$ ) as reported at the output branches of the current mirrors in Figure 1a,b. In other words, Equation (1) can be rewritten as

$$i_{\text{out}_{\text{emi}}} = I_{\text{OUT}} + i_{\text{error}}$$

(2)

where  $I_{\text{OUT}} = K \cdot I_{\text{IN}}$  is the nominal output current with no EMI presence and  $i_{\text{error}}$  represents the effect of the EMI on the output current.

Thus,

$$i_{\text{error}} = i_{\text{emi-induced}} = KC_{\text{F}} \sqrt{\frac{1}{\frac{\mu C_{\text{ox}}}{2} \cdot (\frac{W}{L})_0}} \cdot \frac{d}{dt} (\sqrt{I_{\text{IN}} + i_{\text{emi}}})$$

(3)

which implies an EMI-induced offset on the output current  $I_{\text{EMI-OFFSET}} = |i_{\text{error}}| = |i_{\text{emi-induced}}|$  so that Equation (2) can be rewritten referring to the DC values as:

$$I_{\text{OUT}_{\text{EMI}}} = I_{\text{OUT}} + I_{\text{EMI-OFFSET}} \tag{4}$$

These analytic results are valid under the assumption that in the N-type (P-type) current mirror both the transistors  $M_{\rm n0}$  ( $M_{\rm p0}$ ) and  $M_{\rm n1}$  ( $M_{\rm p1}$ ) operate in the saturation region.

# 3. Ultra-Low-Voltage Current Generators

To reduce the overall power consumption of any System-on-Chip, the trend in reducing the power supply moves towards ICs operating in sub-threshold and thus towards a range of current below micro-amperes. This means that the mirroring ratio *K* could convert currents in the range of micro-amperes into mirrored currents in the nano-amperes range.

To move towards Ultra-Low-Voltage current generators, the properties of transistors operating in sub-threshold [31] are explored to build an IC solution more robust to EMI. For this reason, the properties of the current-splitter [32,33] and the current-correlator [34] are summarized, respectively, in Sections 3.1 and 3.2.

# 3.1. Current-Splitter

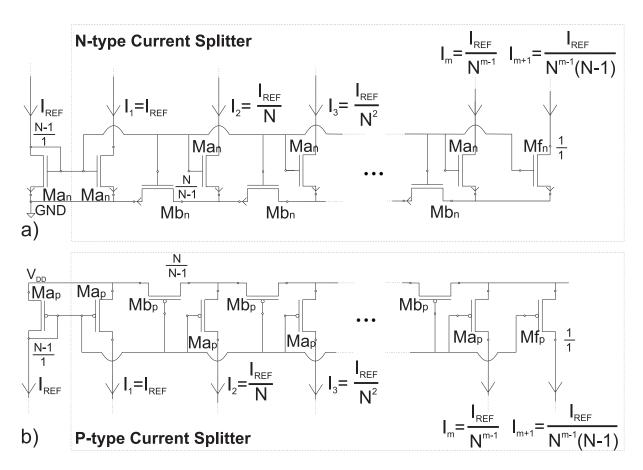

Figure 2 represents N- and P-type current-splitters (Figure 2a,b respectively). Such circuits are capable of providing sourced or sunk currents in the order of nano-amperes or even below through a splitting technique. The size ratio of the transistors Ma, Mb and Mf are  $(W/L)_a = N - 1$ ,  $(W/L)_b = N/(N-1)$  and  $(W/L)_f = 1$  respectively [32]. The current provided by each output branch is progressively divided by a factor N [32]. In other words, the currents provided by each branch comes from a resistive-like partition of the reference current. Indeed, for N = 2 the current-splitter behaves like an M2M ladder network which can be controlled digitally by means of switches to produce any combination of binary-weighted currents. Differently, in the current-splitter, N can be chosen higher than two to rapidly scale down (with the factor N) the reference (input) current  $I_{REF}$ . By lowering the operating currents, both noise and mismatch will remain constant and independent by the current level for the complete weak inversion regime [32].

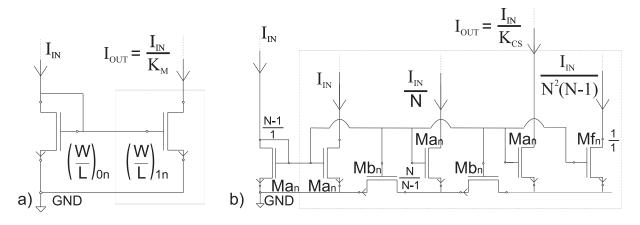

Figure 3 compares how to scale a current  $I_{\text{IN}}$  with a current mirror by a factor  $K_{\text{M}} = \frac{\left(\frac{W}{L}\right)_0}{\left(\frac{W}{L}\right)_1}$  (see Figure 3a) and with a current-splitter by a factor  $K_{\text{CS}} = N^2$  (see Figure 3b). Such a factor is originated by the sum of the N-weighted currents provided by the enabled branches of the current-splitters [32].

Based on these characteristics, the current-splitter perfectly matches the needs of current scaling to bias Ultra-Low-Voltage ICs. In fact, the current-splitter is already used in critical scenarios like neural implants where low power consumption and high reliability are tight constraints [22,35]. This makes further valuable the investigation of ULV current generators robust to EMI.

Referring to Figure 3, assuming  $K_{\rm M} = K_{\rm CS} = N^2 = 100$  and accordingly to the sizing reported in Table 1, the overall area of the proposed solution is  $2.5 \times$  larger than that of the current mirror. Moreover, to properly set the M2M-ladder division, the current  $I_{\rm IN}$  has to be mirrored. This results in doubled overall power consumption. Anyhow, such a current scaling joint with the current correlator properties (in Section 3.2) allows to dramatically increase the EMI robustness of current bias for ICs operating in sub-threshold solution without any additional (external) capacitance as shown in the following.

Figure 2. Schematic of the N-type (a) and P-type (b) current-splitter [32].

**Figure 3.** (a) N-type current mirror with a current scaling  $K_{\rm M} = \frac{\left(\frac{W}{L}\right)_0}{\left(\frac{W}{L}\right)_1}$  and (b) Current-Splitter [32] with a current scaling  $K_{\rm CS} = N^2$ .

| Parameter                                                                                 | Value | Units |

|-------------------------------------------------------------------------------------------|-------|-------|

| $(W/L)_0$                                                                                 | 100/1 | μm/μm |

| $(W/L)_1$                                                                                 | 1/1   | μm/μm |

| $(W/L)_{a_{n,p}}$                                                                         | 9/1   | μm/μm |

| $(W/L)_{b_{n,n}}$                                                                         | 10/9  | μm/μm |

| $(W/L)_{\mathbf{b}_{\mathbf{n},\mathbf{p}}} \ (W/L)_{\mathbf{f}_{\mathbf{n},\mathbf{p}}}$ | 1/1   | μm/μm |

**Table 1.** Sizing of the transistor in Figure 3.

# 3.2. Current Correlator

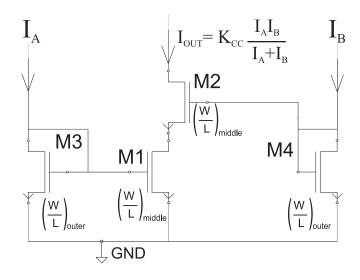

Another valuable circuit topology that operates in the sub-threshold region is the current-correlator shown in Figure 4 [34]. This circuit computes a measure of the correlation between its two input currents named  $I_A$  and  $I_B$ . More precisely, the output current  $I_{OUT}$  is proportional to the product of the two input currents, divided by the sum of the inputs:

$$I_{\text{OUT}} = K_{\text{CC}} \cdot \frac{I_{\text{A}} I_{\text{B}}}{I_{\text{A}} + I_{\text{B}}} \tag{5}$$

where

$$K_{\text{CC}} = \frac{\left(\frac{W}{L}\right)_{middle}}{\left(\frac{W}{L}\right)_{outer}}$$

.

Figure 4. Schematic of a current-correlator [34].

To reduce the overall EMI-induced offset, in this topology  $I_A$  e  $I_B$  are considered to be, respectively, affected by the P- and N-type induced EMI offset:

$$I_{A} = I_{IN} + I_{EMI_{OFFSETp}}$$

$$I_{B} = I_{IN} - I_{EMI_{OFFSETp}}$$

(6)

Assuming  $I_{\rm EMI_{OFFSETp}} \approx I_{\rm EMI_{OFFSETn}} = I_{\rm EMI_{OFFSET}}$ , Equation (5) can be rewritten as:

$$I_{\rm OUT_{\rm emi}} \approx K_{\rm CC} \left( \frac{I_{\rm IN}}{2} - \frac{I_{\rm EMI_{\rm OFFSET}}^2}{2I_{\rm IN}} \right)$$

(7)

The effect of the two different EMI offset contributions at the two input branches is compensated so that:

$$I_{\text{OUT}_{\text{emi}}} \approx I_{\text{OUT}} - K_{\text{CC}} \cdot \left(\frac{I_{\text{EMI}_{\text{OFFSET}}}^2}{2I_{\text{IN}}}\right) = I_{\text{OUT}} - I_{\text{ERROR}}$$

(8)

where

$$I_{\text{ERROR}} = K_{\text{CC}} \cdot \left( \frac{I_{\text{EMI}_{\text{OFFSET}}}^2}{2I_{\text{IN}}} \right)$$

(9)

Comparing Equations (9) with Equation (3), it can be noticed that the overall EMI-induced offset error  $I_{\text{ERROR}}$  is now much attenuated. In fact, in the practical case  $I_{\text{EMI}_{\text{OFFSET}}}^2 \ll I_{\text{IN}}$  so  $I_{\text{EMI}}^2$

that the error factor  $K_{CC} \cdot \frac{I_{\rm EMI_{OFFSET}}^2}{2I_{\rm IN}}$  is negligible and the output current is not strongly affected by the EMI:

$$I_{\rm OUT_{\rm emi}} \approx K_{\rm CC} \cdot \frac{I_{\rm IN}}{2} = I_{\rm OUT}$$

(10)

Figure 5 represents how an EMI current  $i_{\rm emi}$  generates an EMI-induced offset  $I_{\rm EMI_{OFFSET}}$  on a conventional current mirror while EMI currents superimposed with the opposite sign to the two branches of a current correlator do not affect its output current  $I_{\rm OUT}$ .

Notice that even if the EMI-induced offset currents  $I_{\rm EMI_{OFFSETp}}$  and  $I_{\rm EMI_{OFFSETn}}$  superimposed on the nominal current  $I_{\rm IN}$  of the two input branches of the current correlator with opposite signs (as in Equation (6)) are not equal in amplitude ( $I_{\rm EMI_{OFFSETp}} \neq I_{\rm EMI_{OFFSETn}}$ ) but in the same order of magnitude, the interference effect on the output current  $I_{\rm OUT}$  is attenuated.

This characteristic will be exploited in the newly proposed solution and validated by means of simulation in Section 4.

**Figure 5.** (a) N-type current mirror with N-type Electromagnetic Interference (EMI)-induced offset (negative offset current  $I_{\text{EMI}_{\text{OFFSET}n}}$ ) and (b) current-correlator [34] with opposite EMI-induced offset as input currents.

#### 4. A New Current Generator Robust to EMI

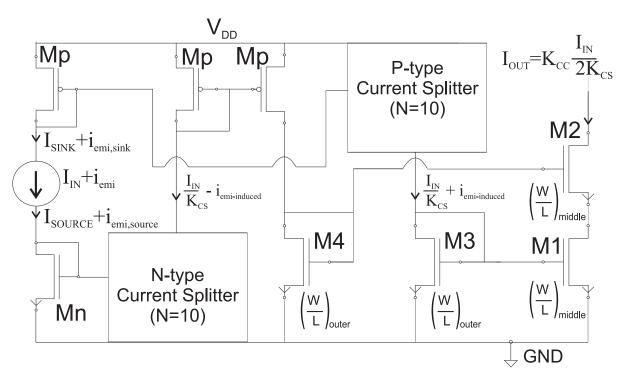

The above-described circuit topologies operating in sub-threshold are employed as building blocks of a new current biasing circuit sketched in Figure 6 in which the input current to be mirrored and scaled is affected by EMI.

The input current  $I_{\rm IN}$  represents both the independent sourced ( $I_{\rm SOURCE}$ ) and sunk ( $I_{\rm SINK}$ ) currents ( $I_{\rm SOURCE} = I_{\rm SINK} = I_{\rm IN}$ ) that come from reference currents (not reported in Figure 6. These reference currents are usually implemented using a voltage regulator and an operational amplifier to produce a current from the feedback of a small series resistance [36]. To not introduce any error, these building blocks should be designed according to the existing design guidelines to avoid any EMI-induced offset at their outputs [37–40]. In this way, the proper input DC current  $I_{\rm IN}$  can be provided even if still affected by a superimposed

EMI current  $i_{\rm emi}$ . Thus, for sake of simplicity and focusing on the current generator only,  $I_{\rm IN} = I_{\rm SOURCE} = I_{\rm SINK}$  is considered. The same assumption is applied for the respective superimposed EMI currents ( $i_{\rm emi} = i_{\rm emi,source} = i_{\rm emi,sink}$ ). Notice that the minimum difference in the inputs branches currents ( $I_{\rm SOURCE}$  and  $I_{\rm SINK}$ ) and in the respective superimposed EMI currents ( $i_{\rm emi,source}$  and  $i_{\rm emi,sink}$ ) do not affect the mathematical definition of the output current  $I_{\rm OUT}$  much.

The input current  $I_{\rm IN}$  is scaled down by a ratio factor  $K_{\rm CS}$  through both P and N-type current-splitters. The presence of complementary current-splitters in the circuit in Figure 6 allows to rapidly scale the input current and benefit from the EMI-induced offset compensation based on an N-P offset compensation [40], which is performed through the current-correlator. The scaled currents coming from a P and N-type current-splitters flow to the respective current correlator that balances the opposite offset trend according to Equation (7). Assuming the aspect ratio of the current-correlator is equal to  $K_{\rm CC}=2$ :

$$I_{\text{OUT}} \approx K_{\text{CC}} \frac{I_{\text{IN}}}{2K_{\text{CS}}} = \frac{I_{\text{IN}}}{K_{\text{CS}}}$$

(11)

On this basis, the circuit in Figure 6 performs a current mirror-like function suitable for ICs operating in the nano-ampere range and highly immune to EMI.

Figure 6. Schematic of the proposed current generator operating in the subthreshold region and robust to EMI.

**Table 2.** Sizing of the transistor employed in the new current bias method proposed in Figure 6.

| Parameter                                    | Value | Units |

|----------------------------------------------|-------|-------|

| $(W/L)_{a_{n,p}}$                            | 9/1   | μm/μm |

| $(W/L)_{\mathbf{b}_{\mathbf{n},\mathbf{p}}}$ | 10/9  | μm/μm |

| $(W/L)_{f_{n,p}}$                            | 1/1   | μm/μm |

| $(W/L)_{\text{middle}}$                      | 10/1  | μm/μm |

| $(W/L)_{\text{outer}}$                       | 10/1  | μm/μm |

| $(W/L)_n$                                    | 10/1  | μm/μm |

| $(W/L)_{p}$                                  | 10/1  | μm/μm |

# 5. Validation and Comparison

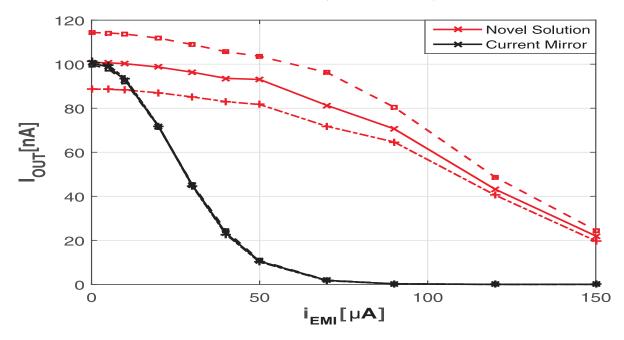

To verify the EMI robustness of the proposed circuit solution, time-domain simulations have been performed with reference to the 180 nm CMOS technology. Analyses have been carried out referring to a traditional current mirror in Figure 5a and the proposed solution in Figure 6. For both these current bias methods, the output current  $I_{\rm OUT}=100$  nA originates from an input current  $I_{\rm IN}=10$  µA affected by a CW RF current  $i_{\rm emi}$ . It means that  $K_{\rm M}=K_{\rm CS}=100$ . Thus, both the P- and N-type current-splitters divide the input current twice by a factor N = 10. Table 2 reports the transistors' size for both the current-splitters and current correlator presented in Figure 6. On this basis, the overall area results to be  $5\times$  larger than that of a conventional current mirror with the same scaling factor.

The interference current  $i_{\rm emi}$  is superimposed on the input current  $I_{\rm IN}$  and the DC offset on the output current  $I_{\rm OUT}$  is evaluated similarly to immunity tests [41]. Every simulation result refers to the average value assumed by the output current in steady-state conditions when the offset becomes constant and while the input is affected by a CW EMI. In addition, process corner variations have also been reported: ss (dashed) and ff (dotted-dashed) line. Such variations could vary the DC nominal output current  $I_{\rm OUT}$  up to 10% in the proposed solution but not its EMI robustness. Thus, if a precise output current value is needed, it can be reached through calibration keeping the EMI robustness capability.

In Figure 7 the EMI-induced offset on the current  $I_{\rm OUT}=100$  nA versus the amplitude of the interference  $i_{\rm emi}$  at 100 MHz is reported. A relevant gap between the two EMI-induced offsets on the output current can be highlighted. The newly proposed solution represented in Figure 6 shows an error on the output current below 5% for a CW RF interference current  $i_{\rm emi}$  equal to 50  $\mu$ A. In the same condition, the conventional current mirror exhibits an error of 90% (from 100 to 10 nA).

Figure 7. Output current  $I_{\text{OUT}}$  due to an input current  $I_{\text{IN}} = 10 \,\mu\text{A}$  with a superimposed Continuous Wave (CW) Radio Frequency (RF) current  $i_{\text{emi}}$  in an N-type current mirror ( $K_{\text{M}} = 100$  in Figure 5a) and in the proposed solution ( $K_{\text{CS}} = 100$  in Figure 6). Process corner: ss (dashed) and ff (dotted-dashed) line.  $I_{\text{OUT}}$  versus  $i_{\text{emi}}$  amplitude ( $i_{\text{emi}} @ 100 \, \text{MHz}$ ).

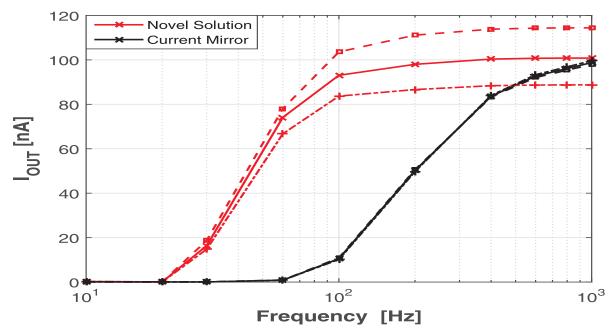

Similarly, the amplitude of the interference is kept constant and equal to  $i_{\rm emi}=50~\mu A$  while its frequency is swept in the RF range in Figure 8. The proposed current generator shows higher robustness to EMI in a larger RF range.

**Figure 8.** Output current  $I_{OUT}$  due to an input current  $I_{IN} = 10 \, \mu A$  with a superimposed CW RF current  $i_{emi}$  in an N-type current mirror ( $K_M = 100$  in Figure 5a) and in the proposed solution ( $K_{CS} = 100$  in Figure 6). Process corner: ss (dashed) and ff (dotted-dashed) line.  $I_{OUT}$  versus  $i_{emi}$  frequency ( $i_{emi} = 50 \, \mu A$ ).

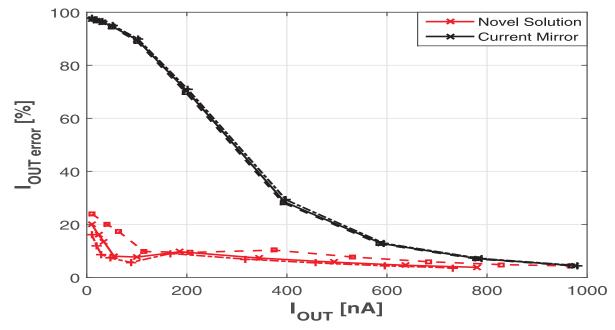

Figure 9 represents the percentage variations of the output current ( $I_{\rm OUT_{error}} = \frac{I_{\rm OUT} - I_{\rm OUT_{emi}}}{I_{\rm OUT}}$  ·100) due to the interference  $i_{\rm emi}$  versus the value of the DC value itself  $I_{\rm OUT}$  with no EMI presence. The sweep in the  $I_{\rm OUT}$  has been obtained simply changing the input DC current  $I_{\rm IN}$  and keeping the CW RF interference  $i_{\rm emi}$  at 100 MHz, the same frequency of the amplitude sweep in Figure 7 and with the same amplitude of the frequency sweep in Figure 8 ( $i_{\rm emi} = 50~\mu{\rm A}$ ). The lower the output current  $I_{\rm OUT}$  to obtain, the higher the effectiveness of the proposed method in providing a current robust to EMI.

**Figure 9.** Percentage error  $I_{\text{OUT}_{\text{error}}}$  due to a CW RF current  $i_{\text{emi}}$  superimposed on a variable input current  $I_{\text{IN}}$  in an N-type current mirror ( $K_{\text{M}} = 100$  in Figure 5a) and in the proposed solution ( $K_{\text{CS}} = 100$  in Figure 6). Process corner: ss (dashed) and ff (dotted-dashed) line.  $I_{\text{OUT}_{\text{error}}}$  versus  $I_{\text{OUT}}$  for  $i_{\text{emi}} = 50~\mu\text{A}$  @ 100 MHz.

# 6. Conclusions

In this work, a new integrated method suitable to provide currents for ICs operating in sub-threshold and robust to EMI has been discussed. The EMI-induced offset on the output current of a conventional current mirror is first considered. Then, based on ICs building blocks operating in sub-threshold, a new current generator for ULV ICs has been proposed. Such an IC solution exploits the N-P offset compensation and the properties of the current-correlator to strongly attenuate the EMI-induced offset on the output current.

The mathematical results as well as the time domain simulations show that for different conditions of frequency and amplitude of the EMI, the newly proposed solution to generate currents for ICs operating in sub-threshold is highly immune to EMI and much more robust than conventional current mirrors. This is at the cost of  $4\times$  higher overall current consumption ( $2\times$  for each current-splitter) and  $5\times$  larger area compared to the conventional current mirroring.

Funding: This research received no external funding.

Institutional Review Board Statement: Not applicable.

**Informed Consent Statement:** Not applicable.

**Acknowledgments:** The author would like to thank the anonymous reviewers for their valuable suggestions.

Conflicts of Interest: The author declares no conflict of interest.

### **Abbreviations**

The following abbreviations are used in this manuscript:

EMI Electromagnetic Interference

ICs Integrated Circuits

CMOS Complementary Metal-Oxide-Semiconductor

RF Radio Frequency

RFI Radio Frequency Interference

ULV Ultr-Low Voltage CW Continuous Wave

#### References

- Aiello, O.; Crovetti, P.S.; Alioto, M. A Sub-Leakage pW-Power Hz-Range Relaxation Oscillator Operating with 0.3 V-1.8 V Unregulated Supply. In Proceedings of the IEEE 2018 Symposia on VLSI Circuits (VLSI 2018), Honolulu, HI, USA, 18–22 June 2018; pp. 119–120.

- Aiello, O.; Crovetti, P.S.; Alioto, M. Wake-Up Oscillators with pW Power Consumption in Dynamic Leakage Suppression Logic. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–5.

- 3. Richelli, A.; Colalongo, L.; Kovacs-Vajna, Z.; Calvetti, G.; Ferrari, D.; Finanzini, M.; Pinetti, S.; Prevosti, E.; Savoldelli, J.; Scarlassara, S. A Survey of Low Voltage and Low Power Amplifier Topologies. *J. Low Power Electron. Appl.* **2018**, *8*, 22. [CrossRef]

- 4. Aiello, O.; Crovetti, P.S.; Alioto, M. Fully synthesizable low-area analogue-to-digital converters with minimal design effort based on the dyadic digital pulse modulation. *IEEE Access* **2020**, *8*, 70890–70899. . [CrossRef]

- 5. Rodovalho, L.H.; Aiello, O.; Rodrigues, C.R. Ultra-Low-Voltage Inverter-Based Operational Transconductance Amplifiers with Voltage Gain Enhancement by Improved Composite Transistors. *Electronics* **2020**, *9*, 1410. [CrossRef]

- 6. Toledo, P.; Crovetti, P.; Aiello, O.; Alioto, M. Fully-Digital Rail-to-Rail OTA with Sub-1000 μm<sup>2</sup> Area, 250-mV Minimum Supply and nW Power at 150-pF Load in 180 nm. *IEEE Solid-State Circuits Lett.* **2020**, *3*, 474–477. [CrossRef]

- 7. Richelli, A.; Delaini, G.; Grassi, M.; Redoute, J.M. Susceptibility of Operational Amplifiers to Conducted EMI Injected Through the Ground Plane into Their Output Terminal. *IEEE Trans. Reliab.* **2016**, 65, 1369–1379. [CrossRef]

- 8. Coccoli, A.; Richelli, A.; Redoute, J.-M. EMI Susceptibility of a Digitally Based Analog Amplifier in a 180-nm CMOS Process. *IEEE Trans. Electromagn. Compat.* **2016**, *58*, 1236–1239. [CrossRef]

- 9. Richelli, A. EMI Susceptibility Issue in Analog Front-End for Sensor Applications. J. Sens. 2016, 2016, 1082454. [CrossRef]

- 10. Richelli, A. Ultra Low Voltage and Low Power Biopotential Amplifier with High Electromagnetic Interference Immunity. *J. Low Power Electron.* **2016**, 12, 124–129. [CrossRef]

- 11. Richelli, A.; Matiga, G.; Redoute, J.M. Design of a Folded Cascode Opamp with Increased Immunity to Conducted Electromagnetic Interference in 0.18 μm. *Elsevier Microelectron. Reliab.* **2015**, *55*, 654–661. [CrossRef]

- 12. Aiello, O.; Fiori, F. A New MagFET-Based Integrated Current Sensor Highly Immune to EMI. *Elsevier Microelectron. Reliab.* **2013**, 53, 573–581. [CrossRef]

- 13. Aiello, O. Electromagnetic Susceptibility of Battery Management Systems' ICs for Electric Vehicles: Experimental Study. *Electronics* **2020**, *9*, 510. [CrossRef]

- 14. Aiello, O.; Crovetti, P.S.; Fiori, F. Susceptibility to EMI of a Battery Management System IC for electric vehicles. In Proceedings of the 2015 IEEE International Symposium on Electromagnetic Compatibility (EMC), Dresden, Germany, 16–22 August 2015; pp. 749–754.

- 15. Aiello, O. Hall-Effect Current Sensors Susceptibility to EMI: Experimental Study. Electronics 2019, 8, 1310. [CrossRef]

- 16. Aiello, O.; Crovetti, P.; Fiori, F. Investigation on the susceptibility of hall-effect current sensors to EMI. In Proceedings of the 10th International Symposium on Electromagnetic Compatibility, York, UK, 26–30 September 2011; pp. 1–4.

- 17. Aiello, O.; Fiori, F. On the Susceptibility of Embedded Thermal Shutdown Circuit to Radio Frequency Interference. *IEEE Trans. Electromagn. Compat.* **2012**, *54*, 405–412. [CrossRef]

- 18. Hayes, P.; Hanada, E.; Bakuzonis, C. Electromagnetic interference risk analysis. *IEEE Eng. Med. Biol. Mag.* **2008**, 27, 39–41. [CrossRef] [PubMed]

- 19. Seidman, S.J.; Pantchenko, O.; Tennakoon, D. Design of Unique Simulators to Evaluate Medical Device Susceptibility to Radio Frequency Identification Exposure. *IEEE Electromagn. Compat. Mag.* **2014**, *3*, 70–74. [CrossRef]

- 20. Aiello, O.; Redoute, J.M. Design of a neural recording amplifier robust to EMI. In Proceedings of the 2013 Asia-Pacific Symposium on Electromagnetic Compatibility (APEMC), Melbourne, Australia, 20–23 May 2013; Volume 54, pp. 405–412.

- 21. Aiello, O. On the DC Offset Current Generated during Biphasic Stimulation: Experimental Study. *Electronics* **2020**, *9*, 1198. [CrossRef]

- 22. Hamilton, T.J.; Jin, C.; van Schaik, A.; Tapson, J. An Active 2-D Silicon Cochlea. *IEEE Trans. Biomed. Circuits Syst.* **2008**, 2, 30–43. [CrossRef]

- 23. Pudi, N.S.A.K.; Boyapati, S.; Baghini, M.S.; Redoute, J.M. Analytical and Experimental Validation of Robustness of the Current Mirrors to EMI. *IEEE Trans. Electromagn. Compat.* **2018**, *60*, 1907–1914. [CrossRef]

- 24. Cordova, D.; Toledo, P.; Fabris, E. A low-voltage current reference with high immunity to EMI. In Proceedings of the 27th Symposium on Integrated Circuits and Systems Design (SBCCI), Aracaju, Brazil, 1–5 September 2014; pp. 1–6.

- Abuelmaatti, M.T.; Abuelmaatti, A.M.T. Effect of EMI on the DC Shift, Harmonic, and Intermodulation Performance of NMOSFET Mirror With a Capacitor Between the Mirror Node and the Ground. IEEE Trans. Electromagn. Compat. 2013, 55, 849–854. [CrossRef]

- 26. Redoute, J.M.; Walravens, C.; Winckel, S.V.; Steyaert, M.S.J. An Externally Trimmed Integrated DC Current Regulator Insensitive to Conducted EMI. *IEEE Trans. Electromagn. Compat.* **2008**, *50*, 63–70. [CrossRef]

- 27. Redoute, J.M.; Steyaert, M. Improved EMI filtering current mirror structure requiring reduced capacitance. *Electron. Lett.* **2006**, 42, 560–561. [CrossRef]

- 28. Redoute, J.M.; Steyaert, M. Current mirror structure insensitive to conducted EMI. Electron. Lett. 2005, 41, 1145–1146. [CrossRef]

- 29. Aiello, O.; Fiori, F. Current sensing circuit for DC-DC converters based on the miller effect. In Proceedings of the 2013 International Conference on Applied Electronics (AE), Pilsen, Czech Republic, 10–12 September 2013; pp. 1–4.

- 30. Aiello, O.; Fiori, F. A new mirroring circuit for power MOS current sensing highly immune to EMI. *Sensor* **2013**, *13*, 1856–1871. [CrossRef] [PubMed]

- 31. Bult, K.; Geelen, G.J.G.M. An Inherently Linear and Compact MOST-Only Current Division Technique. *IEEE J. Solid-State Circuits* **1992**, 27, 1730–1735. [CrossRef]

- 32. Linares-Barranco, B.; Serrano-Gotarredona, T. On the Design and Characterization of Femtoampere Current-Mode Circuits. *IEEE J. Solid-State Circuits* **2003**, *38*, 1353–1363. [CrossRef]

- 33. Delbruck, T.; Schaik, A.V. Bias Current Generators with Wide Dynamic Range. *Analog Integr. Circuits Signal Process.* **2004**, 43, 247–268. [CrossRef]

- 34. Liu, S.C.; Kramer, J.; Indiveri, G.; Delbruck, T.; Douglas, R. Analog VLSI: Circuits and Principles; The MIT Press: Cambridge, MA, USA, 2002

- 35. Greenwald, E.; Maier, C.; Wang, Q.; Beaulieu, R.; Etienne-Cummings, R.; Cauwenberghs, G.; Thakor, N. A CMOS current steering neurostimulation array with integrated DAC calibration and charge balancing. *IEEE Trans. Biomed. Circuits Syst.* **2017**, *11*, 324–335. [CrossRef]

- 36. Tips and Tricks for Designing with Voltage References. Texas Instruments. 2017. Available online: https://www.ti.com/lit/eb/slyc147/slyc147.pdf (accessed on 14 January 2021).

- 37. Krolak, D.; Plojhar, J.; Horsky, P. An Automotive Low-Power EMC Robust Brokaw Bandgap Voltage Reference. *IEEE Trans. Electromagn. Compat.* **2020**, *62*, 2277–2284. [CrossRef]

- 38. Cordova, D.; Toledo, P.; Klimach, H.; Bampi, S.; Fabris, E. A High-PSR EMI-Resistant NMOS-Only Voltage Reference Using Zero-V<sub>T</sub> Active Loads. *IEEE Trans. Electromagn. Compat.* **2017**, *59*, 1347–1355. [CrossRef]

- 39. Cordova, D.; Toledo, P.; Klimach, H.; Bampi, S.; Fabris, E. EMI resisting MOSFET-only voltage reference based on ZTC condition. Analog Integr. Circuits Signal Process. **2016**, 89, 45–59. [CrossRef]

- 40. Fiori, F.; Crovetti, P.S. Complementary differential pair with high immunity to RFI. Electron. Lett. 2002, 38, 1663–1664. [CrossRef]

- 41. IEC 623132-4:2006. Integrated Circuits, Measurement of Electromagnetic Immunity—Part 4: Direct RF Power Injection Method. Available online: https://webstore.iec.ch/publication/6510 (accessed on 14 January 2021).