Article

# A Dual-Mode InGaP/GaAs HBT Power Amplifier Using a Low-Loss Parallel Power-Combining Transformer with IMD3 Cancellation Method

Kyutaek Oh 10, Hyunjin Ahn 1, Ilku Nam 10, Hui Dong Lee 2, Bonghyuk Park 2 and Ockgoo Lee 1,\*0

- Department of Electrical Engineering, Pusan National University, Busan 46241, Korea; ktoh95@pusan.ac.kr (K.O.); hjahn@pusan.ac.kr (H.A.); nik@pusan.ac.kr (I.N.)

- Mobile RF Team, Electronics and Telecommunications Research Institute (ETRI), Daejeon 34129, Korea; leehd@etri.re.kr (H.D.L.); bhpark@etri.re.kr (B.P.)

- \* Correspondence: olee@pusan.ac.kr; Tel.: +82-51-510-7335

Abstract: A dual mode InGaP/GaAs heterojunction bipolar transistor (HBT) power amplifier (PA) using a parallel power-combining transformer (PCT) is presented herein. A low loss transformer is implemented on a printed circuit board (PCB) to improve the passive efficiency of a PCT. Dual-mode operation is applied to reduce the current consumption at a low power level. In the low-power (LP) mode, one of the individual amplifiers is turned off to reduce the current consumption. Additionally, a third-order intermodulation distortion (IMD3) cancellation method using a PCT combiner is proposed to improve linearity performance. Nonlinear IMD3 components from each amplifier cancel each other out through magnetic coupling in the secondary winding of the PCT. The implemented PA achieves a saturated output power of 33.8 dBm and a peak power-added efficiency (PAE) of 54.5% at 0.91 GHz with a 5-V power supply. An average output power of 25.2 dBm with an adjacent channel leakage ratio (ACLR) of -42 dBc is delivered when the PA is tested with an orthogonal frequency division multiplexing (OFDM) 64-quadrature amplitude modulated (64-QAM) signal with a bandwidth of 10 MHz and peak-to-average power ratio (PAPR) of 7.8 dB. When compared with the high-power (HP) mode operation, the LP mode operation could save 48% of the current consumption at an average output power of 10.4 dBm.

Keywords: dual mode; power amplifier; power-combining transformer; IMD3 cancellation

Citation: Oh, K.; Ahn, H.; Nam, I.; Lee, H.D.; Park, B.; Lee, O. A Dual-Mode InGaP/GaAs HBT Power Amplifier Using a Low-Loss Parallel Power-Combining Transformer with IMD3 Cancellation Method. Electronics 2021, 10, 1612. https:// doi.org/10.3390/electronics10141612

Academic Editor: Paolo Colantonio

Received: 11 June 2021 Accepted: 5 July 2021 Published: 6 July 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

With the exponential growth of modern wireless communications, current wireless systems are built with the aim of achieving high-speed data rates. Signals with high-order quadrature amplitude modulations (QAMs) are typically required to achieve these high data rates. These signals have high peak-to-average power ratios (PAPRs) and require highly linear operations of power amplifiers (PAs) in transmitters. Power-combining methods have been widely used to combine the output power from individual amplifiers so as to increase the output power of the PA. Among the power-combining passive networks, transformer-based power-combining methods are the preferred solution, because transformers can enable impedance transformation in addition to balun operation. Series power-combining transformers (SCTs) are the most popular configurations in powercombining transformers [1-9]. In SCTs, multiple primary windings are connected to individual amplifiers, and the output power from each primary winding is magnetically coupled with a secondary winding in series. In Reference [9], the SCT was implemented on a printed circuit board (PCB) to improve the passive loss. Another popular powercombining transformer is the parallel power-combining transformer (PCT) [10–13]. Herein, the output power from each primary winding is magnetically coupled with a secondary winding in a parallel configuration. A PCT configuration can be implemented in an area

smaller than that for an SCT configuration. Hence, in this work, to minimize the loss of the output-combining transformer with a relatively smaller area, a parallel power-combing transformer is implemented on a PCB, providing a thicker Cu layer with a flame retardant 4 (FR4) substrate. Compared with the PA design using an on-chip transformer in [14], the PA design using the transformer on a PCB improves output power and efficiency performances owing to the improvement of the transformer efficiency. The output power level of the PA design using a PCT is much higher than that of [14] by adding the output power from multiple primary windings of the transformer. In addition, a dual-mode operation using a PCT is applied in a high-Q PCB transformer to reduce the current consumption at a lower power level.

Although many studies on PAs using CMOS technology have focused on replacing heterojunction bipolar transistor (HBT)-based PAs, the achievement of comparable circuit performances using CMOS technology continues to be challenging. Thus, HBT-based PAs are widely used in current handset products. Power amplifiers in femto-cell base-station applications require highly linear operations compared with typical PAs in handset applications [15]. A third-order intermodulation distortion (IMD3) cancellation method using parallel-combined transistors was proposed with an inductor-capacitor (*LC*) output matching in [16] to improve the linearity performance using HBT technology. It can also be applied using power-combining transformers. An SCT-based output combiner was used to cancel the IMD3 components in [8]. In this work, an IMD3 cancellation technique using a PCT combiner is proposed wherein the nonlinear components from each primary winding cancel each other out at the secondary winding of the PCT.

The remainder of this paper is organized as follows. Section 2 describes the analysis of the PCT with a high-Q output combiner and the dual-mode operations. In Section 3, the analyses of the proposed IMD3 cancellation mechanism using a PCT combiner are described. Section 4 discusses the measurement results of this work. Finally, Section 5 concludes the paper.

## 2. Low-Loss Dual-Mode Parallel Power-Combining Transformer

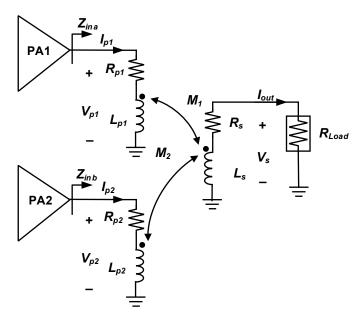

Figure 1 shows the equivalent non-ideal circuit model of a parallel power-combining transformer.  $L_{p1}$  and  $R_{p1}$  represent the net resistance and self-inductance, respectively, of the primary winding connected to PA1.

Figure 1. Equivalent non-ideal circuit model of a parallel power-combining transformer.

Electronics 2021, 10, 1612 3 of 14

> Similarly,  $L_{p2}$  and  $R_{p2}$  represent those of the primary winding connected to PA2.  $L_S$  and  $R_S$  are used to model the secondary winding. The voltages of the primary and secondary windings ( $V_{p1}$ ,  $V_{p2}$ , and  $V_s$ ) can be expressed as

$$\begin{bmatrix} V_{p1} \\ V_{p2} \\ V_s \end{bmatrix} = \begin{bmatrix} R_{p1} + j\omega L_{p1} & 0 & -j\omega M_1 \\ 0 & R_{p2} + j\omega L_{p2} & -j\omega M_2 \\ j\omega M_1 & j\omega M_2 & -(R_s + j\omega L_s) \end{bmatrix} \cdot \begin{bmatrix} I_{p1} \\ I_{p2} \\ I_{out} \end{bmatrix}$$

(1)

$$V_{p1} = (R_{p1} + j\omega L_{p1}) \cdot I_{p1} - j\omega M_1 \cdot I_{out}$$

(2)

$$V_{p2} = (R_{p2} + j\omega L_{p2}) \cdot I_{p2} - j\omega M_2 \cdot I_{out}$$

(3)

$$V_s = j\omega M_1 \cdot I_{p1} + j\omega M_2 \cdot I_{p2} - (R_s + j\omega L_s) \cdot I_{out} = R_{Load} \cdot I_{out}$$

(4)

where

$$I_{out} = \frac{j\omega M_1 \cdot I_{p1} + j\omega M_2 \cdot I_{p2}}{R_s + R_{Load} + j\omega L_s}$$

$R_{Load}$  is the load impedance and is typically 50  $\Omega$ . The input impedances looking into

the transformer of PA1 and PA2 (

$$Z_{ina}$$

and  $Z_{inb}$ ) are as follows:

$$Z_{ina} = \frac{V_{p1}}{I_{p1}} \equiv R_{ina} + jX_{ina} = \frac{\left(R_{p1} + j\omega L_{p1}\right) \cdot \left(R_s + R_{Load} + j\omega L_s\right) + \omega^2 \cdot M_1^2 + \omega^2 \cdot M_1 M_2 \cdot \frac{I_{p2}}{I_{p1}}}{R_s + R_{Load} + j\omega L_s}$$

(5)

$$Z_{inb} = \frac{V_{p2}}{I_{p2}} \equiv R_{inb} + jX_{inb} = \frac{\left(R_{p2} + j\omega L_{p2}\right) \cdot \left(R_s + R_{Load} + j\omega L_s\right) + \omega^2 \cdot M_2^2 + \omega^2 \cdot M_1 M_2 \cdot \frac{I_{p1}}{I_{p2}}}{R_s + R_{Load} + j\omega L_s} \tag{6}$$

where  $R_{in}$  and  $X_{in}$  are the real and imaginary parts, respectively, of  $Z_{in}$ .  $R_{ina}$  and  $R_{inb}$  are expressed as

$$R_{ina} = R_{p1} + \frac{(R_s + R_{Load}) \cdot \omega^2 \cdot \left(M_1^2 + M_1 M_2 \cdot \frac{I_{p2}}{I_{p1}}\right)}{(R_s + R_{Load})^2 + (\omega L_s)^2}$$

(7)

$$R_{inb} = R_{p2} + \frac{(R_s + R_{Load}) \cdot \omega^2 \cdot \left(M_2^2 + M_1 M_2 \cdot \frac{I_{p1}}{I_{p2}}\right)}{(R_s + R_{Load})^2 + (\omega L_s)^2}$$

(8)

The efficiency of the parallel power-combining transformer can be expressed as

$$\eta_{PCT} \equiv \frac{|I_{out}|^2 \cdot R_{Load}}{\left|I_{p1}\right|^2 \cdot R_{Ina} + \left|I_{p2}\right|^2 \cdot R_{Inb}} = \frac{\left\{\omega M_1 \cdot \left|I_{p1}\right| + \omega M_2 \cdot \left|I_{p2}\right|\right\}^2 \cdot R_{Load}}{\left\{(R_s + R_{Load})^2 + (\omega L_s)^2\right\} \cdot \left\{R_{p1} \cdot \left|I_{p1}\right|^2 + R_{p2} \cdot \left|I_{p2}\right|^2\right\} + \omega^2 \cdot (R_s + R_{Load}) \cdot \left\{M_1 \cdot \left|I_{p1}\right| + M_2 \cdot \left|I_{p2}\right|\right\}^2}$$

(9)

A linear PA is typically modeled as a current source. Because both PA1 and PA2 are turned on in the HP mode, both of the current sources  $(I_{v1}$  and  $I_{v2})$  are excited into the transformer. Thus, the transformer efficiency for the high-power (HP) mode (i.e.,  $I_{v1} = I_{v2}$ ), when  $L_{p1} = L_{p2} = L_p$ ,  $R_{p1} = R_{p2} = R_p$ , and  $M_1 = M_2 = M$ , can be expressed as follows:

$$\eta_{PCT}(I_{p1} = I_{p2}) = \frac{(2\omega M)^2 \cdot R_{Load}}{\left\{ (R_s + R_{Load})^2 + (\omega L_s)^2 \right\} \cdot 2R_p + \omega^2 \cdot (R_s + R_{Load}) \cdot (2M)^2}$$

(10)

In addition, because PA1 is turned on while PA2 is turned off in the low-power (LP) mode, only the current source  $I_{p1}$  is excited into the transformer. Thus, the transformer efficiency for the LP mode (i.e.,  $I_{p2} = 0$ ) when  $L_{p1} = L_{p2} = L_p$ ,  $R_{p1} = R_{p2} = R_p$ , and  $M_1 = M_2 = M$  can be expressed as follows:

$$\eta_{PCT}(I_{p2}=0) = \frac{(\omega M)^2 \cdot R_{Load}}{\left\{ (R_s + R_{Load})^2 + (\omega L_s)^2 \right\} \cdot R_p + \omega^2 \cdot (R_s + R_{Load}) \cdot M^2}$$

(11)

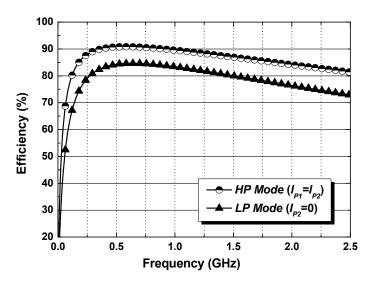

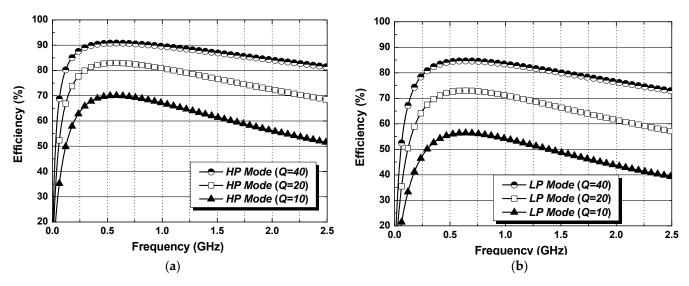

Figure 2 depicts the plot of the calculated transformer efficiencies in the HP and LP modes for the PCT. All the transformer design parameters are determined by considering

the values extracted from the physical layout geometries of a PCB. The mutual inductances are selected as  $M=k\sqrt{L_p\cdot L_s}$  (k=0.57). The inductances and resistances of the primary and secondary windings are set as  $L_p=4.9$  nH,  $L_s=10.8$  nH,  $R_p=\omega L_p/Q_p$ , and  $R_s=\omega L_s/Q_s$  (quality factor  $Q_p=Q_s=40$ ). The calculated efficiencies for both the HP and LP modes are higher than 80% at 0.91 GHz. The calculated efficiencies for the two modes for different Q values are plotted in Figure 3. The efficiency of the PCT can be increased with an increase in the Q value, in both the HP and LP modes. As can be seen in (10) and (11), the transformer efficiency is inversely proportional to  $R_p$  and  $R_s$ . With the selected design parameters of  $L_p$  and  $L_s$ , the increase in  $Q_p$  and  $Q_s$  values decrease  $R_p$  and  $R_s$ , resulting in the increase in the transformer efficiency. Thus, a low-loss power combing transformer can be obtained using a high-Q PCB.

Figure 2. Calculated transformer efficiencies for HP and LP modes for the PCT.

Figure 3. Transformer efficiencies of the PCT calculated for different Q values (a) HP mode (b) LP mode.

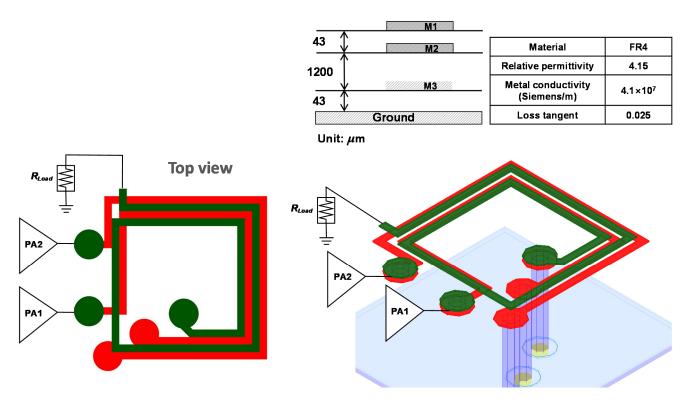

Figure 4 shows a 3D view of the proposed PCT using a four-layer FR4 PCB. The size of the PCT is 2.2 mm  $\times$  2.2 mm.

Electronics **2021**, 10, 1612 5 of 14

Figure 4. Layout of the PCT structure and layout information of the PCB.

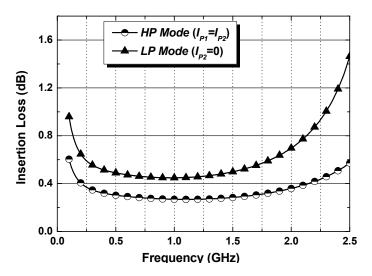

Two primary windings with a width of 100  $\mu$ m are designed using an M2 metal layer. The spacing between the two primary windings is 100  $\mu$ m. For the interconnection, PA1 and PA2 are connected to the primary windings through an M1–M2 via. The M1 top metal layer is used for the construction of the two-turn secondary winding with a width of 100  $\mu$ m. The electromagnetic (EM) simulated insertion losses in the HP and LP modes are plotted in Figure 5. The insertion loss, which is the inverse of the maximum available gain, has been used to evaluate the transformer efficiency [17]. The EM simulated insertion losses in the HP and LP modes are 0.27 dB and 0.45 dB, respectively.

Figure 5. EM simulated insertion loss in HP and LP modes for the PCT.

### 3. IMD3 Cancellation with Parallel Power-Combining Transformer

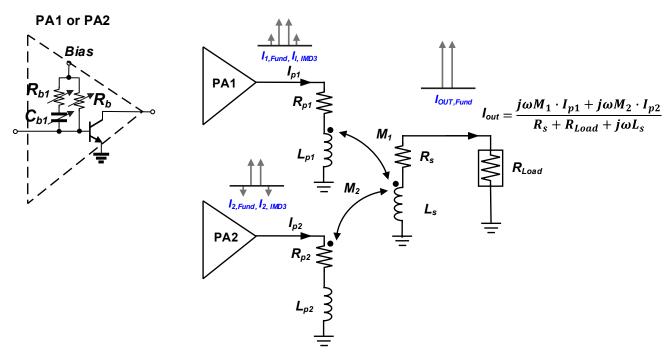

Transmitters in femto-cell base-station applications require highly linear PAs to satisfy their stringent ACLR specification. An IMD3 cancellation using a PCT combiner is proposed to satisfy the stringent ACLR requirement, as shown in Figure 6.

Figure 6. Proposed IMD3 cancellation method using a parallel power-combining transformer.

As described in Equation (4), the currents from each primary winding are added at the output secondary winding through the magnetic couplings of the PCT. With the appropriate selection of  $R_b$ ,  $R_{b1}$ , and  $C_{b1}$  in PA1 and PA2, the phase difference between the fundamental components of the currents from PA1 and PA2 is approximately  $0^{\circ}$  [16]. The phase difference between the IMD3 components of the currents from PA1 and PA2 is approximately  $180^{\circ}$  [16]. Thus, the fundamental components of the currents from PA1 and PA2 are added up at the output load. The nonlinear IMD3 components of the currents from PA1 and PA2 cancel each other out at the output. For the configuration of each unit cell in PA1 and PA2, a ballast resistor  $R_b$  is inserted to prevent thermal runaway of the HBT transistors. In addition, resistors  $R_{b1}$  and  $C_{b1}$  are incorporated to form bypass circuits and compensate for the decrease in the base voltage of the HBT transistor [18].

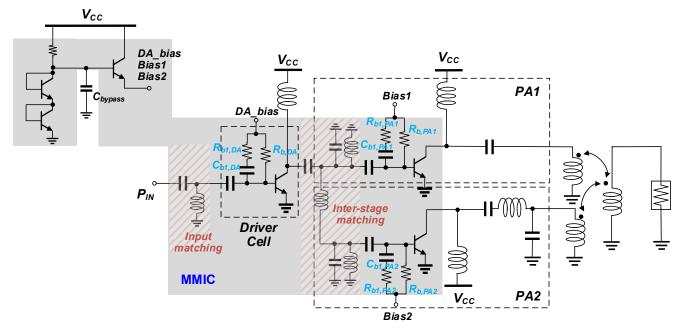

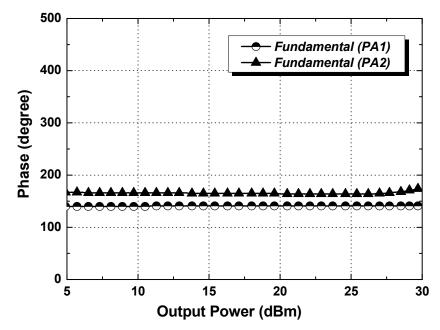

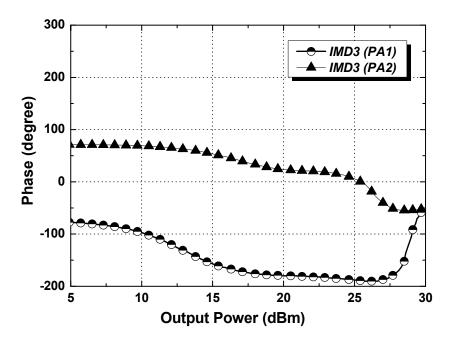

Figure 7 shows the total schematic of the proposed HBT PA with a parallel powercombining transformer. With the appropriate value of  $R_{b,PA1}$ ,  $R_{b1,PA1}$ , and  $C_{b1,PA1}$  in PA1 and  $R_{b,PA2}$ ,  $R_{b1,PA2}$ , and  $C_{b1,PA2}$  in PA2, the phase difference of the IMD3 currents from PA1 and PA2 can be approximately 180°. Thus, the IMD3 currents will cancel each other out at the output. In contrast, the phase difference of the fundamental currents from PA1 and PA2 will be approximately 0° and the fundamental currents will be summed up at the output. For the bias circuit, an active bias circuit topology is applied to compensate for the distortion [18–20]. An on-chip LC input matching and inter-stage matching are indicated with shaded boxes in Figure 7. A driver stage is included to provide sufficient gain of the total PA. Because the changes in  $R_b$ ,  $R_{b1}$ , and  $C_{b1}$  also change the bias currents of PA1 and PA2, different sizes of HBT transistors are selected for PA1 and PA2. Thus, additional matching components (off-chip inductor and capacitor) are added to PA2. The phase change owing to the additional matching circuits is also included in the circuit simulation (see Figure 7). The two-tone simulation with a signal having a tone spacing of 10 MHz has been performed at 0.91 GHz. As shown in Figure 8, the phase difference in the fundamental currents between PA1 and PA2 is less than 30° for an output power of up to

Electronics 2021, 10, 1612 7 of 14

27.3 dBm. Thus, the fundamental currents from PA1 and PA2 can be added to the secondary winding at the PCT. Figure 9 shows the simulated phase of the IMD3 current components.

Figure 7. Schematic of the proposed HBT PA with a parallel power-combining transformer.

Figure 8. Two-tone simulated results for the phase of fundamental currents.

Electronics 2021, 10, 1612 8 of 14

Figure 9. Two-tone simulated results for the phase of IMD3 currents.

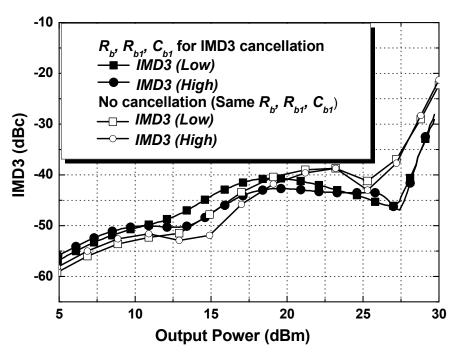

The phase difference in IMD3 currents between PA1 and PA2 is in the range of  $180^{\circ} \pm 40^{\circ}$  for an output power of up to 27.3 dBm. As shown in Figure 6, when the phase of the IMD3 currents from PA1 and PA2 is close to  $180^{\circ}$  out-of-phase, the IMD3 currents will cancel each other out at the output. Figure 10 shows the IMD3 comparison between the condition with IMD3 cancellation and that without the IMD3 cancellation under identical values of  $R_b$ ,  $R_{b1}$ , and  $C_{b1}$ . For the case of the PA without the IMD3 cancellation, the condition of  $R_{b,PA1} = R_{b,PA2}$ ,  $R_{b1,PA1} = R_{b1,PA2}$ , and  $C_{b1,PA1} = C_{b1,PA2}$  is chosen. An IMD3 performance of -40 dBc can be maintained for an output power of up to 28.1 dBm by applying the IMD3 cancellation condition.

Figure 10. Simulated total IMD3 results with and without IMD3 cancellation.

#### 4. Measurement Results

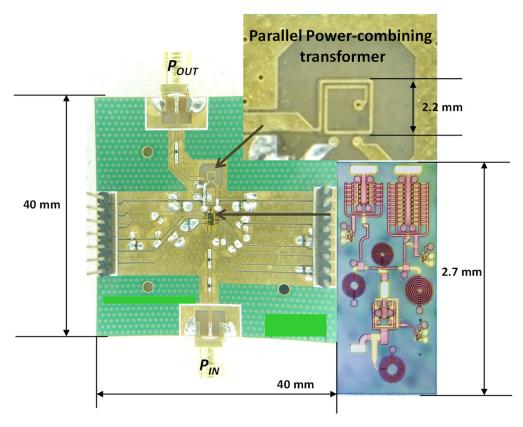

A two-stage dual-mode InGaP/GaAs HBT PA was constructed with fabricated DA/PA devices, including input/inter-stage matching [21] and the proposed PCT implemented using a PCB. Figure 11 shows a photograph of the PA designed with the PCT. The proposed PA was operated at a supply voltage of 5 V.

Figure 11. Photograph of the dual-mode HBT PA using PCB PCT.

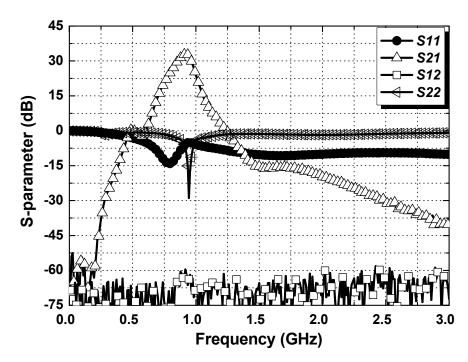

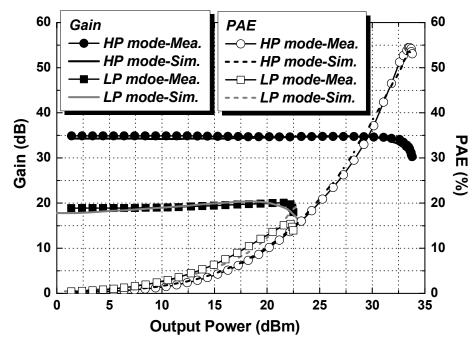

The measured S-parameter results are shown in Figure 12. The implemented PA was tested with a 0.91 GHz single-tone continuous wave (CW). Figure 13 shows the measured power gains and power-added efficiencies (PAEs) of the dual-mode operation (HP and LP modes). Both PA1 and PA2 are turned on for the HP-mode operation. Meanwhile, for the LP mode operation, PA1 is turned on, whereas PA2 is turned off. The measured power gains of the implemented PA are 34.6 dB and 18.9 dB for the HP and LP modes, respectively. The saturated output powers,  $P_{SAT}$ , are 33.8 dBm and 22.5 dBm for the HP and LP modes, respectively. The  $P_{SAT}$  of the PA is over 2 W with the proposed high-Q parallel power-combining transformer. The peak PAEs for the HP and LP modes are 54.5% and 15.4%, respectively.

Figure 12. Measured S-parameter performances.

Figure 13. Measured 0.91 GHz continuous wave performance.

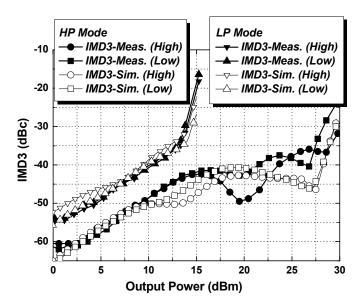

Additionally, the PA was also tested with a two-tone signal centered at 0.91 GHz with a tone spacing of 10 MHz. Figure 14 shows the measured IMD3 results versus the output power. The PA yields output powers of 27.5 dBm and 13.0 dBm in the HP and LP modes, respectively, while attaining IMD3 results of less than -35 dBc. As shown in Figure 9, owing to the mechanism of the IMD3 cancellation, the IMD3 results of less than -35 dBc are obtained up to an output power of 27.5 dBm in the HP mode.

Figure 14. Measured IMD3 results.

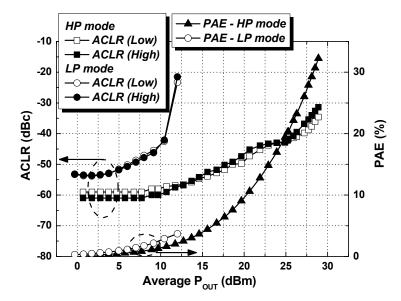

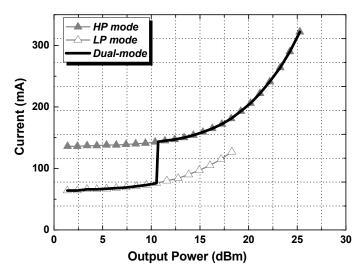

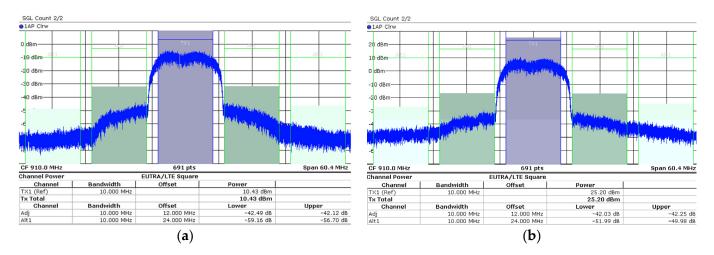

A modulated signal measurement was performed with an orthogonal frequency division multiplexing (OFDM) 64-quadrature amplitude modulation (64-QAM) signal with a bandwidth of 10 MHz and a PAPR of 7.8 dB at 0.91 GHz. Figure 15 shows the measured adjacent channel leakage ratio (ACLR) and PAE versus the average output power. The PA achieves an average output power of 25.2 dBm with PAEs of 20.2%, while attaining ACLR results of less than -42 dBc. As shown in Figure 16, the operation in the LP mode can reduce the current consumption in the low output power range by 48% (i.e., by 68 mA) from that in the HP mode (143 mA), while attaining ACLR results of less than -42 dBc at an average output power of 10.4 dBm. Figure 17 shows the measured PA output spectrums in the HP and LP modes for the OFDM 64-QAM signal with a bandwidth of 10 MHz at 910 MHz. Without a digital pre-distortion (DPD) applied, the ACLR of the proposed PA is obtained at less than -42 dBc, up to 25.2 dBm and 10.4 dBm in the HP and LP modes, respectively.

**Figure 15.** Measured ACLR and PAE for the 64-QAM OFDM signal with a bandwidth of 10 MHz at 0.91 GHz.

**Figure 16.** Measured current consumption for the 64-QAM OFDM signal with a bandwidth of 10 MHz at 0.91 GHz.

**Figure 17.** Measured PA output spectrum for the OFDM 64-QAM signal with a bandwidth of 10 MHz at 0.91 GHz: (a) output power of 10.4 dBm in the LP mode, (b) output power of 25.2 dBm in HP mode.

Table 1 compares the PA developed in this work to the other PAs using other power-combining transformers on a PCB. A PCT can be implemented on a PCB with an area smaller than that of the SCT. Table 2 summarizes the HBT PAs for the femto-cell applications. Among the PAs in the comparison table, the proposed PA demonstrates a dual-mode operation to reduce the current consumption at a lower power level with a high-Q PCT configuration.

**Table 1.** Performance comparison of PAs with power-combining transformers on a PCB.

| Ref.      | Power-Combining<br>Transformer<br>(Size: mm <sup>2</sup> ) | Tech. | Freq.<br>(GHz) | P <sub>SAT.</sub> (dBm) | Gain<br>(dB)          | Peak PAE<br>(%)        |

|-----------|------------------------------------------------------------|-------|----------------|-------------------------|-----------------------|------------------------|

| [9]       | SCT<br>(5.1 mm × 2.4 mm)                                   | CMOS  | 0.875          | 31.7                    | 30.3                  | 62                     |

| This work | Dual-mode PCT (2.2 mm $\times$ 2.2 mm)                     | HBT   | 0.91           | 33.8 (HP)<br>22.5 (LP)  | 34.6 (HP)<br>18.9(LP) | 54.5 (HP)<br>15.4 (LP) |

|              | Output<br>Features                      | Freq.<br>(GHz) | P <sub>SAT.</sub><br>(dBm)   | Gain<br>(dB)                 | Peak PAE<br>(%)              | Signal                              | Pout (dBm)<br>@ -42 dBc<br>ACLR | PAE<br>(Current)<br>@ Pout                                                 |

|--------------|-----------------------------------------|----------------|------------------------------|------------------------------|------------------------------|-------------------------------------|---------------------------------|----------------------------------------------------------------------------|

| [22]         | LC Matching                             | 0.85           | 34.5 *                       | 31.8 *                       | N/A                          | WCDMA<br>64DPCH                     | 26.0 *                          | (540 mA)<br>@ 25 dBm                                                       |

| [23]         | LC Matching                             | 0.9            | N/A                          | 31.7                         | N/A                          | 10-MHz<br>LTE TM1.1                 | 19.8 *                          | 14.0% *<br>@ 19.8 dBm                                                      |

| [21]         | Single- &<br>Two-Winding<br>Transformer | 0.91           | 33.3                         | 34.3                         | 61.3                         | 10-MHz<br>64QAM<br>(7.8 dB<br>PAPR) | 26.0                            | 26.8%<br>(297 mA)<br>@ 26.0 dBm                                            |

| [14]         | On-chip<br>Transformer                  | 2.3            | 31.0                         | 26.0                         | 27.6                         | 10-MHz<br>LTE<br>(7.3 dB<br>PAPR)   | 18.1 *                          | 4.7% *<br>@ 18.1 dBm                                                       |

| This<br>work | Dual-Mode<br>PCT                        | 0.91           | 33.8<br>(HP)<br>22.5<br>(LP) | 34.6<br>(HP)<br>18.9<br>(LP) | 54.5<br>(HP)<br>15.4<br>(LP) | 10-MHz<br>64QAM<br>(7.8 dB<br>PAPR) | 25.2<br>(HP)<br>10.4<br>(LP)    | 20.1% (322 mA)<br>@25.2 dBm (HP)<br>143 mA<br>(HP)/75 mA (LP)<br>@10.4 dBm |

**Table 2.** Performance comparison with linear femto-cell HBT PAs.

#### 5. Conclusions

In this paper, an HBT PA with a high-*Q* parallel power-combining transformer to efficiently combine two individual amplifiers with a relatively compact area is proposed. In addition, dual-mode operation is adopted in the PA with the PCT configuration to reduce the current consumption. Furthermore, an IMD3 cancellation technique using the PCT combiner is presented to satisfy the stringent ACLR requirement for femto-cell base-station PAs. The implemented PA achieves a saturated output power, power gain, and peak PAE of 33.8 dBm, 34.6 dB, and 54.5%, respectively. Current consumption saving of 48% can be obtained with the LP mode operation at an output power of 10.4 dBm.

**Author Contributions:** Conceptualization, K.O., H.A. and O.L.; methodology, K.O. and O.L.; validation, K.O., H.A., I.N., H.D.L., B.P. and O.L.; data curation, K.O. and H.A.; writing—original draft preparation, K.O. and O.L.; writing—review and editing, I.N., H.D.L., B.P. and H.A. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by Korea Institute for Advancement of Technology (KIAT) grant funded by the Korea Government (MOTIE) (P0012451, The Competency Development Program for Industry Specialist) and the Ministry of Science and ICT (MIST), Korea, under the Information Technology Research Center (ITRC) support program (IITP-2021-2017-0-01635) supervised by the Institute for Information & Communications Technology Planning & Evaluation (IITP).

Acknowledgments: The CAD tools were supported by the IDEC, Korea.

Conflicts of Interest: The authors declare no conflict of interest.

### References

- 1. Wang, F.; Wang, H.A. A high-power broadband multi-primary DAT-based doherty power amplifier for mm-wave 5G applications. *IEEE J. Solid-State Circuits* **2021**, *56*, 1668–1681. [CrossRef]

- 2. Aoki, I.; Kee, S.D.; Rutledge, D.B. Hajimiri, Distributed active transformer—A new power-combining and impedance-transformation technique. *IEEE Trans. Microw. Theory Tech.* **2002**, *50*, 316–331. [CrossRef]

- 3. Aoki, I.; Kee, S.D.; Rutledge, D.B.; Hajimiri, A. Fully integrated CMOS power amplifier design using the distributive active-transformer architecture. *IEEE J. Solid-State Circuits* **2002**, *37*, 371–383. [CrossRef]

- 4. Kaymaksut, E.; Reynaert, P. Dual-mode CMOS Doherty LTE power amplifier with symmetric hybrid transformer. *IEEE J. Solid-State Circuits* **2015**, *50*, 1974–1987. [CrossRef]

- 5. Liu, G.; Haldi, P.; Liu, T.-J.K.; Niknejad, A.M. Fully integrated CMOS power amplifier with efficiency enhancement at power back-off. *IEEE J. Solid-State Circuits* **2008**, 43, 600–609. [CrossRef]

<sup>\*</sup> graphically estimated

6. Haldi, P.; Chowdhury, D.; Reynaert, P.; Liu, G.; Niknejad, A.M. A 5.8 GHz 1 V linear power amplifier using a novel on-chip transformer power combiner in standard 90 nm CMOS. *IEEE J. Solid-State Circuits* **2008**, *43*, 1054–1063. [CrossRef]

- 7. Chowdhury, D.; Hull, C.D.; Degani, O.B.; Wang, Y.; Niknejad, A.M. A fully integrated dual-mode highly linear 2.4 GHz CMOS power amplifier for 4G WiMax applications. *IEEE J. Solid-State Circuits* **2009**, *44*, 3393–3402. [CrossRef]

- 8. Kaymaksut, E.; Reynaert, P. Transformer-based uneven Doherty power amplifier in 90 nm CMOS for WLAN Applications. *IEEE J. Solid-State Circuits* **2012**, 47, 1659–1671. [CrossRef]

- 9. Jang, J.; Park, P.; Kim, H.; Hong, K. A CMOS RF power amplifier using an off-chip transmission line transformer with 62% PAE. *IEEE Microw. Wirel. Compon. Lett.* **2007**, 17, 385–387. [CrossRef]

- Choi, S.E.; Ahn, H.; Hur, J.; Kim, K.W.; Nam, I.; Choi, J.; Lee, O. A fully integrated compact outphasing CMOS power amplifier using a parallel-combining transformer with a tuning inductor method. *Electronics* 2020, 9, 257. [CrossRef]

- An, K.H.; Lee, O.; Kim, H.; Lee, D.H.; Han, J.; Yang, K.S.; Chang, J.J.; Woo, W.; Lee, C.-H.; Laskar, J. Power-combining transformer techniques for fully-integrated CMOS power amplifiers. *IEEE J. Solid-State Circuits* 2008, 43, 1064–1075. [CrossRef]

- An, K.H.; Lee, D.H.; Lee, O.; Kim, H.; Han, J.; Kim, W.; Lee, C.-H.; Kim, H.; Laskar, J. A 2.4 GHz fully integrated linear CMOS power amplifier with discrete power control. IEEE Microw. Wirel. Compon. Lett. 2009, 19, 479–481.

- 13. Kim, J.; Yoon, Y.; Kim, H.; An, K.H.; Kim, W.; Kim, H.-W.; Lee, C.-H.; Kornegay, K.T. A linear multi-mode CMOS power amplifier with discrete resizing and concurrent power combining structure. *IEEE J. Solid-State Circuits* **2011**, *46*, 1034–1048.

- 14. Ahn, H.; Choi, S.; Ryu, H.; Baek, S.; Nam, I.; Lee, O. 2.3-GHz HBT power amplifier with parallel-segmented on-chip autotransformer. *IEEE Microw. Wirel. Compon. Lett.* **2017**, 27, 1140–1142. [CrossRef]

- 15. TDD Home eNode B (HeNB) Radio Frequency (RF) Requirements Analysis; Document 3GPP TS 36.922; The 3rd Generation Partnership Project Tech. Specification Group: Valbonne, France, 2014.

- 16. Baek, S.; Ahn, H.; Nam, I.; Ryu, N.; Lee, H.D.; Park, B.; Lee, O. A linear InGaP/GaAs HBT power amplifier using parallel-combined transistors with IMD3 cancellation. *IEEE Microw. Wirel. Compon. Lett.* **2016**, *26*, 921–923. [CrossRef]

- 17. El-Charniti, O.; Kerhervé, E.; Bégueret, J.-B. Modeling and characterization of on-chip transformers for silicon RFIC. *IEEE Trans. Microw. Theory Tech.* **2007**, *55*, 607–615. [CrossRef]

- 18. Oka, T.; Hasegawa, M.; Hirata, M.; Amano, Y.; Ishimaru, Y.; Kawamura, H.; Sakunoi, K. A high-power low-distortion GaAs HBT power amplifier for mobile terminals used in broadband wireless applications. *IEEE J. Solid-State Circuits* **2007**, 42, 2123–2127. [CrossRef]

- 19. Noh, Y.S.; Park, C.S. PCS/W-CDMA dual-band MMIC power amplifier with a newly proposed linearizing bias circuit. *IEEE J. Solid-State Circuits* **2002**, *37*, 1096–1099.

- 20. Yoshimasu, T.; Akagi, M.; Tanba, N.; Hara, S. An HBT MMIC power amplifier with an integrated diode linearizer for low-voltage portable phone applications. *IEEE J. Solid-State Circuits* **1998**, 33, 1290–1296. [CrossRef]

- 21. Ahn, H.; Oh, K.; Nam, I.; Lee, O. Highly Efficient HBT Power Amplifier Using High-Q Single- and Two-Winding Transformers with IMD3 Cancellation IEEE Access to Be Published. Available online: https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=9450832 (accessed on 10 June 2021).

- 22. Skyworks Solutions, Inc. Available online: https://www.skyworksinc.com (accessed on 10 June 2021).

- 23. NXP Semiconductors Inc. Available online: https://www.nxp.com (accessed on 10 June 2021).