MDPI

Article

# A New Realization of Electronically Tunable Multiple-Input Single-Voltage Output Second-Order LP/BP Filter Using VCII

Leila Safari <sup>1</sup>, Gianluca Barile <sup>1,2</sup>,\*<sup>0</sup>, Giuseppe Ferri <sup>1</sup><sup>0</sup>, Mattia Ragnoli <sup>1</sup><sup>0</sup> and Vincenzo Stornelli <sup>1,2</sup><sup>0</sup>

- Department of Industrial and Information Engineering, Università degli Studi dell'Aquila, 67100 L'Aquila, Italy; leilasafari@yahoo.com (L.S.); giuseppe.ferri@univaq.it (G.F.); mattia.ragnoli@graduate.univaq.it (M.R.); vincenzo.stornelli@univaq.it (V.S.)

- DEWS, Università degli Studi dell'Aquila, 67100 L'Aquila, Italy

- \* Correspondence: gianluca.barile@univaq.it

**Abstract:** In this paper, a new realization of electronically tunable voltage output second-order low-pass (LP) and band-pass (BP) filter is presented. The circuit has a multiple-input single-output structure, and LP and BP outputs are provided using the same structure. One electronically variable second-generation voltage conveyor (VCII), whose impedance at the Y port can be electronically varied using a control current ( $I_{con}$ ), two capacitors, and one resistor are used. By changing the value of  $I_{con}$ , the impedance value at the Y port can be electronically varied; therefore, the value of  $ω_0$  can be tuned. This feature helps to reduce the number of passive components used. Interestingly, the LP and BP outputs are provided at the low-impedance Z port of the VCII, and there is no need for an extra voltage buffer for practical use. The circuit enjoys a simple realization consisting of only 24 MOS transistors. Simulation results using PSpice and 0.18 μm CMOS parameters are provided. The value of  $ω_0$  can be varied from 1.2 MHz to 1.7 MHz, while  $I_{con}$  varies from 0 to 50 μA, with a power consumption variation from 244 μW to 515 μW.

**Keywords:** band-pass filter; CCII; current mode signal processing; electronically tunable; low-pass filter VCII; second-order filter; voltage conveyor

Citation: Safari, L.; Barile, G.; Ferri, G.; Ragnoli, M.; Stornelli, V. A New Realization of Electronically Tunable Multiple-Input Single-Voltage Output Second-Order LP/BP Filter Using VCII. Electronics 2022, 11, 646. https://doi.org/10.3390/electronics11040646

Academic Editor: Inhee Lee

Received: 15 January 2022 Accepted: 17 February 2022 Published: 18 February 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

## 1. Introduction

Filter design represents a widespread and important topic, due to the interesting application in communication, measurement, instrumentation, control, and signal processing [1–3]. In recent years, current mode signal processing has been the focus of researchers in the design of various types of active filters. This is attributed to the numerous advantages offered by current mode signal processing, such as simple realization, high-frequency performance, low-voltage operation, etc. [4–9]. Importantly, current mode signal processing provides the opportunity of realizing electronically tunable filters, which are highly suitable for the requirements of full integration. These features have enabled various innovative current mode solutions in the realization of active filters [1–3,10–19].

A survey of the literature shows that considerable effort has been devoted to realizing filter topologies based on various current mode active building blocks (ABBs), such as current buffers (CBs) [1,3], second-generation current conveyors (CCIIs) [8–11], current differential transconductance amplifiers (CDTAs) [13], differential voltage current conveyors (DVCCs) [15,17], current differencing transconductance amplifiers (CCCTAs) [12,18], current feedback operational amplifiers (CFOAs) [19], current differencing buffered amplifiers (CDBAs) [20,21], fully differential CCIIs (FDCCIIs) [22], etc. However, the current mode active filters reported in [1,3–19,22] suffered from a common weakness of applications requiring voltage signals. In these circuits, the output signal was either in current form, making them unsuitable for applications requiring voltage signals, or in voltage form provided on a high impedance port, necessitating additional voltage buffers for practical use. In addition, the circuits reported in [1,3,10,11,15,17–22] were not electronically tunable.

Electronics **2022**, 11, 646 2 of 11

Moreover, the CB-based circuit reported in [3], which was able to realize all-pass and notch functions, required additional current followers (CFs) at the outputs for practical application. In the CCII-based circuit presented in [11], up to five active building blocks were used. The CCCTA- and CDTA-based filters presented in [12,13,18] were implemented using BJT technology. The filter reported in [16] suffered from circuit complications, because the FDCCII used as the active building block was realized using 60 MOS transistors, and thus required a high supply voltage of  $\pm 1.65$  V. The topology of [17] employed three dual-output DVCC blocks with a total number of 84 transistors. The CFOA-based filter presented in [19] required extra current buffers at the outputs for practical use.

Recently, researchers' focus has been concentrated on the dual circuit of the CCII, referred to as a second-generation voltage conveyor (VCII) [22–27]. Owing to the low-impedance voltage output port, VCII is highly suitable for applications requiring output signal in voltage form. A new research area has opened up related to the design and possible applications of the VCII. VCII-based voltage output second-order high-pass (HP), low-pass (LP), band-stop (BS), band-pass (BP) and all-pass (AP) filters have been reported recently [28,29]. However, these structures include more than one ABB. They also lack electronic tuning capability. In this paper, we aim to present second-order LP and BP filters using only one VCII with electronic tunability. The  $\omega_0$  of the proposed filters can be tuned using a control current. The organization of this paper is as follows: in Section 2, the proposed circuit is presented. A non-ideal analysis is given in Section 3. Section 4 includes the simulation results, and finally, Section 5 presents the conclusions.

### 2. The Proposed Circuit

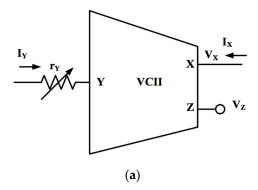

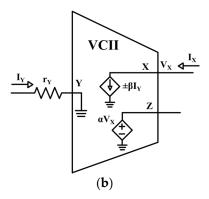

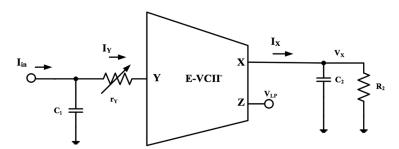

A symbolic representation and internal structure of an electronically tunable VCII is shown in Figure 1 [23]. An E-VCII consists principally of a current buffer between the Y and X ports, and a voltage buffer between the X and Z ports. In the electronically tunable VCII, the input resistance of the CB is shown by  $r_Y$ , which is electronically tunable. Matrix Equation (1) shows the operation of the VCII with electronically tunable impedance at Y:

$$\begin{bmatrix} I_X \\ V_Z \\ V_Y \end{bmatrix} = \begin{bmatrix} \pm 1 & 0 & 0 \\ 0 & 1 & 0 \\ r_Y & 0 & 0 \end{bmatrix} \begin{bmatrix} I_Y \\ V_X \\ I_Z \end{bmatrix}$$

(1)

In Equation (1), + and - indicate a VCII $^+$  and a VCII $^-$ , respectively. There is a current buffer between the Y and X ports with a current gain of unity, while there is a voltage buffer between the X and Z ports with a voltage gain of unity. The resistance at the Y port is shown by  $r_Y$ , which is electronically tunable. We take advantage of the electronically tunable  $r_Y$  instead of adding an external passive resistor.

Figure 1. Cont.

Electronics **2022**, 11, 646 3 of 11

**Figure 1.** VCII with electronic tunable impedance at the Y port: (a) symbolic representation; (b) internal structure.

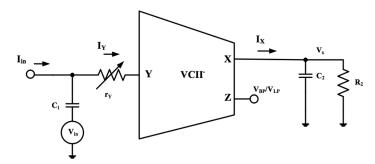

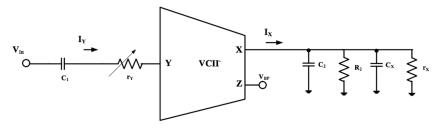

Figure 2 shows the schematic of the proposed VCII $^-$ -based BP/LP filter. It is composed of one VCII $^-$ , one external resistor, and two grounded capacitors. The internal resistance at Y is shown as  $r_Y$ , and is exploited to electronically vary the natural frequency of the filter. BP/LP outputs as voltage signals are produced at the Z port.

Figure 2. The proposed  $VCII^-$ -based second-order LP/ BP filter realization.

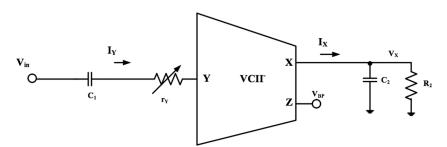

As can be seen in Figure 3, for  $I_{in} = 0$ , there will be a second-order BP transfer function. The analysis of the proposed BP circuit under ideal conditions is as follows:

Figure 3. The proposed VCII<sup>-</sup>-based second-order BP filter realization.

By assuming Y port at ground, for  $I_Y$  we have:

$$I_{Y} = \frac{sC_{1}}{1 + sC_{1}r_{Y}}V_{in}$$

(2)

Using Equation (1):

$$I_{X} = I_{Y} \tag{3}$$

Using Equations (2) and (3),  $V_X$  is found as:

$$V_{X} = \frac{sC_{1}R_{2}}{(1 + sC_{1}r_{Y})(1 + sC_{2}R_{2})}V_{in}$$

(4)

Electronics 2022, 11, 646 4 of 11

Using Equations (1) and (4), V<sub>BP</sub> is:

$$V_{BP} = \frac{sC_1R_2}{(1 + sC_1r_Y)(1 + sC_2R_2)}V_{in}$$

(5)

From Equation (5),  $\omega_0$  and Q are found, respectively, as:

$$\omega_0 = \frac{1}{\sqrt{C_1 r_Y C_2 R_2}} \tag{6}$$

$$Q = \frac{\sqrt{C_1 r_Y C_2 R_2}}{C_1 r_Y + C_2 R_2} \tag{7}$$

As can be seen from (6), the value of  $\omega_0$  can be electronically tuned by varying  $r_Y$ .

If  $V_{in}$  = 0 and the input signal is applied as  $I_{in}$ , a second-order LP transfer function is achieved, as shown in Figure 4. A similar analysis gives the second-order LP transfer function as:

$$V_{LP} = \frac{R_2}{(1 + sC_1r_Y)(1 + sC_2R_2)} I_{in}$$

(8)

**Figure 4.** The proposed VCII<sup>-</sup>-based second-order LP filter realization.

# 3. Non-Ideal Analysis

The operation of a VCII $^-$  in non-ideal conditions is given by Equation (9). Here,  $\beta$  and  $\alpha$  are current gain between the Y and X terminals and voltage gain between the X and Z terminals, respectively. The main parasitic impedances associated with the VCII $^-$  ports are shown by  $r_x$  (the parasitic resistance related to X port),  $C_x$  (parasitic capacitance related to X port) and  $r_Y$  (parasitic resistance related to Y port). The ideal values of  $r_x$  and  $r_y$  are infinity and zero, respectively.

$$\begin{bmatrix} I_{X} \\ V_{Z} \\ V_{Y} \end{bmatrix} = \begin{bmatrix} -\beta & \frac{1}{r_{x}} + sC_{x} & 0 \\ 0 & \alpha & 0 \\ r_{Y} & 0 & 0 \end{bmatrix} \begin{bmatrix} I_{Y} \\ V_{X} \\ I_{Z} \end{bmatrix}$$

(9)

Figure 5 shows the proposed second-order BP filter in which all parasitic elements are modeled. Using Equation (9), the transfer function of Figure 5 is found as:

$$V_{BP} = \frac{s\alpha\beta C_1 R_{eq}}{[1 + sC_1 r_Y)] [1 + s(C_2 + C_X) R_{eq}]} V_{in}$$

(10)

where:

$$R_{eq} = r_X || R_2 \tag{11}$$

Electronics 2022, 11, 646 5 of 11

Figure 5. The proposed second-order BP filter with VCII<sup>-</sup> non-ideal components.

From Equation (9),  $\omega_0$  and Q are found, respectively, as:

$$\omega_0 = \frac{1}{\sqrt{C_1 r_Y (C_2 + C_X) R_{eq}}}$$

(12)

$$Q = \frac{\sqrt{C_1 r_Y (C_2 + C_X) R_{eq}}}{C_1 r_Y + (C_2 + C_X) R_{eq}}$$

(13)

Similar analysis for the proposed second-order LP filter gives:

$$V_{LP} = \frac{\alpha \beta R_{eq}}{(1 + sC_1 r_Y)(1 + s(C_2 + C_X)R_{eq})} I_{in}$$

(14)

# 4. CMOS Implementation of VCII<sup>-</sup> with Electronically Tunable Impedance at the Y Port

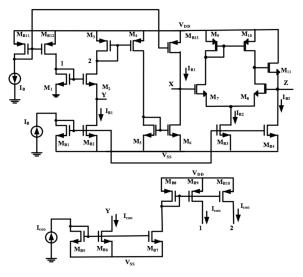

Figure 6 shows the CMOS implementation of VCII $^-$  with electronically tunable impedance at the Y port. It consists of 24 MOS transistors. Inversion of the current buffer comprising transistors  $M_1$ – $M_6$  is performed to transfer the Y port input current to the X port. The control current  $I_{con}$  is used to change the bias current of common gate transistor  $M_2$ ; therefore, electronically variable impedance at the Y port is provided. To maintain a constant bias current at the other branches,  $I_{con}$  is also applied to node 2; therefore, only the bias current of  $M_2$  is varied. In addition, to maintain a zero offset voltage at the Y port, bias currents of  $M_1$  and  $M_2$  must be kept equal, so  $I_{con}$  is also applied to node 1.

**Figure 6.** CMOS implementation of VCII<sup>-</sup> with electronically variable impedance at the Y port. Nodes Y, 1 and 2 from the lower section of the schematic are connected to their counterparts in the upper section of the schematic.

Electronics **2022**, 11, 646 6 of 11

The voltage buffer consists of transistors  $M_7$ – $M_{11}$ , which are a differential pair cascaded by a voltage follower. They are connected in a closed loop configuration so as to decrease Z port impedance and improve the overall accuracy of the buffering action of transferring the X node voltage to the Z node. Transistors  $M_{Bi}$  for i=1–12 provide the bias and control currents. The electronically variable impedance at the Y port is given by (with the usual meanings of the symbols):

$$r_{Y} = \frac{1}{gm_{M2}} = \left[ \sqrt{\mu C_{ox} \frac{W_{M2}}{L_{M2}} (I_{B1} + I_{con})} \right]^{-1}$$

(15)

### 5. Proposed LP/BP Second-Order Filter Simulation Results

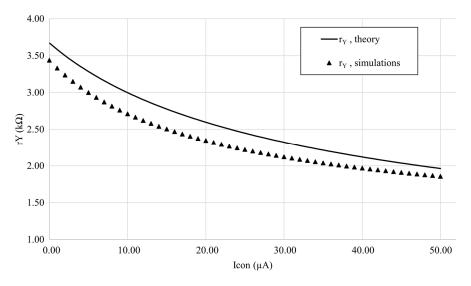

PSpice simulations of the VCII $^-$  using 0.18 µm CMOS TSMC technology and a supply voltage of  $\pm 0.9$  V are presented in Figure 6. The transistor sizes for the used PMOS and NMOS transistors were W = 9 µm, L = 0.9 µm and W = 27 µm, L = 0.9 µm, respectively. The values of bias currents were  $I_B = I_{B1} = I_{B2} = I_{B3} = 20$  µA. The control current  $I_{con}$  was varied from 0 µA to 50 µA. All bias currents were realized by simple current mirrors so as to ensure the best possible voltage swing at each terminal. To validate the proposed tuning technique, a comparison between the theoretical behavior of  $r_Y$  according to (15), and the values of the same magnitude extracted from the simulations is presented in Figure 7. In particular,  $\mu = \mu_{electrons} = 0.13$  m $^2$ /Vs,  $C_{ox} = 9.51 \times 10^{-4}$  F/m $^2$  are constant values dependent on the technology. As can be seen, the trend between the theoretical and simulated curves matches, while the percentage error always remains below 10%. This error mirrors the inaccuracies of  $M_{B1}$ ,  $M_{B2}$  and  $M_{B5}$ – $M_{B10}$ , which generate  $I_{B1}$  and  $I_{con}$ , directly impacting the simulated value of  $r_Y$ .

**Figure 7.** Comparison between simulated and theoretical ry values as a function of I<sub>con</sub>.

The large signal behavior of the used VCII was evaluated by extracting the slew rate (SR) figures both for the current output, X, and for the voltage output, Z. For the former, a  $\pm 20~\mu A$  step was used, which corresponds to the full  $\pm I_B$  range, while for the latter, a  $\pm 500~mV$  step was applied to the X terminal, with a 3 pF capacitive load at Z. The current slew rates were:  $SR^+{}_I=13\times 10^3~A/s$  and  $SR^-{}_I=-0.64\times 10^3~A/s$ , and the voltage slew rates were:  $SR^+{}_V=1.4\times 10^8~V/s$  and  $SR^-{}_V=-6.64\times 10^6~V/s$ . As expected, the class A biasing of the input and output stages determines the difference between positive and negative values, with the latter remaining lower due to the sinking capability of the architecture being limited by the biasing current.

Table 1 shows the simulation results for the performance parameters and parasitic elements of the used VCII<sup>-</sup>.

Electronics **2022**, 11, 646 7 of 11

|         | Parameter            | Value                                                        |  |  |  |

|---------|----------------------|--------------------------------------------------------------|--|--|--|

|         | $I_{con} = 0 \mu A$  | 3.43 kΩ                                                      |  |  |  |

| $r_{Y}$ | $I_{con} = 25 \mu A$ | $2.18~\mathrm{k}\Omega$                                      |  |  |  |

|         | $I_{con} = 50 \mu A$ | $1.8~\mathrm{k}\Omega$                                       |  |  |  |

|         | $r_{\chi}$           | $244~\mathrm{k}\Omega$                                       |  |  |  |

|         | $r_z$                | $48~\Omega$                                                  |  |  |  |

|         | α                    | 0.981                                                        |  |  |  |

|         | $I_{con} = 0 \mu A$  | 1.04                                                         |  |  |  |

| β       | $I_{con} = 25 \mu A$ | 1.03                                                         |  |  |  |

|         | $I_{con} = 50 \mu A$ | 1.023                                                        |  |  |  |

|         | $C_{x}$              | 64 fF                                                        |  |  |  |

| Pow     | er dissipation       | 244–515 μW                                                   |  |  |  |

|         | ositive, negative)   | $13 \times 10^3 \text{ A/s}, -0.64 \times 10^3 \text{ A/s}$  |  |  |  |

| - 1     | ositive, negative)   | $1.4 \times 10^8 \text{ V/s}, -6.64 \times 10^6 \text{ V/s}$ |  |  |  |

**Table 1.** The simulated characteristics of VCII<sup>-</sup> with electronically variable impedance at the Y port.

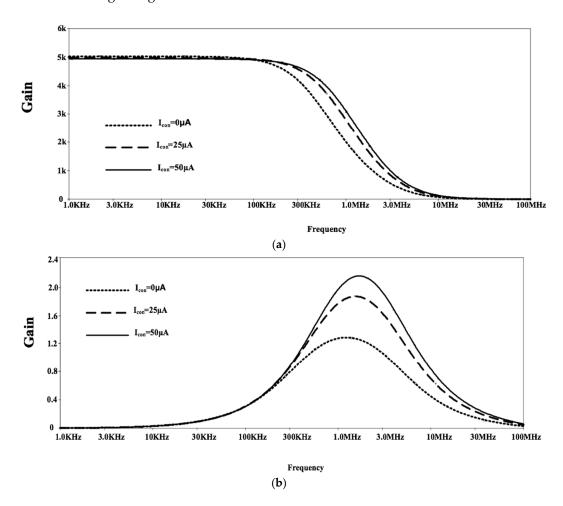

The proposed filter presented in Figure 2 was simulated using the VCII $^-$  presented in Figure 6. The values of the passive components were  $C_1$  = 100 pF,  $C_2$  = 10 pF and  $R_2$  = 5 k $\Omega$ . Figure 8 shows the AC frequency performance of the LP and BP outputs for different values of  $I_{con}$ . On the basis of the simulation results,  $\omega_0$  was 1.2 MHz, 1.59 MHz and 1.7 MHz for  $I_{con}$  values of 0  $\mu$ A, 25  $\mu$ A and 50  $\mu$ A, respectively. On the basis of Equation (12), the values of  $\omega_0$  were 1.22 MHz, 1.54 MHz and 1.69 MHz, respectively. Fortunately, there is good agreement between the simulation and the calculation.

**Figure 8.** Proposed circuit frequency performance for (a) LP and (b) BP outputs.

Electronics 2022, 11, 646 8 of 11

The robustness of the proposed solutions was tested by running 30 Monte Carlo (MC) simulations at each of the fast, typical, and slow corners. PVT combinations were as follows: SS,  $\pm 0.85$  V, 80 °C; TT,  $\pm 0.9$  V, 25 °C; FF,  $\pm 0.95$  V, -20 °C, whereas for the MC analysis, we considered 3% mismatches in V<sub>th</sub> and C<sub>ox</sub> of all transistors alongside a 5% variation in the value of the passive elements. The results are summarized in Table 2. As can be seen, the proposed circuit is robust against mismatches.

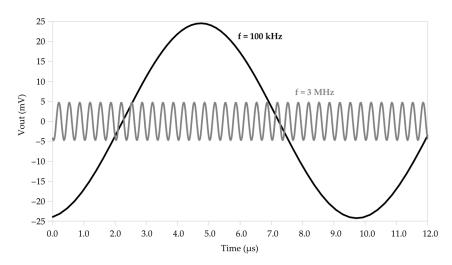

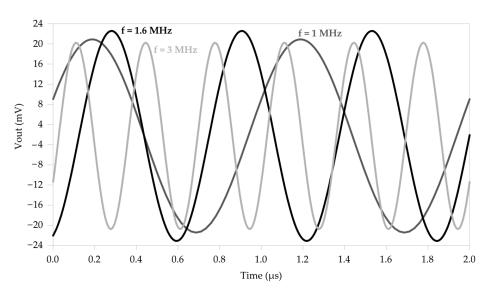

Finally, Figures 10 and 11 show a time domain example of both the low-pass and band-pass filters. For the LP filter, an input current of 5  $\mu$ A was used with frequencies of 100 kHz and 3 MHz. I<sub>con</sub> was set to 50  $\mu$ A. Similarly, for the BP, an input voltage of 10 mV was applied at three different frequencies, of 1.6 MHz, 1 MHz and 3 MHz. I<sub>con</sub> was set equal to 50  $\mu$ A.

|                      | Value                   | Max                       | Min                       | Mean                      |

|----------------------|-------------------------|---------------------------|---------------------------|---------------------------|

|                      | Magnitude <sub>BP</sub> | 2.78 dB                   | 1.67 dB                   | 2.16 dB                   |

| $I_{con} = 0 \mu A$  | $Magnitude_{LP}$        | $74.16~\mathrm{dB}\Omega$ | $73.96~\mathrm{dB}\Omega$ | $74.05~\mathrm{dB}\Omega$ |

|                      | $\omega_0$              | 1.25 MHz                  | 1.13 MHz                  | 1.19 MHz                  |

|                      | Magnitude <sub>BP</sub> | 5.91 dB                   | 4.66 dB                   | 5.23 dB                   |

| $I_{con} = 25 \mu A$ | Magnitude <sub>LP</sub> | 74.05 dBΩ                 | 73.84 dBΩ                 | 73.94 dBΩ                 |

|                      | $\omega_0$              | 1.55 MHz                  | $1.40~\mathrm{MHz}$       | 1.48 MHz                  |

|                      | Magnitude <sub>BP</sub> | 7.11 dB                   | 5.70 dB                   | 6.36 dB                   |

| $I_{con} = 50 \mu A$ | Magnitude <sub>LP</sub> | 73.94 dBΩ                 | 73.73 dBΩ                 | 73.83 dBΩ                 |

|                      | $\omega_0$              | 1.70 MHz                  | 1.52 MHz                  | 1.61 MHz                  |

**Table 2.** PVT and Monte Carlo simulation results for the magnitude of the filters and their  $\omega_0$ .

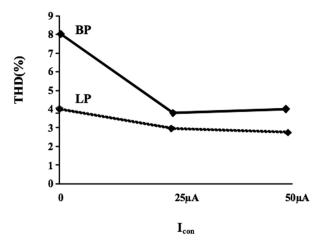

The linearity performance of the proposed circuit was checked for different values of  $I_{con}$  at  $\omega_0.$  The peak-to-peak values of  $V_{in}$  and  $I_{in}$  were 100 mV and 40  $\mu A$ , respectively. The resulting THD is reported in Figure 9. As can be seen, the maximum value of THD remained below 4% and 8% for the LP and BP outputs, respectively.

Figure 9. The simulated THD for LP and BP outputs.

Electronics 2022, 11, 646 9 of 11

Figure 10. Time domain output for the low-pass configuration.

Figure 11. Time domain output for the band-pass configuration.

Table 3 shows a comparison between the proposed circuit and others reported in the literature. As can be seen, the structures proposed in [1,3,13–17] provide output signal in current form, and therefore they are not suitable for applications requiring output signal in voltage form. In addition, the circuit of [3] requires an additional current buffer for practical use. The circuit reported in [10] produces output signal in voltage form; however, it needs extra voltage buffer at the output. Similarly, additional voltage buffer is necessary for the circuits presented in [17,19]. The circuits in [20,21] are not electronically tunable, and they suffer from a high supply voltage requirement. The VCII-based topology of [29] provides BP and LP outputs at the low-impedance Z port of VCII. Unfortunately, it is not electronically tunable. In contrast to other works, the proposed VCII-based circuit is electronically tunable, and does not require additional voltage buffers at the output node. More importantly, by taking advantage of the internal impedance at the Y port, the number of passive components is reduced.

Electronics **2022**, 11, 646

| Ref      | ABB    | #of |   | Electronic<br>Tunability | Outputs | V <sub>DD</sub> -V <sub>SS</sub>                                                                                    | Power<br>Dissipation  | Extra<br>VB/CB |     |

|----------|--------|-----|---|--------------------------|---------|---------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|-----|

|          |        | ABB | R | C                        |         |                                                                                                                     |                       |                |     |

| [1]      | CF     | 1   | 2 | 2                        | No      | $I_{LP}$ , $I_{HP}$ , $I_{BP}$                                                                                      | NA                    | NA             | No  |

| [3]      | CF     | 1   | 4 | 2                        | No      | $I_{AP}$ , $I_{notch}$                                                                                              | NA                    | NA             | Yes |

| [10]     | CCII   | 1   | 2 | 2                        | No      | $V_{BP}, V_{HP}, V_{LP}$                                                                                            | $\pm 0.75~\mathrm{V}$ | NA             | Yes |

| [13]     | CDTA   | 2   | 0 | 2                        | yes     | $I_{BP}$ , $I_{LP}$ , $I_{HP}$                                                                                      | $\pm 2.5 \text{ V}$   | 870 μW         | No  |

| [15]     | VDCC   | 1   | 1 | 2                        | No      | $I_{\mathrm{LP}}, I_{\mathrm{BP}}, I_{\mathrm{HP}}, \ I_{\mathrm{BS}}, I_{\mathrm{AP}}$                             | ±0.9 V                | NA             | No  |

| [16]     | FDCCII | 1   | 2 | 2                        | No      | $I_{\mathrm{LP}}, I_{\mathrm{BP}}, I_{\mathrm{HP}}, \ I_{\mathrm{BS}}, I_{\mathrm{AP}}$                             | $\pm 1.65~\mathrm{V}$ | 2.28 mW        | No  |

| [17]     | DVCC   | 3   | 3 | 2                        | No      | $egin{aligned} \mathbf{V_{LP}}, \mathbf{V_{BP}}, \mathbf{V_{HP}}, \ \mathbf{V_{BR}}, \mathbf{V_{AP}} \end{aligned}$ | ±0.9 V                | NA             | Yes |

| [18]     | CCCTA  | 3   | 0 | 2                        | yes     | $I_{HP}$ , $I_{LP}$ , $I_{BP}$                                                                                      | $\pm 1.85~\mathrm{V}$ | NA             | No  |

| [19]     | CFOA   | 1   | 3 | 2                        | No      | $V_{BP}$ , $V_{LP}$                                                                                                 | NA                    | NA             | Yes |

| [20]     | CDBA   | 3   | 5 | 2                        | No      | $V_{HP}, V_{BP}, V_{LP}$                                                                                            | $\pm 1.25~\mathrm{V}$ | NA             | No  |

| [21]     | CDBA   | 3   | 3 | 2                        | No      | $V_{HP}$ , $V_{BP}$ , $V_{LP}$                                                                                      | $\pm 5 \text{ V}$     | NA             | No  |

| [29]     | VCII   | 1   | 2 | 2                        | No      | $V_{BP}, V_{LP}$                                                                                                    | $\pm 1.65~\mathrm{V}$ | 700 μW         | No  |

| Proposed | VCII   | 1   | 1 | 2                        | yes     | $V_{BP}$ , $V_{LP}$                                                                                                 | $\pm 0.9~\mathrm{V}$  | 244–515 μW     | No  |

**Table 3.** Comparison between the proposed circuit and other reported works.

#### 6. Conclusions

In this paper, a new realization of an electronically tunable second-order LP/BP filter using VCII $^-$  with the property of electronically tunable impedance at the Y port is presented. The proposed circuit consists of one VCII $^-$ , two capacitors, and one resistor. The output signal is in voltage form provided at the low-impedance Z port of the VCII, which makes it unnecessary to use extra voltage buffer in practical applications. The  $\omega_0$  of the proposed transfer functions can be tuned using a control current (I\_{con}), by means of which the impedance at the Y port of VCII can be varied. Therefore, the number of passive resistors used is also reduced, resulting in a simpler circuit and a reduced chip area. A non-ideal analysis is provided. Spice simulation results are reported to show the functionality of the proposed structure.

**Author Contributions:** Conceptualization, L.S.; Formal analysis, L.S.; Methodology, G.F.; Project administration, G.F. and V.S.; Resources, V.S.; Supervision, G.F. and V.S.; Visualization, G.B. and M.R.; Writing—original draft, L.S.; Writing—review & editing, G.B., G.F. and V.S. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported in part by the Italian Ministry of Education, University and Research (MIUR) with the research grant "ASSIOMI", "PON R&I 2014–2020".

**Institutional Review Board Statement:** Not applicable.

Informed Consent Statement: Not applicable.

**Data Availability Statement:** Data sharing not applicable. No new data were created or analyzed in this study. Data sharing is not applicable to this article.

Conflicts of Interest: The authors declare no conflict of interest.

### References

- 1. Sharma, A.; Maheshwari, S. Current follower based current mode filters. In Proceedings of the 2020 Third International Conference on Smart Systems and Inventive Technology (ICSSIT), Tirunelveli, India, 20–22 August 2020; pp. 632–636.

- 2. Arora, T.S. Realization of current-mode universal filter utilising minimum active elements and only grounded passive components. In Proceedings of the 2020 7th International Conference on Signal Processing and Integrated Networks (SPIN), Noida, India, 27–28 February 2020; pp. 681–686.

- 3. Ergun, E.; Ulutas, M. Low input impedance current-mode allpass and notch filter employing single current follower. In Proceedings of the 2007 14th International Conference on Mixed Design of Integrated Circuits and Systems, Ciechocinek, Poland, 21–23 June 2007; pp. 638–640.

Electronics **2022**, 11, 646

4. Safari, L.; Barile, G.; Stornelli, V.; Ferri, G.; Leoni, A. New current mode wheatstone bridge topologies with intrinsic linearity. In Proceedings of the 2018 14th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Prague, Czech Republic, 2–5 July 2018; pp. 9–12.

- 5. Safari, L.; Barile, G.; Stornelli, V.; Ferri, G. A New Versatile Full Wave Rectifier Using Voltage Conveyors. *AEU—Int. J. Electron. Commun.* **2020**, *122*, 153267. [CrossRef]

- 6. Prommee, P.; Somdunyakanok, M.; Toomsawasdi, S. CMOS-based current-controlled DDCC and its applications. In Proceedings of the 2010 IEEE International Symposium on Circuits and Systems, Paris, France, 30 May–2 June 2010; pp. 1045–1048.

- 7. Barile, G.; Safari, L.; Ferri, G.; Stornelli, V. A VCII-Based Stray Insensitive Analog Interface for Differential Capacitance Sensors. Sensors 2019, 19, 3545. [CrossRef] [PubMed]

- 8. Sedra, A.; Smith, K. A Second-Generation Current Conveyor and Its Applications. *IEEE Trans. Circuit Theory* **1970**, 17, 132–134. [CrossRef]

- 9. Alzaher, H.A.; Elwan, H.; Ismail, M. A CMOS Fully Balanced Second-Generation Current Conveyor. *IEEE Trans. Circuits Syst. II Analog. Digit. Signal Processing* **2003**, *50*, 278–287. [CrossRef]

- 10. Parveen, T.; Rajput, S.S.; Ahmad, M.T. Low Voltage CCII-based High Performance Cascadable Multifunctional Filter. *Microelectron. Int.* **2006**, 23, 28–31. [CrossRef]

- 11. Bhaskar, D.R.; Raj, A.; Kumar, P. Mixed-Mode Universal Biquad Filter Using OTAs. *J. Circuit Syst. Comput.* **2020**, 29, 2050162. [CrossRef]

- 12. Budboonchu, J.; Tangsrirat, W. Three-input single-output current-mode universal filter using single CCCTA. In Proceedings of the 2017 9th International Conference on Information Technology and Electrical Engineering (ICITEE), Phuket, Thailand, 12–13 October 2017; pp. 1–4.

- Duangmalai, D.; Jaikla, W. Resistorless current-mode universal filter using current differencing cascaded transconductance amplifiers. In Proceedings of the 2018 3rd International Conference on Control and Robotics Engineering (ICCRE), Nagoya, Japan, 20–23 April 2018; pp. 188–191.

- 14. Stornelli, V.; Pantoli, L.; Leuzzi, G.; Ferri, G. Fully Differential DDA-Based Fifth and Seventh Order Bessel Low Pass Filters and Buffers for DCR Radio Systems. *Analog Integr. Circuits Signal Process.* **2013**, 75, 305–310. [CrossRef]

- 15. Lamun, P.; Phatsornsiri, P.; Torteanchai, U. Single VDCC-based current-mode universal biquadratic filter. In Proceedings of the 2015 7th International Conference on Information Technology and Electrical Engineering (ICITEE), Chiang Mai, Thailand, 29–30 October 2015; pp. 122–125.

- 16. Torteanchai, U.; Kumngern, M. Three-input single-output current-mode universal filter using a single FDCCII and grounded passive components. In Proceedings of the 2014 International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS), Kuching, Malaysia, 1–4 December 2014; pp. 275–278.

- 17. Chen, H.-P. Tunable Versatile Current-Mode Universal Filter Based on plus-Type DVCCs. *AEUE—Int. J. Electron. Commun.* **2012**, 4, 332–339. [CrossRef]

- 18. Singh, S.; Maheshwari, S.; Mohan, J.; Chauhan, D.S. Electronically tunable current-mode universal biquad filter based on the CCCCTA. In Proceedings of the 2009 International Conference on Advances in Recent Technologies in Communication and Computing, Kottayam, India, 27–28 October 2009; pp. 424–429.

- 19. Horng, J.W.; Chou, P.-Y.; Wu, J.-Y. Voltage/Current-Mode Multifunction Filters Using Current-Feedback Amplifiers and Grounded Capacitors. *Act. Passiv. Electron. Compon.* **2010**, 2010, e785631. [CrossRef]

- 20. Arora, T.S.; Rana, U. Multifunction Filter Employing Current Differencing Buffered Amplifier. *Circuits Syst.* **2016**, *7*, 543–550. [CrossRef]

- 21. Sagbas, M.; Koksal, M. A New multi-mode multifunction filter using CDBA. In Proceedings of the 2005 European Conference on Circuit Theory and Design, Cork, Ireland, 2 September 2005; Volume 2, pp. II/225–II/228.

- 22. Safari, L.; Barile, G.; Stornelli, V.; Ferri, G. An Overview on the Second Generation Voltage Conveyor: Features, Design and Applications. *IEEE Trans. Circuits Syst. II: Express Briefs* **2019**, *66*, 547–551. [CrossRef]

- 23. Čajka, J.; Vrba, K. The Voltage Conveyor May Have in Fact Found Its Way into Circuit Theory. *AEU—Int. J. Electron. Commun.* **2004**, *58*, 244–248. [CrossRef]

- 24. Barile, G.; Safari, L.; Ferri, G.; Stornelli, V. Traditional Op-Amp and New VCII: A Comparison on Analog Circuits Applications. *AEU—Int. J. Electron. Commun.* **2019**, *110*, 152845. [CrossRef]

- 25. Pantoli, L.; Barile, G.; Leoni, A.; Muttillo, M.; Stornelli, V. Electronic Interface for Lidar System and Smart Cities Applications. *J. Commun. Softw. Syst.* **2019**, *15*, 118–125. [CrossRef]

- 26. Al-Absi, M. Realization of inverse filters using second generation voltage conveyor (VCII). *Analog Integr. Circuits Signal Process.* **2021**, *109*, 29–32. [CrossRef]

- 27. Stornelli, V.; Safari, L.; Barile, G.; Ferri, G. A New Extremely Low Power Temperature Insensitive Electronically Tunable VCII-Based Grounded Capacitance Multiplier. *IEEE Trans. Circuits Syst. II: Express Briefs* **2021**, *68*, 72–76. [CrossRef]

- 28. Stornelli, V.; Ferri, G. A 0.18μm CMOS DDCCII for Portable LV-LP Filters. Radioengineering 2013, 22, 434–439.

- 29. Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. High Performance Voltage Output Filter Realizations Using Second Generation Voltage Conveyor. *Int. J. RF Microw. Comput.-Aided Eng.* **2018**, 28, e21534. [CrossRef]