Article

# Interface Contact Thermal Resistance of Die Attach in High-Power Laser Diode Packages

Liting Deng  $^{1,2}$ , Te Li  $^{1,*}$ , Zhenfu Wang  $^{1}$ , Pu Zhang  $^{1}$ , Shunhua Wu  $^{1,2}$ , Jiachen Liu  $^{1,2}$ , Junyue Zhang  $^{1,2}$ , Lang Chen  $^{1}$ , Jiachen Zhang  $^{1}$ , Weizhou Huang  $^{1,2}$  and Rui Zhang  $^{1}$

- State Key Laboratory of Transient Optics and Photonics, Xi'an Institute of Optics and Precision Mechanics, Chinese Academy of Sciences, Xi'an 710119, China; dengliting@opt.ac.cn (L.D.); wzf2718@opt.ac.cn (Z.W.); zhangpu@opt.ac.cn (P.Z.); wushunhua@opt.ac.cn (S.W.); liujiachen@opt.ac.cn (J.L.); zhangjunyue@opt.ac.cn (J.Z.); chenlang@opt.ac.cn (L.C.); zhangjiachen@opt.ac.cn (J.Z.); huangweizhou2022@opt.ac.cn (W.H.); zhangrui2022@opt.ac.cn (R.Z.)

- <sup>2</sup> University of Chinese Academy of Sciences, Beijing 100049, China

- \* Correspondence: lite@opt.ac.cn

**Abstract:** The reliability of packaged laser diodes is heavily dependent on the quality of the die attach. Even a small void or delamination may result in a sudden increase in junction temperature, eventually leading to failure of the operation. The contact thermal resistance at the interface between the die attach and the heat sink plays a critical role in thermal management of high-power laser diode packages. This paper focuses on the investigation of interface contact thermal resistance of the die attach using thermal transient analysis. The structure function of the heat flow path in the T3ster thermal resistance testing experiment is utilized. By analyzing the structure function of the transient thermal characteristics, it was determined that interface thermal resistance between the chip and solder was 0.38 K/W, while the resistance between solder and heat sink was 0.36 K/W. The simulation and measurement results showed excellent agreement, indicating that it is possible to accurately predict the interface contact area of the die attach in the F-mount packaged single emitter laser diode. Additionally, the proportion of interface contact thermal resistance in the total package thermal resistance can be used to evaluate the quality of the die attach.

**Keywords:** die attach; interface contact thermal resistance; thermal management; transient thermal analysis; structure function; high-power laser diode

Citation: Deng, L.; Li, T.; Wang, Z.; Zhang, P.; Wu, S.; Liu, J.; Zhang, J.; Chen, L.; Zhang, J.; Huang, W.; et al. Interface Contact Thermal Resistance of Die Attach in High-Power Laser Diode Packages. *Electronics* **2024**, *13*, 203. https://doi.org/10.3390/electronics13010203

Academic Editor: Nakkeeran Kaliyaperumal

Received: 1 December 2023 Revised: 22 December 2023 Accepted: 25 December 2023 Published: 2 January 2024

Copyright: © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

High-power laser diodes have been widely used for solid-state laser pumping, as well as a direct high-power light source for industrial, research, and medical applications [1,2]. With the development of laser diodes, the requirement for power has continued to increase and the heat in the die has been generated. According to statistics, the failure of electronic devices caused by excessive temperature currently accounts for approximately 55%, being a major reason for electronic device failure [3]. Therefore, it is evident that thermal effects have become an issue that cannot be ignored in the development of high-power laser diodes, and effective removal of heat in order to maintain a safe junction temperature is the key to thermal management of high-power laser diode packages.

Thermal management is crucial for high-power laser diodes. With the development of laser diodes, electro-optical conversion efficiency can increase to 50~70%, but there is still 30~50% of electrical energy being converted into thermal energy. High-power laser diode chips have a small size and high output power, resulting in a great heat flux density during operation. For instance, when the thermal load power of a single emitter chip increases to 10 W, the internal heat flux density will exceed to 1500 W/cm², which is equivalent to the magnitude of heat flux density on the surface of the sun [4]. If such a high heat flux density cannot be efficiently dissipated, the junction temperature will rapidly increase. The

rising chip temperature significantly affects the performance of the laser diodes, leading to degradation of lifetime and electro-optical efficiency, as well as an increase in threshold current and wavelength redshift. Therefore, thermal management is vital to maintain a safe junction temperature during the operation for high-power laser diodes.

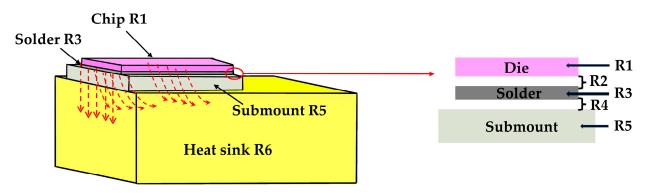

Thermal resistance is the primary parameter for evaluating thermal management of electronic devices [5]. Packaging technology is the post-processing technique for fabrication of laser diodes, which mainly includes heat sink design, solder preparation, sintering, and bonding. Sintering involves soldering the chip onto the heat sink, while bonding entails connecting electrode leads from the chip to the heat sink, typically using gold wires with a diameter of 30 um to form the current path. To enhance heat dissipation performance, the laser chip is epi-down mounted onto a substrate, which is the p-side connection. The packaging thermal resistance of high-power laser diodes is composed of chip thermal resistance R1, interface contact thermal resistance between chip and solder R2, solder thermal resistance R3, interface thermal resistance between solder and submount R4, submount thermal resistance R5, and heat sink thermal resistance R6, as Figure 1 shows. Analyzing the package thermal resistance is of great significance for better thermal management of high-power laser diodes.

**Figure 1.** Schematic diagram of high-power laser diode package thermal resistance.

Thermal management has a vital impact on the thermal performance of high-power laser diodes, making the evaluation of precise thermal resistance essential. It should be noted that numerous studies on the thermal characteristic of laser diode packages have been conducted by other research groups. For instance, Wipiejewski. T et al. measured the thermal resistance of vertical-cavity laser diodes by comparing the emission wavelength shift versus dissipated power to the wavelength shift as ambient temperature was changed [6]. Chang. J et al. researched the effect of solder void size and location on the thermal resistance of power devices using three-dimensional (3-D) finite element modeling [7]. Maciej. Kuc and Otiaba. KC et al. focused on thermal analysis of the size of the diamond heat sink and on the thickness of the solder [8,9]. Ma. X et al. studied the relationship between chip size and thermal resistance of the C-mount packaged single emitter diode laser through a wavelength shift experiment [10]. Ni. Y et al. investigated the heat dissipating performance of laser diodes packaged by silicon carbide (SiC) ceramic submount, compared with aluminum nitride (AlN) ceramic submount. The thermal resistance was measured using the structure function method [11].

Although the aforementioned studies provide vital information on the package thermal resistance of laser diodes, they were more concentrated on the impact of chip size, solder void, heat sink, and submount materials on thermal resistance [6–11]. There are few papers researching the influence of interface between the chip and solder or solder and heat sink on package thermal resistance in high-power laser diodes. Previous research [6,10] mostly measured the overall thermal resistance between the heat-generating chip and heat-dissipating heat sink using the wavelength shift experiment, which could not obtain the thermal resistance of each layer in the laser diodes' packaged structure. Thus, more studies are needed for an in-depth understanding of the precise measurement of interface

thermal resistance in the die attach for package thermal management. This article firstly utilizes the finite element method (FEM) to conduct steady-state thermal characteristic simulations on F-mount packaged high-power single emitter laser diodes, analyzing the mechanism of interface thermal resistance which affects the thermal properties of the chip, and then, measures the interface thermal resistance using T3ster thermal resistance testing measurement. Finally, combining the results of measurement with simulation, we can forecast and estimate the interface contact area and package quality of single emitter laser diodes in the real working environment. These findings have great reference significance for further improving the reliability and performance stability of high-power laser diodes.

#### 2. Materials and Methods

#### 2.1. Simulation of F-Mount Packaged Single Emitter

Interface contact thermal resistance of the die attach is crucial for the thermal management of high-power laser diodes. At present, Indium solder and Gold-Tin solder are commonly used in laser diode packages. In the die attach process, the laser chip is epidown mounted onto the submount, and the liquid AuSn alloy will flow and fill the burrs on the surface of the chip metal layer or heat sink layer when the soldering temperature increases to 320 °C [12]. However, due to the poor flatness of the heat sink's surface, large particles produced during the chip metallization, impurities in solder, pressure applied during sintering and poor wettability of the die attach, gaps, and voids may form at the contact interface. When thermal flow passes through the interface, incomplete contact of the interface results in a sudden decrease in the heat transfer channel, leading to the shrinkage of thermal flow, thus causing significant temperature difference and interface thermal resistance between the chip or heat sink and solder. Interface contact thermal resistance is related to the roughness of the interface and the interface contact area. Generally, to ensure that the laser diode can operate normally, the wettability of the solder should not be too poor. Hence, in the following simulation, we analyze the impact of contact interface area of 80%, 85%, and 90% on interface contact thermal resistance in the die attach of high-power laser diode packages.

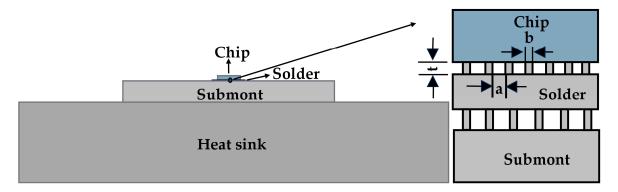

To investigate interface thermal resistance and the interface contact state in the die attach, we establish a calculation model and a finite element calculation format based on the multi-point contact model. From a microscopic perspective, the actual contact interface is composed of numerous randomly distributed micro-protrusions with various shapes. When conducting finite element simulations, directly adopting this random surface model would result in a significant increase in computational scale and workload, potentially reaching an unacceptable level. In order to better simulate the actual contact interface of laser diodes, we use regular micro-protrusions with the same characteristic parameters, such as cuboids, cylinders, frustums, spheres, etc., to approximate random rough surfaces. In terms of rapidity and feasibility of calculation, using cuboids or cylinders is more convenient. Moreover, it can better match the measurement results of the surface roughness of the structure (for example, the height of a convex rectangle can be determined by the surface roughness parameter Ra) [13]. Additionally, due to the small size of the microcontact, the computational workload would be very large if threedimensional modeling were conducted. The increase in computational accuracy would be insignificant compared to a two-dimensional model. Therefore, this study adopts a two-dimensional plane model to simulate the contact interface. The microcontacts on the interface are approximated by multiple rectangular protrusions with a periodic distribution, as Figure 2 shows.

Figure 2 shows the main structural parameters of the calculation model, including the height t, width b, and the gap width a of the rectangular convex body, in addition to the actual size of the chip, solder, and heat sink. The determination methods for these parameters are as follows: the contact between two rough surfaces is equivalent to the contact between a completely smooth surface and a rough surface. The height t of the contact protrusions is taken as the average of the surface roughness (Ra1 and Ra2) of

Electronics **2024**, 13, 203 4 of 14

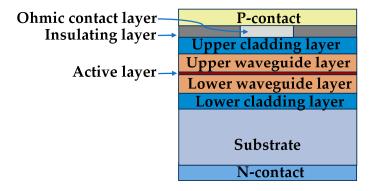

the two interfaces. The gap width depends on the contact area between the solder and the chip or heat sink. During the Ansys finite element simulation, in order to facilitate analysis and calculation, it is common to model the chip and its internal structure using a simplified rectangular stack structure [14–17]. The research object of this study is the F-mount packaged single emitter diode laser with a cavity length of 2 mm. Figure 3 shows the schematic diagram of the single emitter epitaxial structure. Table 1 presents the specific parameters of the finite element computational model.

Figure 2. Computational model of the thermal contact resistance based on multipoint contact model.

Figure 3. Schematic diagram of single emitter epitaxial structure.

|           | Layer                 | Material                          | $W \times L \times H$ (mm)     | Thermal Conductivity<br>(W/m·K) |  |

|-----------|-----------------------|-----------------------------------|--------------------------------|---------------------------------|--|

|           | N-contact             | Au                                | $0.5 \times 2 \times 0.0007$   | 315                             |  |

|           | Substrate             | GaAs                              | $0.5 \times 2 \times 0.1$      | 46                              |  |

|           | Lower cladding layer  | Al <sub>0.5</sub> GaAs            | $0.5 \times 2 \times 0.0011$   | 11                              |  |

|           | Lower waveguide layer | $Al_{0.33}GaAs$                   | $0.5 \times 2 \times 0.0006$   | 12.04                           |  |

| D.        | Active layer          | $Al_{0.12}Ga_{0.795}In_{0.085}As$ | $0.5 \times 2 \times 0.000008$ | 4                               |  |

| Die       | Upper waveguide layer | Al <sub>0,33</sub> GaAs           | $0.5 \times 2 \times 0.0004$   | 12.04                           |  |

|           | Upper cladding layer  | Al <sub>0.5</sub> GaAs            | $0.5 \times 2 \times 0.0011$   | 11                              |  |

|           | Insulating layer      | SiO <sub>2</sub>                  | $0.2\times2\times0.00015$      | 46                              |  |

|           | Ohmic contact layer   | GaAs                              | $0.15 \times 2 \times 0.00015$ | 1.28                            |  |

|           | P-contact             | Au                                | $0.5 \times 2 \times 0.0004$   | 315                             |  |

| Solder    |                       | AuSn                              | $0.9\times4.75\times0.005$     | 57                              |  |

| Submount  |                       | AlN                               | $5 \times 4.75 \times 0.4$     | 120                             |  |

| Heat sink |                       | Cu                                | $14 \times 5.25 \times 2.5$    | 398                             |  |

In this section, we conducted steady-state thermal simulation calculation for interface thermal resistance of the die attach, utilizing the multipoint contact thermal resistance calculation model established in the previous section. Regarding the numerical model, we Electronics **2024**, 13, 203 5 of 14

made some reasonable assumptions. Firstly, we assume that all heat power is concentrated in the active layer during the operation of the laser diode [18,19]. Subsequently, the chip surface, as well as the sides of the thermal sink, are considered adiabatic [20], and the heat dissipation capacity at the bottom of the heat sink is assumed to be infinite. In the simulation calculation, the governing equation for the steady-state temperature field we employ is  $\nabla^2 T + \frac{q_v}{\lambda} = 0$  (where  $\nabla$  is the Laplace operator,  $\lambda$  is the thermal conductivity, and  $q_v$  is the internal heat source). The corresponding boundary conditions are  $T = \overline{T}$  (in the  $\partial \Omega_1$ ) and  $n \cdot q = \overline{q}$  (in the  $\partial \Omega_2$ ). The surface roughness of the chip P-side gold layer and the solder were measured to be 0.8 um and 0.25 um, respectively, while the AlN heat sink exhibited a surface roughness of 0.5 um. Considering that the height of the contact protrusions is the average of the surface roughness values Ra1 and Ra2 of the two interfaces, the height at the chip—solder interface was determined to be 0.525 um, with a width of 0.5 um. Similarly, the height of the contact protrusions at the solder—heat sink interface was calculated to be 0.375 um, with a width of 0.5 um.

For the simulation, we first set the initial contact area between the chip and solder, as well as between the solder and heat sink interfaces, to be 80%. The thermal boundary condition applied in the simulation model involved a thermal power density of  $1.11\times10^{15}\,\rm W/m^3$  in the active layer and a constant temperature boundary condition of 22 °C at the bottom of the heat sink. These parameters were crucial in the simulation setup, ensuring accurate representation of the thermal behavior at the interfaces. The simulation results will provide valuable insights into the interface thermal resistance and contribute significantly to the advancement of our understanding in this field.

### 2.2. Experiment of F-Mount Packaged Single Emitter

#### 2.2.1. T3ster Interface Contact Thermal Resistance Testing

The most widely used method for measuring the chip temperature of high-power laser diodes is the junction voltage measurement method, also known as the forward voltage method. This approach relies on the nearly linear relationship between the temperature of the junction temperature region and the forward voltage, making it a reliable technique for temperature estimation [21,22]. The chip's active region temperature can be deduced by measuring the voltage of the laser diode. However, due to the variations in laser diode types and manufacturing processes, this linear relationship needs to be calibrated in advance using a low current method. In this method, the laser diode operates under a current from the working current source for a sufficiently long duration (typically 600 s), ensuring a steady-state operational regime. The laser diode is then switched from the working state to the measuring state to measure the forward voltage. This method has been validated by Liu et al., confirming that the temperature change over time under cooling conditions has a complementary relationship with that under heating conditions [23]. Therefore, by mathematically inverting the transient cooling curve, the transient temperature rise curve can be derived. Due to its simplicity and effectiveness, this method is commonly utilized for temperature measurement in high-power semiconductor lasers (LED, IGBT etc.) [24–26].

The utilization of the structure function theory was introduced as an enhancement to the junction voltage thermometry method, enabling fast calculation of the device package thermal resistance. In 1997, V. Szekely et al. pioneered the application of the structure function in thermal analysis based on the Cauer network model [27]. This approach involved measuring the transient thermal response curves of the device during heating or cooling, from which parameters related to the thermal resistance and thermal capacitance were extracted [28]. By discerning the physical differences among different material layers, crucial parameters such as thermal resistance and heat capacity could be acquired, particularly at the interfaces between material layers. The structure functions serve as a tool to map the cumulative thermal capacitances of the heat flow path in relation to the thermal resistances, extending from the junction to the ambient environment. By examining the derivative of this function, the differential structure is represented as a function of cumulative thermal resistance. Notably, local peaks and valleys in these functions indicate transitions to new

Electronics **2024**, 13, 203 6 of 14

materials or changes in surface areas within the heat flow path, offering valuable insight into the thermal behavior and material transitions within the package.

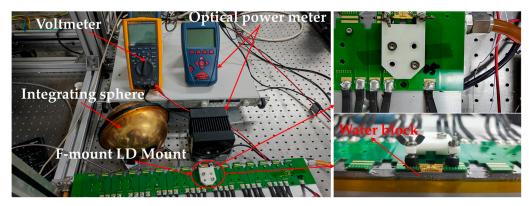

In this experiment, we determined the transient thermal response curve of a single emitter using the commercial T3ster transient thermal tester (SIMUCAD Info Tech Co., Ltd., Shanghai, China), which offers a remarkable time resolution of 1 us and a high-temperature measurement accuracy of 0.01 °C. The experimental subjects consisted of two F-mount packaged single emitter laser diodes, each with a cavity length of 2 mm, as Figure 4 depicts. Initially, the single emitters were placed directly on a cold plate for testing, allowing us to observe the cumulative structure function. Subsequently, thermal grease was applied on the cold plate, and the transient response curve was measured under the same conditions as the first test to obtain the structure function. In the laboratory setup, the LD heating current was maintained at 3 A, with a heating duration of 80 s and a test current of 20 mA. The temperature of the cooling plate was precisely controlled at 20 °C using a Peltier-based temperature controller. This meticulous experimental procedure ensured accurate measurements and reliable data for the analysis of the thermal behavior of the single emitter laser diodes.

Figure 4. Schematic diagram of two F-mount packaged single emitter laser diodes.

## 2.2.2. CW Power-Averaged Wavelength Measurement of the Overall Thermal Resistance

The interface contact thermal resistance of the die attach is one crucial parameter of thermal management in high-power laser diode packages. However, there has been relatively limited research conducted on interface thermal resistance of solders in high-power laser diode packages. Both simulation and experimental fields in this area remain largely unexplored. This paper aims to quantitatively measure interface contact thermal resistance utilizing the T3ster thermal resistance testing experiment. To enhance the credibility and accuracy of this experimental data, we also performed a wavelength shift experiment to measure the thermal resistance of an F-mount packaged single emitter diode laser.

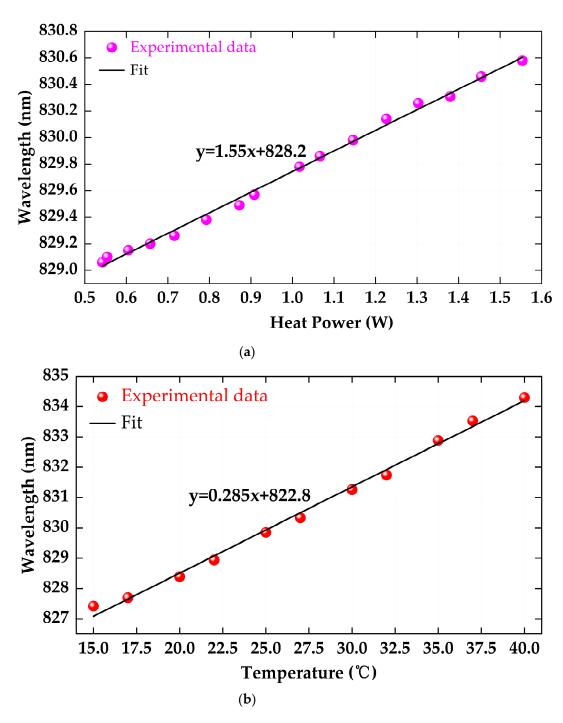

This method is based on the wavelength change under continuous wave (*CW*) operation of an F-mount packaged single emitter [29]. Figure 5 shows the setting up of the experimental equipment. Figure 6a shows data obtained by measuring the wavelength vs. heat sink temperature with a constant drive current of 1.4 A, revealing a wavelength heat coefficient of 1.55 nm/W. Figure 6b shows the measurement results of power-averaged wavelength vs. heat power with a heat sink temperature of 20 °C, indicating wavelength shifts of 0.285 nm/K toward longer wavelengths. By using equation  $R = (\Delta \lambda/\Delta P)/(\Delta \lambda/\Delta T)$ , the thermal resistance of the laser diode was calculated to be 5.4 K/W.

Figure 5. Test setup for power-averaged wavelength measurement.

Electronics **2024**, 13, 203 7 of 14

**Figure 6.** Measured results of wavelength shift method: (a) Wavelength varies with heat power of the single emitter; (b) Wavelength varies with temperature of the single emitter.

#### 3. Results

## 3.1. Simulation of the Interface Contact Thermal Resistance

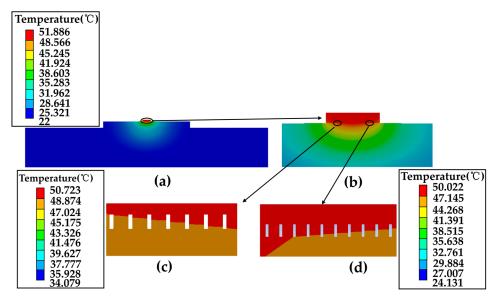

Figure 7 illustrates the case of an interface contact area setting at 80%, the temperature distribution contour plot for the overall structure, and the local contact protrusions. Figure 4 shows that due to the presence of interface contact thermal resistance, there are significant temperature disparities on both sides of the chip—solder contact interface and the solder—heat sink contact interface. Specifically, the temperature difference at the chip—solder interface contact measures 1.8 °C, while at the solder—heat sink interface contact, it amounts to 2.8 °C. The interface thermal resistance between the solder layer and the chip or heat sink of a given material and thickness is profoundly influenced by the wettability of the solder

layer between the chip and the heat sink. Consequently, this study delves into the impact of the contact area between the solder layer and the chip or heat sink on the interface thermal resistance and thermal performance. To investigate this, the contact area of the die attach is varied at 80%, 85%, 90%, respectively. Table 2 outlines the different contact areas of the interface thermal resistance in the simulation.

**Figure 7.** Temperature field of the computational model: (a) The overall structure; (b) The local contact protrusions; (c) Interface of the chip and solder; (d) Interface of the solder and heat sink.

**Table 2.** Thermal resistance of each layer for single emitter in simulation.

| Thermal Resistance (K/W) |     |      |      |        |      |          |           |                   |

|--------------------------|-----|------|------|--------|------|----------|-----------|-------------------|

|                          |     | Chip | R1   | Solder | R2   | Submount | Heat Sink | R <sub>thjc</sub> |

|                          | 80% | 0.41 | 0.47 | 0.42   | 0.55 | 0.81     | 0.57      | 3.23              |

| Simulation               | 85% | 0.37 | 0.40 | 0.50   | 0.49 | 0.77     | 0.45      | 2.98              |

|                          | 90% | 0.36 | 0.34 | 0.57   | 0.42 | 0.75     | 0.44      | 2.88              |

### 3.2. T3ster Interface Contact Thermal Resistance Testing

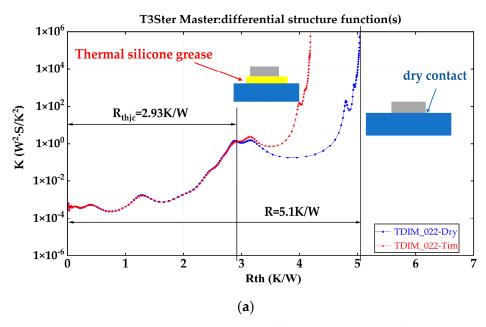

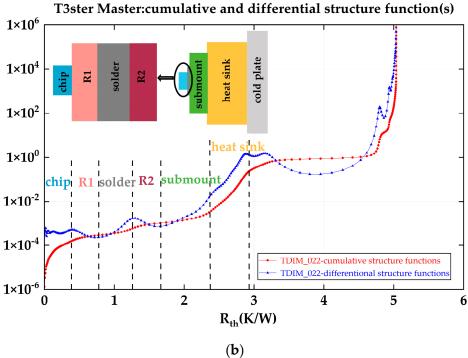

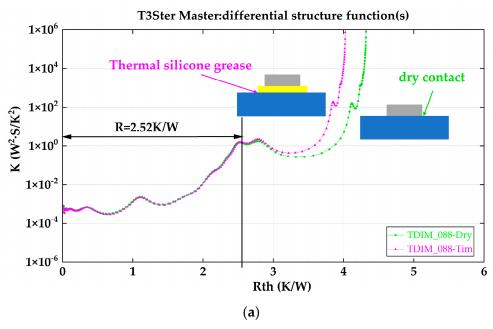

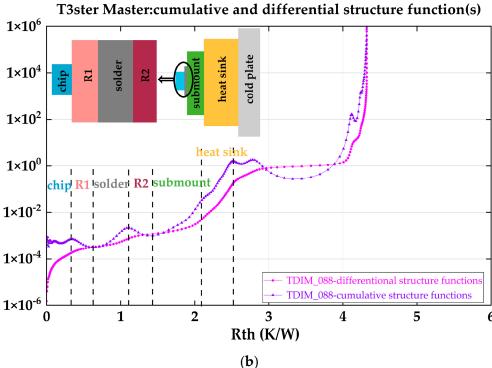

In this experiment, Figure 8a illustrates the cumulative structure functions of FL111022 under two distinct experimental conditions. The two curves exhibit exceptional repeatability up to 2.93 K/W. However, beyond 2.93 K/W, the curves diverge. This divergence occurs because the internal thermal resistance and thermal capacitance characteristics within the same single emitter lasers remain constant. However, once the heat flow reaches the backside of the heat sink, the structure functions separate due to the presence of different thermal conductive materials. By identifying the position of the separation point in the structure function, we can determine the overall thermal resistance from the chip to the heat sink of the single emitter, which amounts to  $R_{thjc} = 2.93 \text{ K/W}$ . For various laser diodes, it is challenging to ensure the consistency of voids, thickness uniformity, and wetting properties of the solder layer during the packaging process. Consequently, the thermal resistance of the solder layer or heat sink layer may vary. Figure 9a displays the cumulative structure functions of the single emitter FL112088, where the curve diverges after 2.52 K/W, indicating an overall thermal resistance of 2.52K/W. By delineating the region of slope change and the positions of peak-trough in the curve, different material layers can be classified, as Figures 8b and 9b illustrate. This classification enables the acquisition of the thermal resistance of each layer and the interface thermal resistance in the die attach, as Table 3 details. These findings provide valuable insights into the material characteristics and thermal behavior within the single emitter.

**Figure 8.** Measured cumulative and differential structure functions for FL111022 single emitter: (a) Differential structure functions with two interface contact conditions; (b) Structure functions with the dry contact of the single emitter.

Table 3. Thermal resistance of each layer for single emitter in the experiment.

| Thermal Resistance (K/W) |                      |                |               |               |              |                |              |                   |

|--------------------------|----------------------|----------------|---------------|---------------|--------------|----------------|--------------|-------------------|

|                          |                      | Chip           | R1            | Solder        | R2           | Submount       | Heat Sink    | R <sub>thjc</sub> |

| T3ster                   | FL111022<br>FL112088 | 0.386<br>0.331 | 0.381<br>0.33 | 0.525<br>0.42 | 0.36<br>0.35 | 0.761<br>0.689 | 0.511<br>0.4 | 2.93<br>2.52      |

**Figure 9.** Measured cumulative and differential structure functions for FL112088 single emitter: (a) Differential structure functions with two interface contact conditions; (b) Structure functions with the dry contact of the single emitter.

## 3.3. CW Power-Averaged Wavelength Measurement of the Overall Thermal Resistance

In the wavelength measurement, we calculate the overall thermal resistance of the laser diode to be  $5.4~\rm K/W$ . However, this value does not solely represent the thermal resistance from the chip to the heat sink. In this experimental setup, the single emitter is placed on a temperature-controlled fixture and dissipates heat through the water cooler, as Figure 8 shows. The entire heat dissipation path includes the water block, aligning with the heat dissipation path in the forward voltage method with dry contact, as Figure 6a depicts. Therefore, the thermal resistance measured by the wavelength drift method,  $R = 5.4~\rm K/W$ , is basically consistent with the thermal resistance measured by the forward

voltage method in the device's dry contact state (including the water block), which is  $R = 5.1 \ K/W$ , as Figure 6a shows. The slight difference in thermal resistance may arise from the slightly varied thermal resistance of the water block in the two experimental setups. This alignment demonstrates the accuracy and practicality of the forward voltage method and the structural function theory. It also underscores the effectiveness of using structural function analysis for evaluating interface thermal resistance in the die attach, showcasing it as a powerful experimental method.

#### 4. Discussion

Table 4 summarizes the consequence derived from T3ster testing and finite element simulation. Upon analyzing the simulation results, it becomes evident that the interface thermal resistance of the die attach gradually decreases as the interface contact area between the solder and chip or solder and heat sink increases. This phenomenon arises because a large interface contact area implies good wettability of the solder between the chip and heat sink, resulting in fewer voids on the surface between the chip or heat sink and solder. As a result, the temperature differential between different interfaces diminishes, leading to a reduction in thermal resistance. This reduction is advantageous for efficient heat dissipation.

| Thermal Resistance (K/W) |          |       |       |        |       |          |           |                   |

|--------------------------|----------|-------|-------|--------|-------|----------|-----------|-------------------|

|                          |          | Chip  | R1    | Solder | R2    | Submount | Heat Sink | R <sub>thjc</sub> |

| Tactor                   | FL111022 | 0.386 | 0.381 | 0.525  | 0.36  | 0.761    | 0.511     | 2.93              |

|                          | FL112088 | 0.331 | 0.33  | 0.42   | 0.35  | 0.689    | 0.4       | 2.52              |

| Simulation               | 80%      | 0.41  | 0.468 | 0.42   | 0.547 | 0.814    | 0.571     | 3.23              |

|                          | 85%      | 0.368 | 0.405 | 0.50   | 0.494 | 0.771    | 0.45      | 2.98              |

|                          | 90%      | 0.36  | 0.345 | 0.59   | 0.417 | 0.75     | 0.44      | 2.88              |

Table 4. Thermal resistance of each layer for single emitter between experiment and simulation.

Upon comparing the experimental results with the simulation data, it was found that when the contact area of the die attach is 90%, the error between the simulated interface thermal resistance and the experimental test is only 2.8%. Similarly, with a contact area of 85%, the error between the simulated junction to heat sink of thermal resistance and the experimental result is only 1.7%. The simulated interface thermal resistance aligns closely with the T3ster testing results, indicating that the optimal solder interface contact area for single emitters to operate and emit light properly and stably under actual working conditions is between 85% and 90%. This finding serves as a valuable prediction for the interface contact situation for high-power single emitter diode lasers.

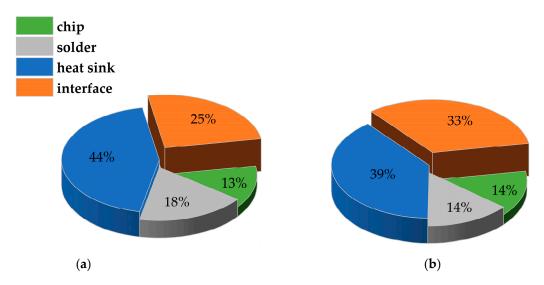

Figure 10 shows the distribution of simulated and experimental thermal resistance for each layer within the overall thermal resistance. The pie chart reveals that when the interface contact area is 80%, the simulation of the solder interface thermal resistance constitutes 33.4% of the total thermal resistance. In the T3ster testing experiment, the proportion of interface thermal resistance decreases to 25.3%. This clearly indicates that during actual packaging processes, the quality of the solder interface can be evaluated based on the proportion of interface thermal resistance of the die attach in the overall thermal resistance. For instance, poor wettability between the chip and solder (or solder and heat sink), or the presence of voids on the solder layer's surface result in higher corresponding interface thermal resistance. This, in turn, leads to a larger share in the total thermal resistance. Consequently, by optimizing specific parameters in the soldering process, such as enhancing solder uniformity and infiltration, both packaging quality and heat dissipation characteristics can be improved. Additionally, this optimization opens up the possibility of non-destructively detecting potential defects in the high-power laser diode packaging process.

**Figure 10.** Distribution of simulated and experimental values of thermal resistance for each layer: (a) T3ster testing for FL111022; (b) Simulation for contact area of 80%.

The consistency of simulated and measured results establishes the significance of interface contact thermal resistance of the die attach in thermal management of high-power laser diode packages. Furthermore, it is evident that the current single emitter diode laser packing structure and process are rational, and this detection technology has the potential to be applied for assessing the thermal resistance of laser diodes packaged with Indium solder in future work. Likewise, this technology could be utilized to identify possible defects, such as voids, in the laser diode package procedure. The discrepancy between the simulation and experiment of the interface thermal resistance between the solder and heat sink may be attributed to the configuration of the interface contact shape. This article provides a thorough analysis and validation of the impact of the interface contact area on interface thermal resistance and device thermal performance. However, it does not delve into the effect of altering the geometric shape of the contact area on the interface thermal resistance of the die attach. Therefore, future research can explore various geometric shapes and comprehensively analyze the interface thermal resistance of the die attach.

### 5. Conclusions

In this paper, we have investigated interface contact thermal resistance of the die attach in high-power F-mount packaged single emitter laser diodes. Through T3ster thermal resistance testing experiment, interface thermal resistance between the chip and solder of 0.38 K/W is determined, while the resistance between the solder and heat sink is 0.36 K/W. Finite element simulation revealed that the chip-solder interface thermal resistance is 0.345 K/W and the solder–heat sink interface thermal resistance is 0.417 K/W when the interface contact area is 90%. By comparing the simulation results with the T3ster testing results, we can predict that the interface contact area of a single emitter under actual operating conditions ranges from 85% to 90%. Additionally, by considering the proportion of interface thermal resistance in the overall thermal resistance, the quality of the die attach can be evaluated, defects in laser diode packages can be identified, and the subsequent packaging process can be optimized. This research also verifies the accuracy and practicality of T3ster thermal resistance testing experiments through CW power-averaged wavelength measurement, highlighting the effectiveness and convenience of using the forward voltage method and structural function analysis for interface thermal resistance assessment in high-power laser diode packages.

**Author Contributions:** Conceptualization, L.D. and T.L.; methodology, software, writing—original draft preparation, L.D.; writing—review and editing, T.L. and Z.W.; resources, P.Z. and S.W.; visualization, J.L. and J.Z. (Junyue Zhang); investigation, L.C. and J.Z. (Jiachen Zhang); data curation, W.H. and R.Z. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded by the National Natural Science Foundation of China, Grant Nos. 61504167 and 62075237; the Natural Science Foundation of Shaanxi Province, China, Grant Nos. 2023-JC-YB-556, 2022JQ-531, 2019ZY-CXPT-03-05, 2018JM6010, and 2015JQ6263, and the Talent Project of Science and Technology Department of Shaanxi Province, No. 2017KJXX-72.

Data Availability Statement: The data is not applicable due to confidentiality.

**Acknowledgments:** This work was performed within the project financially supported by the State Key Laboratory of Transient Optics and Photonics, Xi'an Institute of Optics and Precision Mechanics, Chinese Academy of Sciences. Additionally, we thank SIMUCAD Information Technology Company for the provision of the thermal resistance testing experimental equipment.

Conflicts of Interest: The authors declare no conflicts of interest.

#### References

- Faircloth, B. High-brightness high-power fiber coupled diode laser system for material processing and laser pumping. In Proceedings of the Conference on High-Power Diode Laser Technology and Applications, San Jose, CA, USA, 27–28 January 2003; pp. 34–41.

- Singh, A.; Mukhopadhyay, P.K.; Sharma, S.K.; Ranganathan, K.; Oak, S.M. 82 W Continuous-Wave Green Beam Generation by Intracavity Frequency Doubling of Diode-Side-Pumped Nd:YAG Laser. IEEE J. Quantum Electron. 2011, 47, 398–405. [CrossRef]

- 3. Bailey, C.; IEEE. Thermal Management Technologies for Electronic Packaging: Current Capabilities and Future Challenges for Modelling Tools. In Proceedings of the 10th Electronics Packing Technology Conference, Singapore, 9–12 December 2008; pp. 527–532.

- 4. He, Z.Q.; Yan, Y.F.; Zhang, Z.E. Thermal management and temperature uniformity enhancement of electronic devices by micro heat sinks: A review. *Energy* **2021**, *216*, 119223. [CrossRef]

- 5. Kang, T.; Ye, Y.; Jia, Y.; Kong, Y.; Jiao, B. Enhanced Thermal Management of GaN Power Amplifier Electronics with Micro-Pin Fin Heat Sinks. *Electronics* **2020**, *9*, 1778. [CrossRef]

- 6. Wipiejewski, T.; Peters, M.G.; Young, D.B.; Thibeault, B.J.; Fish, G.A.; Coldren, L.A. Thermal resistance of etched-pillar vertical-cavity surface-emitting laser diodes. In Proceedings of the Conference on Optoelectronic Packaging, San Jose, CA, USA, 1–2 February 1996; pp. 171–182.

- 7. Chang, J.; Wang, L.; Dirk, J.; Xie, X. Finite element modeling predicts the effects of voids on thermal shock reliability and thermal resistance of power device. *Weld. J.* **2006**, *85*, 63S–70S.

- 8. Kuc, M.; Wasiak, M.; Sarzaa, R.P. Impact of Heat Spreaders on Thermal Performance of III-N-Based Laser Diode. *IEEE Trans. Compon. Packag. Manuf. Technol.* **2015**, *5*, 474–482. [CrossRef]

- 9. Otiaba, K.C.; Bhatti, R.S.; Ekere, N.N.; Mallik, S.; Alam, M.O.; Amalu, E.H.; Ekpu, M. Numerical study on thermal impacts of different void patterns on performance of chip-scale packaged power device. *Microelectron. Reliab.* **2012**, *52*, 1409–1419. [CrossRef]

- 10. Ma, X.; Huo, J.; Qu, Y.; Du, S.; Wang, Y. Thermal-resistor Analysis of The Laser Chips with Different Size in C-mount Package. *Chin. J. Lumin.* **2011**, 32, 184–187.

- 11. Ni, Y.; Jing, H.; Kong, J.; Wang, C.; Liu, S.; Ma, X. Thermal Performance of High-Power Laser Diodes Packaged by SiC Ceramic Submount. *Chin. J. Lasers* **2018**, 45, 0101002.

- 12. Nishiguchi, M.; Goto, N.; Nishizawa, H. Highly reliable au-sn eutectic bonding with background gaas lsi chips. *IEEE Trans. Compon. Hybrids Manuf. Technol.* **1991**, *14*, 523–528. [CrossRef]

- 13. Liu, D.; Wang, F.; Zeng, F.; Shang, X. Finite element simulation method of high temperature thermal contact resistance. *Eng. Mech.* **2012**, *29*, 375–379.

- 14. Lu, Y.; Nie, Z.Q.; Zhang, P.; Wang, Z.F.; Xiong, L.L.; Wang, S.N.; Wu, D.H.; Liu, X.S. Numerical Simulation of Thermo-mechanical Behavior in High Power Diode Laser Arrays. In Proceedings of the 17th International Conference on Electronic Packaging Technology (ICEPT), Wuhan, China, 16–19 August 2016; Chinese Institute of Electronics: Portland, ME, USA; Electronic Manufacturing Company: Maplewood, NJ, USA; Packaging Technology Society: Wuhan, China, 2016; pp. 76–83.

- 15. Ma, Z.; Lin, T.; Zhao, R.; Sun, W.; Mu, Y.; Li, Y.; Xie, J. Research on Thermal Analysis Modeling of Semiconductor Laser Based on Package Prototype. *Laser Optoelectron. Prog.* **2021**, *58*, 1450.

- 16. Wang, S.; Bo, B.; Xu, L.; Du, Y.; Qiao, Z.; Gao, X. Thermal Analysis on Semiconductor Laser with Non-injection Region. *Chin. J. Lumin.* **2014**, *35*, 969–973. [CrossRef]

- 17. Zhang, X.L.; Bo, B.X.; Qiao, Z.L.; Xu, Y.M.; Gao, X. Analysis of thermal characteristics based on a new type diode laser packaging structure. *Opt. Eng.* **2017**, *56*, 085105. [CrossRef]

- 18. Romo, G.; Smy, T.; Walkey, D.; Reid, B. Modeling facet heating in ridge lasers. Microelectron. Reliab. 2003, 43, 99–110. [CrossRef]

19. Ryvkin, B.S.; Avrutin, E.A. Free-carrier absorption and active layer heating in large optical cavity high-power diode lasers. *J. Appl. Phys.* **2006**, *100*, 2212147. [CrossRef]

- 20. Wu, D.-H.; Zah, C.-E.; Liu, X. Three-dimensional thermal model of high-power semiconductor lasers. *Appl. Opt.* **2019**, *58*, 3892–3901. [CrossRef] [PubMed]

- 21. Kim, D.S.; Holloway, C.; Han, B.; Bar-Cohen, A. Method for predicting junction temperature distribution in a high-power laser diode bar. *Appl. Opt.* **2016**, *55*, 7487–7496. [CrossRef] [PubMed]

- 22. Xi, Y.; Schubert, E.F. Junction-temperature measurement in GaN ultraviolet light-emitting diodes using diode forward voltage method. *Appl. Phys. Lett.* **2004**, *85*, 2163–2165. [CrossRef]

- 23. Liu, J.; Feng, S.W.; Zhang, G.C.; Zhu, H.; Guo, C.S.; Qiao, Y.B.; Li, J.W. A Novel Method for Measuring the Temperature in the Active Region of Semiconductor Modules. *Chin. Phys. Lett.* **2012**, 29, 044401. [CrossRef]

- 24. Yulin, G.A.O.; Yijun, L.V.; Zhong, C. Thermal Measurement of Power LED by Structure Function. *Semicond. Optoelectron.* **2008**, 29, 329.

- 25. Chen, Y.; Chen, M.; Gao, B.; Hu, B.; Lai, W.; Xu, S. Evaluation of Solder Failure of an IGBT Module Based on Transient Thermal Impedance. *Proc. Chin. Soc. Electr. Eng.* **2018**, *38*, 3059–3067.

- 26. Anithambigai, P.; Shanmugan, S.; Mutharasu, D.; Zahner, T.; Lacey, D. Study on thermal performance of high power LED employing aluminum filled epoxy composite as thermal interface material. *Microelectron. J.* **2014**, *45*, 1726–1733. [CrossRef]

- 27. Szekely, V. A new evaluation method of thermal transient measurement results. Microelectron. J. 1997, 28, 277–292. [CrossRef]

- 28. Kim, H.H.; Choi, S.H.; Shin, S.H.; Lee, Y.K.; Choi, S.M.; Yi, S. Thermal transient characteristics of die attach in high power LED PKG. *Microelectron. Reliab.* **2008**, *48*, 445–454. [CrossRef]

- 29. Li, X.N.; Zhang, Y.X.; Wang, J.W.; Xiong, L.L.; Zhang, P.; Nie, Z.Q.; Wang, Z.F.; Liu, H.; Liu, X.S. Influence of Package Structure on the Performance of the Single Emitter Diode Laser. *IEEE Trans. Compon. Packag. Manuf. Technol.* **2012**, *2*, 1592–1599. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.