Article

# Investigation on Temperature Dependency of Recessed-Channel Reconfigurable Field-Effect Transistor

Jang Hyun Kim 10 and Sangwan Kim 2,\*0

- Inter-university Semiconductor Research Center, Department of Electrical and with the Department of Computer Engineering, Seoul National University, Seoul 08826, Korea; neuburg@naver.com

- Department of Electrical and Computer Engineering, Ajou University, Suwon 16499, Korea

- \* Correspondence: sangwan@ajou.ac.kr; Tel.: +82-31-219-2974

Received: 11 September 2019; Accepted: 1 October 2019; Published: 6 October 2019

**Abstract:** Current-voltage (I-V) characteristics of a recessed-channel reconfigurable field-effect transistor (RC-RFET) is discussed, herein, depending on the variation of temperature (T) to understand the operation mechanisms, in depth. Assuming that RC-RFET can be simply modeled as a channel resistance ( $R_{CH}$ ) and a Schottky contact resistance ( $R_{SC}$ ) connected in series, the validity has been examined by a technology computer-aided design (TCAD) simulation with different Schottky barrier heights (SBHs) and carrier mobilities ( $\mu$ ). As a result, it was clearly determined that the drain current ( $I_{D}$ ) of RC-RFET is dominated by the bigger component, since  $R_{CH}$  and  $R_{SC}$  have an opposite correlation with T.

Keywords: recessed-channel; reconfigurable field-effect transistor; RC-RFET; Schottky contact

## 1. Introduction

Over the past five decades metal-oxide-semiconductor field-effect transistors (MOSFETs) have been aggressively scaled down for a low-power operation with high performance and an enhanced logic functionality with large integration density [1,2]. However, below the 10 nm node, the extension of Moore's law by aggressive scaling of FETs becomes increasingly difficult due to several technical issues [2]. Therefore, there have been a lot of efforts for an appropriate successor to the conventional complementary MOS (CMOS) technology especially based on novel devices [3]. On the other hand, a reconfigurable FET (RFET) has been regarded as another candidate to address the issues by extending the logic functionality of switching elements [4]. It features dynamically programmable operations which allows an integrated circuit (IC) to reduce the required devices for a similar logic function result in circuit-level scaling down [4–9]. Although there are several studies about RFETs, most of them have mainly focused on strategies for improving electrical performance with the help of geometrical device structures, materials, etc. [4–7,10,11] and there is still a lack of understanding about their operation mechanisms. RFETs are programmable as n- and p-FETs by selecting carrier types injected from Schottky contact at source which depends on the temperature (*T*), sensitively [12]. Therefore, a rigorous study about the T characteristics of RFETs is an important research topic. In this letter, the T dependent current-voltage (I-V) characteristic is discussed and analyzed by technology computer-aided design (TCAD) simulation [13].

## 2. Device Structure and Simulation

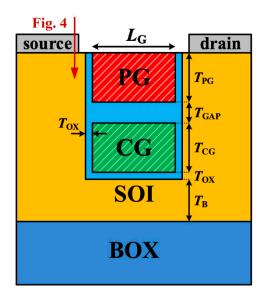

In this work, a novel recessed-channel RFET (RC-RFET), which was proposed in [11] to improve scalability and short-channel-effect immunity of conventional RFET, was used for the

study (Figure 1) [14,15]. The switching mechanism of RC-RFET (thermionic emission) differs from that of conventional RFET (Schottky barrier tunneling). It enables RC-RFET to overcome the fundamental limit of subthreshold swing (S) degradation as a function of gate voltage and promises higher ON–OFF current ratio ( $I_{\rm ON}/I_{\rm OFF}$ ) [11]. The detail parameters used for the TCAD simulation are summarized in Table 1 and the following physical models are used: Shockley–Read–Hall (SRH) recombination, Schottky barrier tunneling (SBT), field-dependent mobility, drift-diffusion, and non-local band-to-band tunneling (BTBT) [13]. In order to exclude the effect of dopants and secure symmetricity for n- and p-FET operations, intrinsic silicon-on-insulator (SOI) is used for channel. The work function ( $W_{\rm FN}$ ) for both the polarity gate (PG) and control gate (CG) is 4.6 eV, while Schottky barrier height (SBH) for Si/metal contact is 0.56 eV unless otherwise noted. They are analogous to half of the Si band gap.

**Figure 1.** Schematic structure diagrams for recessed-channel reconfigurable field-effect transistor (RC-RFET). It features the vertically stacked polarity gate (PG) and control gate (CG) separated to each other with an oxide gap.

| Definition                        | Abbreviation      | Value |

|-----------------------------------|-------------------|-------|

| Silicon body thickness            | $T_{\mathrm{B}}$  | 20 nm |

| Gate oxide thickness              | $T_{OX}$          | 1 nm  |

| Gate length                       | $L_{G}$           | 50 nm |

| Program gate thickness            | $T_{\mathrm{PG}}$ | 20 nm |

| Control gate thickness            | $T_{\text{CG}}$   | 20 nm |

| Oxide thickness between PG and CG | $T_{\rm GAP}$     | 10 nm |

**Table 1.** Simulated device parameters.

# 3. Results and Discussion

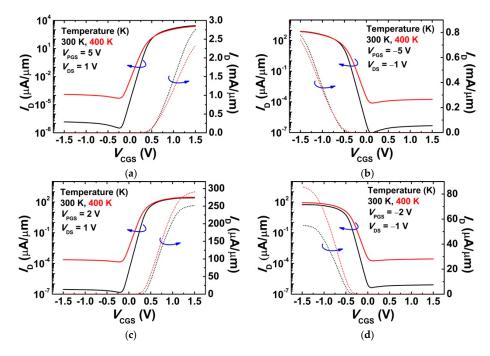

Figure 2 shows drain current ( $I_D$ ) versus CG bias ( $V_{CGS}$ ) for n- and p-FET operations as T increases from 300 K to 400 K with different PG bias ( $V_{PGS}$ ). As shown in Figure 2a,b, the on-current ( $I_{ON}$ ) defined as  $I_D$  at  $\pm 1.5$  V- $V_{CGS}$  is decreased for both n- and p-FETs as T increases in accordance with general expectation, since the mobility ( $\mu$ ) is decreased due to phonon scattering as expressed in Equation (1) [16]. The  $\mu$  at 300 K-T ( $\mu_0$ ) and  $\gamma$  are 1417 cm<sup>2</sup>/V·s and 2.5 for electron, whereas 486 cm<sup>2</sup>/V·s and 2.2 for hole, respectively [13].

$$\mu = \mu_0 \left(\frac{T}{300 \text{ K}}\right)^{-\gamma} \tag{1}$$

**Figure 2.** Schematic transfer characteristics depending on T with different  $V_{PGS}$ . (a) n-FET operations with  $V_{PGS} = 5$  V; (b) p-FET operations with  $V_{PGS} = -5$  V; (c) n-FET operations with  $V_{PGS} = 2$  V; (d) p-FET operations with  $V_{PGS} = -2$  V. The arrows indicate the direction of the graph according to log scale and linear scale.

The noteworthy points are shown in Figure 2c,d that the  $I_{ON}$  becomes an increasing function of the T as  $|V_{PGS}|$  is decreased from 5 to 2 V.

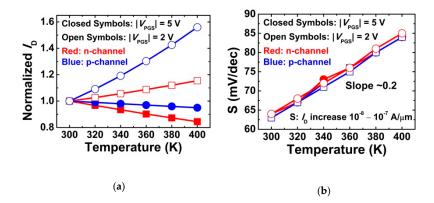

Figure 3a clearly shows  $I_{\rm ON}$  has different tendencies on the T depending on the  $V_{\rm PGS}$ , regardless of n- or p-FETs. It is not related to the subthreshold characteristics since the extracted S is exactly sitting on the  $2.3k_{\rm B}/q$ -slope ( $\sim$ 0.2 mV/K) line similar to the conventional MOSFETs, where  $k_{\rm B}$  and q are the Boltzmann constant and elementary charge, respectively (Figure 3b).

**Figure 3.** Extracted parameters from  $I_D$ – $V_{PGS}$  curves. (a) Normalized  $I_{ON}$  by  $I_{ON}$  at 300 K.  $I_{ON}$  is extracted when  $V_{PGS}$  is 1.5 V; (b) subthreshold swing (*S*). The extracted *S* is exactly sitting on the  $2.3k_B/q$ -slope ( $\sim$ 0.2 mV/K) line.

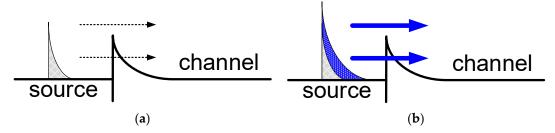

In order to analyze these phenomena, the RC-RFET is simply modeled as a channel resistance ( $R_{\rm CH}$ ) and a Schottky contact resistance ( $R_{\rm SC}$ ) connected in series, which have an opposite correlation with T. In other words, if T is increased, the  $R_{\rm CH}$  is increased due to the increased phonon scattering, whereas the  $R_{\rm SC}$  is decreased due to the increased carrier injection 'over' and 'through' the Schottky barriers at source and drain contacts (Figure 4). Accordingly, the total resistance ( $R_{\rm TOT}$ ) and  $I_{\rm ON}$  is dominated by the bigger one. Since  $R_{\rm SC}$  is exponentially decreased as a function of band bending, the  $R_{\rm TOT}$  can

be approximated to  $R_{\rm CH}$  and  $R_{\rm SC}$  with a small and a large  $|V_{\rm PGS}|$ , respectively. From Equation (1), the  $\mu$  of electron ( $\mu_{\rm e}$ ) is more sensitive to T than that of the hole ( $\mu_{\rm h}$ ) due to the different coefficient  $\gamma$ . Thus,  $R_{\rm CH}$  of n-FET increases faster than that of p-FET as T increase which is well corresponded to the different slopes for 5 V- $|V_{\rm PGS}|$  in Figure 3a. On the other hand, in case of small  $|V_{\rm PGS}|$  (= 2V), p-FET is more sensitive than n-FET to the T. This is because the effect of  $R_{\rm SC}$  decreasing is cancelled out by the  $R_{\rm CH}$  increase with the higher T for n-FET.

**Figure 4.** Energy band diagram and carrier distribution with different T. (a) Low T; (b) high T. The energy band is plotted along the source and channel (Figure 1). The blue-colored areas in the source represent the increased carrier distribution due to the increased T, and blue-colored arrows indicate the increased carriers passing through the Schottky barrier (SB) due to the increased T.

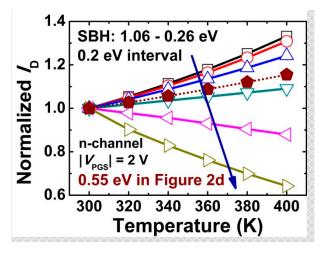

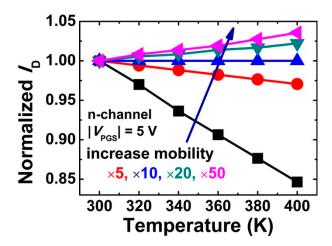

In order to confirm the hypothesis, the effects of  $R_{SC}$  and  $R_{CH}$  on n-FETs'  $I_{ON}$  have been examined independently. For that, the change of doping concentration is inappropriate since both factors are affected at the same time. Thus, the  $R_{SC}$  and the  $R_{CH}$  of n-FET are changed by adjusting SHB and  $\mu_e$ , respectively. First, if SBH decreases from 1.06 eV to 0.26 eV, the dominant factor changes from  $R_{SC}$  to  $R_{CH}$ ;  $I_{ON}$  decreases as T increases as shown in Figure 5. On the other hand, if  $\mu_e$  increases several times the default value (1417 cm²/V·s), the  $R_{TOT}$  is determined by the  $R_{SC}$  (Figure 6). As a result, there is a positive correlation between  $I_{ON}$  and T. Consequently, the assumption is clearly proven to be reasonable. It has to be mentioned that even if this approach is less practical in terms of device design, it is very meaningful to understand and confirm the operation mechanism and overall physics of RFET which is a milestone for device engineers.

**Figure 5.** Normalized  $I_{ON}$  of n-FET as a function of T with different SBH (Schottky barrier height). The blue arrow shows a decrease in the normalized  $I_D$  due to SBH reduction.

**Figure 6.** Normalized  $I_{ON}$  of n-FET as a function of T with different  $\mu_{e.}$  The blue arrow shows an increase in the normalized  $I_{D}$  due to mobility increasement.

### 4. Conclusions

The effects of T on the electrical characteristics of RC-RFET have been examined. There is an abnormal phenomenon that the  $I_{\rm ON}$  decreases as T increases with a small  $|V_{\rm PGS}|$ . Based on rigorous study with the help of TCAD simulation, this was attributed to the large  $R_{\rm SC}$  which decreases the function of T and dominates the  $R_{\rm TOT}$ . This needs to be further addressed for high-performance operation with low-power consumption. In order to decrease SBH for the lower  $R_{\rm CH}$ , adopting a narrow band gap material (e.g., SiGe or Ge) at the source/drain and metal contacts could be a promising solution. In future works, the influences of band gap on SBH will be examined and the optimized RC-RFET will be demonstrated.

Author Contributions: Writing (original draft preparation, review, and editing) J.H.K.; supervision, S.K.

**Funding:** This research was supported in part by the Brain Korea 21 Plus Project, in part by the MOTIE/KSRC under Grant 10080575 (Future Semiconductor Device Technology Development Program), in part by the NRF of Korea funded by the MSIT under Grant NRF-2019M3F3A1A02072091 (Intelligent Semiconductor Technology Development Program) and in part by the MSIT (Ministry of Science and ICT), Korea, under the ITRC (Information Technology Research Center) support program (IITP-2019-2016-0-00309) supervised by the IITP (Institute for Information & communications Technology Planning & Evaluation). The EDA tool was supported by the IC Design Education Center (IDEC), Korea.

Conflicts of Interest: The authors declare no conflicts of interest.

# References

- 1. Ferain, I.; Colinge, C.A.; Colinge, J.P. Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors. *Nature* **2011**, 479, 310–316. [CrossRef] [PubMed]

- 2. International Roadmap for Devices and Systems (IRDSTM) 2018 Edition. Available online: https://irds.ieee.org/editions/2018 (accessed on 5 October 2019).

- 3. Cristoloveanu, S.; Wan, J.; Zaslavsky, A. A review of sharp-switching devices for ultra-low power applications. *IEEE J. Electron Devices Soc.* **2016**, *4*, 215–226. [CrossRef]

- 4. Javey, A.; Tu, R.; Farmer, D.B.; Guo, J.; Gordon, R.G.; Dai, H. High performance n-type carbon nanotube field-effect transistors with chemically doped contacts. *Nano Lett.* **2005**, *5*, 345–348. [CrossRef] [PubMed]

- 5. Trommer, J.; Heinzig, A.; Baldauf, T.; Slesazeck, S.; Mikolajick, T.; Weber, W.M. Functionality-Enhanced Logic Gate Design Enabled by Symmetrical Reconfigurable Silicon Nanowire Transistors. *IEEE Trans. Nanotechnol.* **2015**, *14*, 689–698. [CrossRef]

- 6. Lin, Y.F.; Xu, Y.; Wang, S.T.; Li, S.L.; Yamamoto, M.; Aparecido-Ferreira, A.; Li, W.; Sun, H.; Nakaharai, S.; Jian, W.B.; et al. Ambipolar MoTe<sub>2</sub> transistors and their applications in logic circuits. *Adv. Mater.* **2014**, 26, 3263–3269. [CrossRef] [PubMed]

7. Heinzig, A.; Mikolajick, T.; Trommer, J.; Grimm, D.; Weber, W.M. Dually active silicon nanowire transistors and circuits with equal electron and hole transport. *Nano Lett.* **2013**, *13*, 4176–4181. [CrossRef] [PubMed]

- 8. Crupi, G.; Schreurs, D.M.M.P.; Raskin, J.P.; Caddemi, A. A comprehensive review on microwave FinFET modeling for progressing beyond the state of art. *Solid. State. Electron.* **2013**, *80*, 81–95. [CrossRef]

- 9. Crupi, G.; Schreurs, D.M.M.P.; Caddemi, A. Effects of gate-length scaling on microwave mosfet performance. *Electronics* **2017**, *6*, 62. [CrossRef]

- 10. Weber, W.M.; Heinzig, A.; Trommer, J.; Martin, D.; Grube, M.; Mikolajick, T. Reconfigurable nanowire electronics—A review. *Solid. State. Electron.* **2014**, *102*, 12–24. [CrossRef]

- 11. Kim, S.; Kim, S.W. Recessed-channel reconfigurable field-effect transistor. *Electron. Lett.* **2016**, *52*, 1640–1642. [CrossRef]

- 12. Appenzeller, J.; Radosavljević, M.; Knoch, J.; Avouris, P. Tunneling versus thermionic emission in one-dimensional semiconductors. *Phys. Rev. Lett.* **2004**, *92*, 4. [CrossRef] [PubMed]

- 13. Synopsys Inc. Sentaurus Device User Guide-v.K-2015.06; Synopsys Inc.: Mountain View, CA, USA, 2009.

- 14. Kim, J.Y.; Oh, H.J.; Woo, D.S.; Lee, Y.S.; Kim, D.H.; Kim, S.E.; Ha, G.W.; Kim, H.J.; Kang, N.J.; Park, J.M.; et al. S-RCAT (Sphere-shaped-Recess-Channel-Array Transistor) Technology for 70nm DRAM feature size and beyond. In Proceedings of the Digest of Technical Papers—Symposium on VLSI Technology, Kyoto, Japan, 14–16 June 2005; Volume 2005, pp. 34–35.

- 15. Park, S.; Seo, H.; Oh, J.; Kim, I.; Hong, H.; Jin, G.; Roh, Y. Roles of residual stress in dynamic refresh failure of a buried-recessed-channel-array transistor (B-CAT) in DRAM. *IEEE Electron Device Lett.* **2016**, *37*, 859–861. [CrossRef]

- 16. Lombardi, C.; Manzini, S.; Saporito, A.; Vanzi, M. A Physically Based Mobility Model for Numerical Simulation of Nonplanar Devices. *IEEE Trans. Comput. Des. Integr. Circuits Syst.* 1988, 7, 1164–1171. [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).