Optimal and Robust Design Method for Two-Chip Out-of-Plane Microaccelerometers

Abstract

: In this paper, an optimal and robust design method to implement a two-chip out-of-plane microaccelerometer system is presented. The two-chip microsystem consists of a MEMS chip for sensing the external acceleration and a CMOS chip for signal processing. An optimized design method to determine the device thickness, the sacrificial gap, and the vertical gap length of the M EMS sensing element is applied to minimize the fundamental noise level and also to achieve the robustness to the fabrication variations. In order to cancel out the offset and gain variations due to parasitic capacitances and process variations, a digitally trimmable architecture consisting of an 11 bit capacitor array is adopted in the analog front-end of the CMOS capacitive readout circuit. The out-of-plane microaccelerometer has the scale factor of 372 mV/g∼389 mV/g, the output nonlinearity of 0.43% FSO∼0.60% FSO, the input range of ±2 g and a bias instability of 122 μg∼229 μg. The signal-to-noise ratio and the noise equivalent resolution are measured to be 74.00 dB∼75.23 dB and 180 μg/rtHz∼190 μg/rtHz, respectively. The in-plane cross-axis sensitivities are measured to be 1.1%∼1.9% and 0.3%∼0.7% of the out-of-plane sensitivity, respectively. The results show that the optimal and robust design method for the MEMS sensing element and the highly trimmable capacity of the CMOS capacitive readout circuit are suitable to enhance the die-to-die uniformity of the packaged microsystem, without compromising the performance characteristics.1. Introduction

Over the last decade, extensive efforts have been devoted to the continuously maturing Microelectromechanical System (MEMS) technologies. Above all, MEMS microaccelerometers have been successfully commercialized in a wide range of application areas including automotive safety control, ubiquitous robots, inertial navigation and consumer electronics [1,2]. Most of these applications require sensors which have a multi-axial operation, high sensitivity, large dynamic range, low noise floor and low bias instability, while maintaining low-cost and mass-productivity. The current commercial-off-the-shelf (COTS) MEMS accelerometers have multi-axial operation, while maintaining the noise-floor between a few tens to hundreds μg level. However, the noise-level of the out-of-plane axis is generally higher than that of the in-plane axes. In order to improve the noise performance of the out-of-plane axis, an optimized design method considering the mechanical-thermal noise limit of the MEMS sensing element should be applied.

Recently, a microsystem using a two-chip solution consisting of a MEMS element and a CMOS readout circuit has been implemented so as to improve the noise performance [3–5]. A specialized MEMS bulk micromachining process and an advancement of packaging technology have been established to enable a miniaturized microsystem, while maintaining a low fundamental noise level. Moreover, an optimal and robust design of the MEMS sensing element is necessary so as to enhance the robustness to the fabrication variations. Amini et al. [3] have demonstrated an in-plane micro-gravity accelerometer by optimizing the gap size of comb electrode. Ko et al. [4] presented a design principle of an in-plane accelerometer to optimize the thickness of device layer to minimize the fundamental noise limit. In these papers, however, the dimensional optimization is limited for an in-plane accelerometer and performance variation due to process variation is not discussed. For the low noise characteristic of an out-of-plane operation, Hsu et al. [5] calculated the estimated thermal-mechanical noise. However, this paper only acknowledged the designed result, and did not deal with the design procedure to minimize the noise floor in detail.

The capacitive sensing scheme provides advantages in low temperature dependency, good DC response, and good noise performance [6]. However, the performance of a capacitive sensing sensor is severely limited by the parasitic capacitance. In case of two-chip implemented microsystem, the parasitic capacitances randomly exist mainly due to process variations, bonding wire and bonding pad, which is in several pF ranges [7,8]. Several research groups have reported the method to compensate the process variations using capacitive readout ICs [3,9,10], but the trimmable range for compensation is limited. Therefore, to determine the compensation capability of the CMOS capacitive readout circuit, the capacitance variation of the MEMS sensing element due to fabrication process should be analyzed along with the implementation of a highly trimmable architecture.

In this paper, an implementation of an out-of-plane microaccelerometer system employing an optimal and robust design method that achieves robustness towards the fabrication variations and enhances the die-to-die uniformity without compromising the performance characteristics is presented. The optimal design method is based on the minimization of the total noise equivalent acceleration (TNEA) of the two-chip implemented microsystem. Besides lateral dimensions such as width and length of the torsional spring and gap between the comb electrodes, vertical dimensions such as structural thickness and sacrificial gap of the sensing element and vertical gap length between the moving and stationary vertical comb electrode are taken into consideration for the several reasons, which are discussed later in this paper. The sensor operation is based on a coplanar sense electrode movement wherein the change in capacitance is caused by variation of the overlap area [11] rather than in the air gap [12]. This differential sensing scheme enables the design of a wide dynamic range out-of-plane accelerometer. Another advantage of this sensing scheme is that squeeze film damping between the movable proof mass and the substrate can be minimized by fabricating a large sacrificial gap. Since, the proposed microaccelerometer adopts a CMOS and MEMS, two-chip packaged implementation, the mechanical damping of the MEMS sensing element can be an important issue when demonstrating a low noise device. The out-of-plane microaccelerometer is fabricated by the Extend Sacrificial Bulk Micromachining (ESBM) process [13] and wafer-level hermetic packaging (WLHP) process [4]. The ESBM process is a simple, two-mask fabrication process, which is able to fabricate a high-aspect-ratio structure with a large sacrificial gap and to fabricate the upper and lower vertical gap between the interdigitated comb electrodes.

The brief features mentioned above will be described in the following sections. Beginning with a concept of a two-chip implemented microsystem, the optimal design analysis to determine the device thickness and the vertical gap length will be followed. The design will be substantiated by both electrostatic and mechanical analysis as well as finite element method (FEM) simulation. Then, the advantages of the separate two-chip implemented microsystem will be discussed. After the fabrication principles and fabrication results, the experimental results are evaluated. Finally, conclusions will be drawn.

2. Two-Chip Implemented Microsystem

In this microaccelerometer system, a two-chip solution comprising of separated CMOS sensing electronics and MEMS element is adopted. This two-chip solution allows specialized and optimized processing for CMOS and MEMS [14]. However, with the two-chip implementation compared to the monolithic integration, the dynamic range and the gain of the microsystem can be limited due to increased parasitic capacitance [15]. In order to cancel out the offset and gain variations due to parasitic capacitances and to minimize the die-to-die variation due to process variations, a digitally trimmable architecture consisting of capacitor arrays is adopted in the CMOS capacitive readout circuit [16].

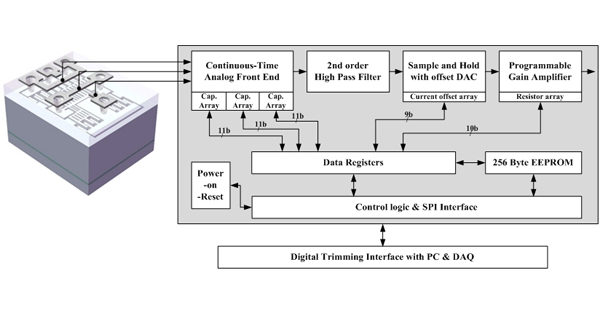

In Figure 1, the top level block diagram of the two-chip implemented microsystem is shown. The MEMS sensing element is fabricated by the ESBM process and the WLHP process. The capacitance change of the MEMS sensing element is converted to a modulated voltage signal by the continuous-time front-end charge amplifier. The compensation of offset and gain variations is performed using 11 bit programmable capacitor arrays. The low frequency noise components of the modulated signal are attenuated by the following high pass filter. Then, the modulated voltage signal is demodulated by a sample-and-hold demodulator and offset calibration of the signal is performed in this stage using a 9-bit current-mode digital-to-analog converter (DAC). Next, the unnecessary high frequency noise components are eliminated by a low pass filter, and the desired signal is obtained. The gain of the signal can be calibrated using a 10 bit programmable gain amplifier (PGA). The programmed data is stored to the 256 byte EEPROM block, and reloaded to the registers when the power is turned on.

3. MEMS Sensing Element Design

The conceptual schematic diagram of a capacitive out-of-plane torsional microaccelerometer is illustrated in Figures 2(a,b). The sensing element is designed to have an asymmetric proof mass suspended by two guided-end torsional springs and comb electrodes. In addition, stationary comb electrodes and movable comb electrodes form an interdigitated pair to detect capacitance change. In this MEMS sensing element design, the differential capacitive sensing scheme is employed. A vertical gap is formed between stationary comb electrodes and movable comb electrodes in upper and lower parts, so as to enhance the mechanical sensitivity, linearity and noise performance. When external acceleration is applied, the guided-end springs are twisted by torque acting on the asymmetric proof mass of the sensing element. The rotation of this asymmetric mass makes a change in the overlap area between the stationary and movable comb fingers, which results in an increment or a decrement of the capacitance.

In this paper, the lateral dimensions are fixed and only the vertical dimensions, which is determined by the fabrication process is taken into consideration. As the gap between the comb electrodes is increased, the mechanical damping gets smaller and the Brownian noise equivalent acceleration (BNEA) is improved. However, the mechanical sensitivity, which is determined by the capacitance change between the interdigitated comb electrodes, is decreased and the circuit noise equivalent acceleration (CNEA) is increased. Therefore the minimum gap size of 4 μm is chosen to maximize the mechanical sensitivity. The torsional spring stiffness is determined by considering the input dynamic range of ±2 g. As the torsional spring stiffness is decreased, the noise performance is enhanced due to the decrement of the 1st order natural frequency and also mechanical sensitivity can be improved. However, the process yield during the fabrication process and the impact resistance of the sensing element get poor due to the decreased torsional stiffness [17,18]. For this reason, the mask dimension of the spring width and length is determined to be 4 μm and 150 μm, respectively. Therefore the proposed design method is applied to optimize the vertical dimensions of the MEMS sensing element, so as to minimize the noise level and also to achieve the robustness to the fabrication variations.

3.1. Optimization of Device Thickness

The design parameters of the MEMS sensing element are listed in Table 1. In order to maximize the performance characteristic and the noise performance, it is necessary to determine the optimal structural thickness which minimizes the mechanical-thermal noise. The fundamental sense limit of the MEMS sensing element is set by the BNEA of the suspended proof mass [19]. The BNEA is expressed as:

The squeeze film damping coefficient of the two parallel plates [23] is derived as:

For the case where t << a, the quality factor is given as:

Since the device layer of the SOI wafer has a thickness limit of 65 μm, the sacrificial gap between two plates decreases as the device thickness increases, as illustrated in Figure 2(b). This implies that to minimize the BNEA level, the structural thickness must have limitation at a certain level.

Another limiting factor is the circuit noise equivalent acceleration (CNEA) that depends on the simulated minimum detectable capacitance of the readout circuit (ΔCmin) and the mechanical sensitivity of the MEMS sensing element (S = ΔC/g). In Figures 5 (a,b), the cross-sectional schematic of the interdigitated comb electrode is shown. Using the detailed parameters from Table 1, the mechanical sensitivity can be derived. The CNEA and mechanical sensitivity can be expressed as:

Figure 6 shows the relationship between the device thickness and the BNEA, CNEA, and TNEA. It is known that noise performance is improved as the structural thickness of the sensing element is increased [4]. However, the proposed out-of-plane microaccelerometer is fabricated on a SOI wafer which has a device layer thickness of 65 μm, therefore, as the thickness of the sensing element increases the thickness of the sacrificial layer is decreased, which results in a low mechanical quality factor and a high TNEA level. This result implies that to achieve the minimum TNEA level, the optimized structural thickness is between 23 μm and 27 μm. When the device thickness is 25 μm, the BNEA is 30.79 μg/(Hz)1/2, the CNEA for ΔCmin at 0.2 aF/(Hz)1/2 is 15.45 μg/(Hz)1/2, and the TNEA is 45.06 μg/(Hz)1/2.

3.2. Optimization of Vertical Gap Length

The proposed out-of-plane microaccelerometer has a vertical gap formed between stationary comb electrodes and movable comb electrodes in the upper and lower parts. In previous studied out-of-plane accelerometers [11,24], a conventional formula of parallel-plate capacitance is used to derive the mechanical sensitivity for the ease of evaluating the device characteristics in analytical expression. The accuracy of the evaluated result can be improved by assuming a constant fringing field method such as Palmer’s formula [25]. These approaches can be valid for a capacitive sensing structure using an air-gap sensing mechanism. However, for a comb-finger typed out-of-plane structure, the effect of fringing field varies due to vertical gap length. Therefore, electrostatic simulation using FEM tool (ANSYS, Inc., United States) is done to verify the optimized vertical gap length.

In order to derive the capacitance, a simplified three dimensional simulation model with two parallel-plates is used. A 10 V (V0) source is applied to the inner comb electrode and a 1 V (V1) source is applied to the outer comb electrode. Then, from the FEM simulation the electrostatic energy, W, and the nominal capacitance, CANSYS, can be calculated using Equation (8):

The simulation is performed for the zero input acceleration and the 1 g input acceleration to derive the mechanical sensitivity. In this out-of-plane microaccelerometer, due to the dimensional limitation of the design constraints, the vertical gap length is set to have a value below 15 μm. Therefore variation of the vertical gap length is carried out from 0 μm to 15 μm. The analyzed result of the mechanical sensitivity using FEM simulation is plotted in Figure 7.

In order to compare the result, the mechanical sensitivity derived from a conventional parallel-plate formula and a constant fringing capacitance formula is also plotted. The mechanical sensitivity increases due to the increase of the vertical gap length from 0 μm to 10 μm. However, at length between 11 μm and 15 μm, the mechanical sensitivity is in the range from 20.6 fF/g to 21.5 fF/g. Due to the analyzed result and the consideration of fabrication process error about 10%, the vertical gap length is determined to be within the range from 12 μm to 14 μm.

4. Capacitive Interface Circuit Design

Although many advanced micromachining processes are developed, fabrication imperfection is inevitable with current MEMS fabrication techniques [26]. For example, the resonant frequency of a resonator is mostly determined by the spring stiffness, and the practical tolerance in the spring width during the fabrication process is about 10% [27]. Also, the pattern variation due to over-exposure and under-exposure occurs frequently during the photolithography step. The imperfections in the deep reactive ion etching (DRIE) process, such as undercut and footing phenomenon, also results in a large process variation. In this circuit design, the expected variation range of structural thickness (t), vertical gap length (g), and gap between two parallel comb electrodes (d) are from 23 μm to 27 μm, from 12 μm to 14 μm, and 3.2 μm to 4.8 μm, respectively. From Table 1, the variation of nominal capacitance (CO) and mechanical sensitivity (S) can be expressed as:

The proposed schematic of the capacitive analog front-end is shown in Figure 9. The output voltage of the front-end charge amplifier is derived as:

In this capacitive interface circuit design, a continuous-time chopper stabilized sensing scheme is adopted. Since the capacitive circuit is implemented with a large feedback resistor (RF > 10 MΩ) and high chopping frequency (s = 500 kHz), sRF » 1 and Equation (11) can be simplified to:

Thus, by trimming the CF capacitor array, the variation of analog front-end gain can be easily compensated.

5. Fabrication

5.1. Fabrication Flow

The MEMS sensing element is fabricated using the ESBM process. The ESBM process allow the fabrication of both upper and lower vertical comb gaps using only two photomasks and four DRIE steps, to achieve differential sensing. The differential sensing scheme results in a highly sensitive sensing element. Also, using the ESBM process, it is possible to fabricate a structure with an inherent high-aspect-ratio with a large sacrificial gap and a structure free from the footing phenomenon. A large sacrificial gap is required to minimize the disadvantages of a large parasitic capacitance, which results in higher gain and reduction in input-referred circuit noise. In addition, the large sacrificial gap has an advantage in protecting the suspended proof mass of the MEMS sensing element from drops and impacts. The WLHP process is employed by the glass-to-silicon anodic bonding to protect the MEMS sensing element and to achieve the reliability of the microsystem.

Process flow of the ESBM process is shown in Figure 10 (a)∼(h). A (111)-oriented SOI wafer with device layer of 65 μm is used to fabricate the sensing element. After cleaning of the SOI wafer, tetra-ethyl-ortho-silicate (TEOS) hard mask is fabricated by TEOS deposition, first photolithography and plasma etching. The second photolithography process is performed to slightly etch the top TEOS layer of the lower comb electrode, which turns out to be the stationary comb electrode [Figure 10(a)]. First a DRIE process is done to determine the lower vertical gap length [Figure 10(b)]. After stripping the photoresist, a second DRIE process is carried out to determine the structural thickness [Figure 10(c)]. As analyzed previously, the structural thickness of 25 μm gives the minimized noise performance characteristic for the MEMS sensing element. Also, this result provides a large sacrificial thickness in order to minimize the TNEA level. A thermal oxidation process is used for sidewall passivation, and TEOS etching is then used to open the bottom area [Figure 10(d)]. The thickness of the sacrificial layer is defined by third DRIE process [Figure 10(e)], and the anisotropic wet etching process using the tetra-methyl-ammonium-hydroxides (TMAH) is performed [Figure 10(f)]. After cleaning and drying, a plasma etching is done to etch the thinner layer of the TEOS hard mask to open the silicon surface. Then, a fourth DRIE process is performed to define the upper vertical gap length [see Figure 10(g)]. Finally, the passivation layer is removed using hydrofluoric acid (HF) [Figure 10(h)].

The WLHP process is employed by glass-to-silicon anodic bonding process. The Pyrex 7740 glass wafer with the thickness of 350 μm is used, and fabricated using HF glass wet etching. In order to neglect the damping inside the protection cavity, the thickness of fabricated protection cavity is fabricated to be 180 μm∼190 μm. After bonding, metal interconnections are fabricated by metal sputtering. A schematic diagram of the packaged MEMS sensing element and cross-sectional view are shown in Figure 11 (a,b), respectively.

5.2. Fabrication Result

In Figure 12, a test pattern fabricated by ESBM process is shown. The upper and lower vertical gap is well fabricated, and as mentioned above, etch depth are defined by individual DRIE steps. The fabrication result of the overall MEMS sensing element with the vertical gap between the parallel comb electrodes is shown in Figure 13(a,b), respectively. The measured length of the vertical gap is 12 μm. The cross-sectional view of the packaged device, the cross-sectional view of the metal interconnection layer, and the overall view of the WLHP MEMS microaccelerometer are shown in Figure 13 (c,d,e), respectively.

6. Performance Evaluation

The fabrication result of CMOS capacitive readout circuit is shown in Figure 14. The circuit is fabricated using the SMIC 0.35 μm process with 256 byte EEPROM. The die size is 2.01 mm × 2.36 mm.

The block diagram and photograph of the experimental setup are shown in Figure 15 (a,b), respectively. The two-chip implemented microsystem is mounted on a sensor evaluation board. The circuit trimming board is used to calibrate the offset and gain of the output signal. After trimming is done, the register value is saved in the 256 byte EEPROM. The B&K 8305 (Brüel & Kjær, Denmark) reference accelerometer is used to compare the output signal with the implemented microsystem. The Agilent 33250A (Agilent Technologies, Inc., United States) function generator is used to apply the acceleration source, and the accurate acceleration is generated to the microsystem using the B&K 4808 (Brüel & Kjær, Denmark) vibration exciter.

Before measuring the performance characteristics of the out-of-plane microaccelerometer system, the offset and gain calibration is carried out. From Figure 1, the final system output, VO, can be expressed as:

The performance characteristic results are shown in Figure 16(a)∼(e). The input-output characteristic of the out-of-plane microaccelerometer system at 10 Hz input acceleration is shown in Figure 16(a). The input range and the average scale factor are measured to be ±2 g and 378 mV/g, respectively. The maximum output non-linearity is calculated to be 0.6% FSO. To measure the signal-to-noise ratio (SNR) and noise equivalent resolution (NER), the input acceleration of 10 Hz, 1 g sinusoidal wave is applied and the output spectrum is plotted [Figure 16(b)]. The thermal noise level is measured to be in the range from −80.03 dB to −79.59 dB and signal level is measured to be in the range from −6.03 dB to −4.35 dB. The maximum SNR is measured from sample #3 to be 75.23 dB, and minimum SNR is measured from sample #1 to be 74.00 dB. Therefore, the NER is calculated to be in the range from 180 μg/rtHz to 190 μg/rtHz. The measured noise floor of the each sample is 180 μg/rtHz, 183 μg/rtHz, and 190 μg/rtHz, which is higher than the result intended by the design. However, the similar results are shown between three samples, which reveal that the robustness to fabrication variations can be achieved by the proposed design method. Figure 16 (c) is the time-domain output of the microsystem with the input acceleration of 20 Hz, 1g sinusoidal wave. A phase lag of about 43.2 degree is observed. This phase lag is mainly occurred due to the low pass filter at the output stage of the fabricated CMOS capacitive readout circuit. In order to evaluate the bias instability, the root-Allan variance method [28] is adopted.

The root-Allan variance (σtotal) can be simplified using the geometric mean of the velocity random walk (σVRW) and the bias instability (σBiasInst), expressed as:

7. Conclusions

In this paper, an optimal and robust design method to implement a two-chip out-of-plane microsystem consisting of a MEMS chip for sensing the external acceleration and a CMOS chip for signal processing is presented. An optimized design method to determine the device thickness, the sacrificial gap, and the vertical gap length of the MEMS sensing element is applied to minimize the fundamental noise level and also to achieve the robustness to the fabrication variations. The MEMS sensing element is fabricated by the ESBM process to have a vertical differential sensing, and the WLHP process is performed so as to achieve the high reliability of the microsystem. In order to cancel out the offset and gain variations due to parasitic capacitance and to minimize the die-to-die variation due to fabrication mismatches, a digitally trimmable architecture consisting of the 11 bit capacitor array is adopted in CMOS capacitive readout circuit.

The summarized performance specifications are listed in Table 2. The out-of-plane microaccelerometer has the scale factor of 372 mV/g ∼ 389 mV/g, the output nonlinearity of 0.43% FSO∼ 0.60% FSO, the input range of ± 2 g and the bias instability of 122 μg∼229 μg. The SNR and the NER are measured to be 74.00 dB∼75.23 dB and 180 μg/rtHz∼190 μg/rtHz, respectively. The x- and y-axis cross-axis sensitivity is measured to be 1.1%∼1.9% and 0.3%∼0.7% of the out-of-plane sensitivity, respectively. The results show that the optimal and robust design method for the MEMS sensing element and the highly trimmable capacity of the CMOS capacitive readout circuit are suitable to enhance the die-to-die uniformity of the packaged microsystem without compromising the performance characteristics.

Acknowledgments

This work was supported partly by the R&D program of the Korea Ministry of Knowledge and Economy (MKE) and the Korea Evaluation Institute of Industrial Technology (KEIT). [2008-F-037-01, Development of HRI Solutions and Core Chipsets for u-Robot].

References and Notes

- Macdonald, GA. A review of low cost accelerometers for vehicle dynamics. Sens Actuat–A Phys 1990, 21, 303–307. [Google Scholar]

- de Coulon, Y; Smith, T; Hermann, J; Chevroulet, M; Rudolf, F. Design and test of precision servoaccelerometer with digital output. Proceeding of 7th International Conference on Solid-State Sensors and Actuators (Transducers ’93), Pacifico, Yokohama, Japan, June 7–10, 1993; pp. 832–835.

- Amini, BV; Ayazi, F. Micro-gravity capacitive silicon-on-insulator accelerometers. J Micromech Microeng 2005, 15, 2113–2120. [Google Scholar]

- Ko, H; Park, S; Choi, B; Lee, A; Cho, D. Wafer-level hermetic packaged microaccelerometer with fully differential BiCMOS interface circuit. Sens Actuat–A Phys 2007, 137, 25–33. [Google Scholar]

- Hsu, Y-W; Chen, J-Y; Chien, H-T; Chen, S; Lin, S-T; Liao, L-P. New capacitive low-g triaxial accelerometer with low cross-axis sensitivity. J Micromech Microeng 2010, 20, 055019. [Google Scholar]

- Yazdi, N; Ayazi, F; Najafi, K. Micromachined inertial sensors. Proc IEEE 1998, 86, 1640–1659. [Google Scholar]

- Karim, N. Plastic Packages’ Electrical Performance: Reduced Bond Wire Diameter; AMKOR Electronics, Inc: Chandler, AZ, USA, 2002. [Google Scholar]

- National Semiconductor. Package Electrical Characterization 1999.

- Zhang, J; Zhou, J; Mason, A. Highly adaptive transducer interface circuit for multiparameter microsystems. IEEE Trans Circuit Syst 2007, 54, 167–178. [Google Scholar]

- Bracke, W; Merken, P; Puers, R; Hoof, CV. Ultra-low-power interface chip for autonomous capacitive sensor systems. IEEE Trans Circuit Syst 2007, 54, 130–140. [Google Scholar]

- Selvakumar, A; Najafi, K. A high-sensitivity z-axis capacitive silicon microaccelerometer with a torsional suspension. J Micromech Microeng 1998, 7, 192–200. [Google Scholar]

- Wang, C; Tsai, M-H; Sun, C-M; Fang, W. A novel CMOS out-of-plane accelerometer with fully differential gap-closing capacitance sensing electrodes. J Micromech Microeng 2007, 17, 1275–1280. [Google Scholar]

- Kim, JP; Park, S; Kwak, D; Ko, H; Cho, D. An x-axis single-crystalline silicon microgyroscope fabricated by the extended SBM process. J Microelectromechanical Syst 2005, 14, 444–455. [Google Scholar]

- Chae, J; Kulah, H; Najafi, K. A hybrid silicon-on-glass (SOG) lateral micro-accelerometer with CMOS readout circuitry. The 15th International Conference on Micro Electro Mechanical Systems, Las Vegas, NV, USA, January 20–24, 2002; pp. 623–626.

- Sharma, A; Zaman, MF; Ayazi, F. A 104-dB dynamic range transimpedance-based CMOS ASIC for tuning fork microgyroscopes. IEEE J Solid-State Circuits 2007, 42, 1790–1802. [Google Scholar]

- Ko, H; Lee, A; Ahn, T; Paik, S; Choi, B; Cho, D. A 37 ppm/°C temperature compensated CMOS ASIC with ±16 V supply protection for capacitive microaccelerometers. IEEE Custom Integrated Circuits Conference 2007 (CICC '07), San Jose, CA, USA, September 16–19, 2007; pp. 595–598.

- Younis, MI; Alsaleem, FM; Miles, R; Su, Q. Characterization of the performance of capacitive switches activated by mechanical shock. J Micromech Microeng 2007, 17, 1360–1370. [Google Scholar]

- Mariani, S; Ghisi, A; Corigliano, A; Zerbini, S. Multi-scale analysis of MEMS sensors subject to drop impacts. Sensors 2007, 7, 1817–1833. [Google Scholar]

- Leland, RP. Mechanical-thermal noise in MEMS gyroscopes. IEEE Sens J 2005, 5, 493–500. [Google Scholar]

- Song, T; Park, S; Park, Y; Kwak, D; Ko, H; Cho, D. Quality factor in microgyroscopes. Proceeding of Asia-Pacific Conference of Transducers and Micro-Nano Technology, Saporo, Japan, July 4–7, 2004; pp. 916–920.

- Houlihan, R; Kraft, M. Modeling squeeze film effects in a MEMS accelerometer with a levitated proof mass. J Micromech Microeng 2005, 15, 893–902. [Google Scholar]

- Sun, D; Dong, W; Liu, C; Chen, W; Kraft, M. Analysis of the dynamic behavior of a torsional micro-mirror. Microsyst Technol 2007, 13, 61–70. [Google Scholar]

- Minikes, A; Bucher, I; Avivi, G. Damping of a micro-resonator torsion mirror in rarefied gas ambient. J Micromech Microeng 2005, 15, 1762–1769. [Google Scholar]

- Lee, I; Yoon, GH; Park, J; Seok, S; Chun, K; Lee, K. Development and analysis of the vertical capacitive accelerometer. Sens Actuat–A Phys 2005, 119, 8–18. [Google Scholar]

- Palmer, B. Capacitance of a parallel-plate capacitor by the Schwartz-Christoffel transformation. Trans Ame Inst Elec Eng 1937, 56, 363–366. [Google Scholar]

- Liu, R; Paden, B; Turner, K. MEMS resonators that are robust to process-induced feature width variations. J Microelectromech Syst 2002, 11, 505–511. [Google Scholar]

- Hong, YS; Lee, JH; Kim, SH. A laterally driven symmetric micro-resonator for gyroscopic applications. J Micromech Microeng 2000, 10, 452–458. [Google Scholar]

- Fang, D; Xie, H. A low-power low-noise capacitive sensing amplifier for integrated CMOS-MEMS inertial sensors. Proceedings of the International Conference on Circuits, Signals, and Systems, Clearwater Beach, FL, USA, November 28–December 1, 2004; pp. 96–101.

| Parameter | Symbol | Value |

|---|---|---|

| Chip size | 3.4 mm × 2.0 mm | |

| Device layer thickness of (111) SOI wafer | t0 | 65 μm |

| Torsional spring | ||

| Width | wspring | 4 μm |

| Length | lspring | 150 μm |

| Thickness | t | 25 μm (±2 μm) |

| Number of springs | nspring | 2 |

| Torsion angle at 1 g input (at t = 25 μm) | θ | 2.59 × 10−4 rad |

| Comb finger | ||

| Width | w | 5 μm |

| Length | lcomb | 210 μm |

| Thickness | t | 25 μm (±2 μm) |

| Comb overlap length | l | 200 μm |

| Vertical gap length | g | 13 μm (±1 μm) |

| Gap between comb finger | d | 4 μm |

| Effective distance from center to comb finger | l’ | 8.13 × 10−4 m |

| Number of combs | n | 254 |

| MEMS structure | ||

| Area size | - | 9.72 × 10−6 m2 |

| Area of asymmetric part | - | 2.74 × 10−7 m2 |

| Center of mass | xcm | 5.58 × 10−4 m |

| Thickness | t | 25 μm (±2 μm) |

| Device length | a | 2.53 mm |

| Device width | b | 1.388 mm |

| 1st mode natural frequency (at t = 25 μm) | ωn | 598 Hz |

| Sample #1 | Sample #2 | Sample #3 | |

|---|---|---|---|

| Scale factor | 373 mV/g | 372 mV/g | 389 mV/g |

| Non-linearity | 0.60%FSO | 0.59%FSO | 0.43%FSO |

| SNR | 74.00 dB | 74.74 dB | 75.23 dB |

| NER | 180 μg/rtHz | 183 μg/rtHz | 190 μg/rtHz |

| Bias instability | 229 μg | 148 μg | 122 μg |

| Cross-axis sensitivity (x-axis) | 1.3% | 1.9% | 1.1% |

| Cross-axis sensitivity (y-axis) | 0.7% | 0.4% | 0.3% |

© 2010 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license ( http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Lee, S.; Ko, H.; Choi, B.; Cho, D.-i.D. Optimal and Robust Design Method for Two-Chip Out-of-Plane Microaccelerometers. Sensors 2010, 10, 10524-10544. https://doi.org/10.3390/s101210524

Lee S, Ko H, Choi B, Cho D-iD. Optimal and Robust Design Method for Two-Chip Out-of-Plane Microaccelerometers. Sensors. 2010; 10(12):10524-10544. https://doi.org/10.3390/s101210524

Chicago/Turabian StyleLee, Sangmin, Hyoungho Ko, Byoungdoo Choi, and Dong-il Dan Cho. 2010. "Optimal and Robust Design Method for Two-Chip Out-of-Plane Microaccelerometers" Sensors 10, no. 12: 10524-10544. https://doi.org/10.3390/s101210524

APA StyleLee, S., Ko, H., Choi, B., & Cho, D. -i. D. (2010). Optimal and Robust Design Method for Two-Chip Out-of-Plane Microaccelerometers. Sensors, 10(12), 10524-10544. https://doi.org/10.3390/s101210524