CMOS-NEMS Copper Switches Monolithically Integrated Using a 65 nm CMOS Technology

Abstract

:1. Introduction

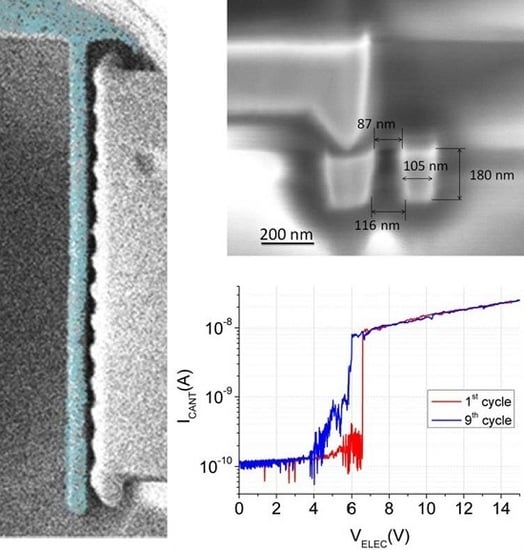

2. CMOS-NEMS Switch Device Design

3. Results and Discussion

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Loh, O.Y.; Espinosa, H.D. Nanoelectromechanical contact switches. Nat. Nanotechnol. 2012, 7, 283–295. [Google Scholar] [CrossRef] [PubMed]

- International Technology Roadmap of Semiconductors 2013. Available online: http://www.itrs.net (accessed on 10 September 2015).

- Peschot, A.; Qian, C.; Liu, T.J.K. Nanoelectromechanical switches for low-power digital computing. Micromachines 2015, 6, 1046–1065. [Google Scholar] [CrossRef]

- Nathanael, R.; Pott, V.; Kam, H.; Jeon, J.; Liu, T.J. 4-terminal relay technology for complementary logic. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; pp. 1–4.

- Jeon, J.; Pott, V.; Kam, H.; Nathanael, R.; Alon, E.; Liu, T.J. Perfectly Complementary Relay Design for Digital Logic Applications. IEEE Electron Device Lett. 2010, 31, 371–373. [Google Scholar] [CrossRef]

- Kaul, A.B.; Wong, E.W.; Epp, L.; Hunt, B.D. Electromechanical carbon nanotube switches for high-frequency applications. Nano Lett. 2006, 6, 942–947. [Google Scholar] [CrossRef] [PubMed]

- Czaplewski, D.A.; Patrizi, G.A.; Kraus, G.M.; Wendt, J.R.; Nordquist, C.D.; Wolfley, S.L.; De Boer, M.P. A nanomechanical switch for integration with CMOS logic. J. Micromech. Microeng 2009, 19, 085003. [Google Scholar] [CrossRef]

- Lee, T.H.; Bhunia, S.; Mehregany, M. Electromechanical computing at 500 °C with silicon carbide. Science 2010, 329, 1316–1318. [Google Scholar] [CrossRef] [PubMed]

- Liu, T.J.K.; Hutin, L.; Chen, I.R.; Nathanael, R.; Chen, Y.; Spencer, M.; Alon, E. Recent progress and challenges for relay logic switch technology. In Proceedings of the 2012 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 12–14 June 2012; pp. 12–14.

- Feng, X.L.; Matheny, M.H.; Zorman, C.A.; Mehregany, M.; Roukes, M.L. Low voltage nanoelectromechanical switches based on silicon carbide nanowire. Nano Lett. 2010, 10, 2891–2896. [Google Scholar] [CrossRef] [PubMed]

- Lee, J.O.; Song, Y.H.; Kim, M.W.; Kang, M.H.; Oh, J.S.; Yang, H.H.; Yoon, J.B. A sub-1-volt nanoelectromechanical switching device. Nat. Nanotechnol. 2013, 8, 36–40. [Google Scholar] [CrossRef] [PubMed]

- Muñoz-Gamarra, J.; Uranga, A.; Barniol, N. NEMS Switches monolithically on CMOS MIM Capacitors. Appl. Phys. Lett. 2014, 104, 243105. [Google Scholar] [CrossRef]

- Muñoz-Gamarra, J.; Vidal-Alvarez, G.; Torres, F.; Uranga, A.; Barniol, N. CMOS-MEMS switches based on back-end metal layers. Microelectron. Eng. 2014, 119, 127–130. [Google Scholar] [CrossRef]

- Liu, T.J.; Xu, N.; Chen, I.R.; Qian, C.; Fujiki, J. NEM relay design for compact, ultra-low-power digital logic circuits. In Proceedings of the 2014 International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014.

- Xu, N.; Sun, J.; Chen, I.R.; Hutin, L.; Chen, Y.; Fujiki, J.; Qian, C.; Liu, T.J. Hybrid CMOS/BEOL-NEMS technology for ultra-low-ower IC applications. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014.

- Chong, S.; Lee, B.; Parizi, K.B.; Provine, J.; Mitra, S.; Howe, R.T.; Wong, H.S. Integration of nanoelectromechanical (NEM) relays with silicon CMOS with functional CMOS-NEM circuit. In Proceedings of the 2011 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2011; pp. 30–35.

- Ramezani, M.; Cosemans, S.; de Coster, J.; Rottenberg, X.; Rochus, V.; Osman, H.; Tilmans, H.A.C.; Severi, S.; De Meyer, K. Submicron three-terminal SiGe-based electromechanical ohmic relay. In Proceedings of the 2014 IEEE 27th International Conference on Micro Electro Mechanical Systems (MEMS), San Francisco, CA, USA, 26–30 January 2014; pp. 1095–1098.

- Lee, J.O.; Kim, M.W.; Ko, S.D.; Kang, H.O.; Bae, W.H.; Kang, M.H.; Kim, K.N.; Yoo, D.E.; Yoon, J.B. 3-terminal nanoelectromechanical switching device in insulating liquid media for low voltage operation and reliability improvement. In Proceedings of the IEEE International Electron Devices Meeting, Baltimore, MD, USA, 7–9 December 2009; pp. 208–211.

- Grogg, D.; Drechsler, U.; Knoll, A.; Duerig, U.; Pu, Y.; Hagleitner, C.; Despont, M. Curved in-plane electromechanical relay for low power logic applications. J. Micromechan. Microeng. 2013, 23, 025024. [Google Scholar] [CrossRef]

- Parsa, R.; Lee, W.S.; Shavezipur, M.; Provine, J.; Maboudian, R.; Mitra, S.; Howe, R.T. Laterally actuated platinum-coated polysilicon NEM relays. J. Microelectromech. Syst. 2013, 22, 768–778. [Google Scholar] [CrossRef]

- ST Microelectronics. Available online: http://www.st.com (accessed on 2 November 2015).

- Verd, J.; Uranga, A.; Abadal, G.; Teva, J.L.; Torres, F.; Lopez, J.; Perez-Murano, E.; Esteve, J.; Barniol, N. Monolithic CMOS MEMS oscillator circuit for sensing in the attogram range. IEEE Electron Device Lett. 2008, 29, 146–148. [Google Scholar] [CrossRef]

- Lopez, J.L.; Verd, J.; Teva, J.; Murillo, G.; Giner, J.; Torres, F.; Uranga, A.; Abadal, G.; Barniol, N. Integration of RF-MEMS resonators on submicrometric commercial CMOS technologies. J. Micromech. Microeng. 2009, 19, 015002. [Google Scholar] [CrossRef]

- Muñoz-Gamarra, J.L.; Alcaine, P.; Marigó, E.; Giner, J.; Uranga, A.; Esteve, J.; Barniol, N. Integration of NEMS resonators in a 65 nm CMOS technology. Microelectron. Eng. 2013, 110, 246–249. [Google Scholar] [CrossRef]

- Kaajakari, V. Practical MEMS; Small Gear Publishing: Las Vegas, NV, USA, 2009. [Google Scholar]

- Eyoum, M.A.; Hoivik, N.; Jahnes, C.; Cotte, J.; Liu, X.H. Analysis and modeling of curvature in copper based MEMS structures fabricated using CMOS interconnect technology. In Proceedings of the 13th International Conference on Solid-State Sensors, Actuators and Microsystems (TRANSDUCERS ’05), Seoul, Korea, 5–9 June 2005; pp. 764–767.

- Abadal, G.; Davis, Z.J.; Helbo, B.; Borrise, X.; Ruiz, R.; Boisen, A.; Campabadal, F.; Esteve, J.; Figueras, E.; Pérez-Murano, F.; et al. Electromechanical model of a resonating nano-cantilever based sensor for high resolution and high sensitivity mass detection. Nanotechnology 2001, 12, 100. [Google Scholar] [CrossRef]

- Molinero, D.; Abelé, N.; Castañer, L.; Ionescu, A. Oxide charging and memory effects in suspended gate FET. In Proceedings of the IEEE 21st International Conference on Micro Electro Mechanical Systems, Tucson, AZ, USA, 13–17 January 2008; pp. 685–688.

- Kam, H.; Pott, V.; Nathanael, R.; Jeon, J.; Alon, E.; Liu, T.J. Design and reliability of a micro-relay technology for zero-standby-power digital logic applications. In Proceedings of the 2009 IEEE International Electron Devices Meeting, Baltimore, MD, USA, 7–9 December 2009.

- Pott, V.; Kam, H.; Nathanael, R.; Jeon, J.; Alon, E.; Liu, T.J. Mechanical Computing Redux: Relays for Integrated Circuit Applications. IEEE Proc. 2010, 98, 2076–2094. [Google Scholar] [CrossRef]

- Marigo, E.; Lopez, J.; Murillo, G.; Torres, F.; Giner, J.; Uranga, A.; Abadal, G.; Esteve, J.; Barniol, N. Zero-level packaging of MEMS in standard CMOS technology. J. Micromech. Microeng. 2010, 20, 064009. [Google Scholar] [CrossRef]

- Kim, R.H.; Kim, B.H.; Matsuda, T.; Kim, J.N.; Baek, J.M.; Lee, J.J.; Cha, J.O.; Hwang, J.H.; Yoo, S.Y.; Chung, K.M.; et al. Highly reliable Cu interconnect strategy for 10nm node logic technology and beyond. In Proceedings of the 2014 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014.

© 2016 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons by Attribution (CC-BY) license ( http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Muñoz-Gamarra, J.L.; Uranga, A.; Barniol, N. CMOS-NEMS Copper Switches Monolithically Integrated Using a 65 nm CMOS Technology. Micromachines 2016, 7, 30. https://doi.org/10.3390/mi7020030

Muñoz-Gamarra JL, Uranga A, Barniol N. CMOS-NEMS Copper Switches Monolithically Integrated Using a 65 nm CMOS Technology. Micromachines. 2016; 7(2):30. https://doi.org/10.3390/mi7020030

Chicago/Turabian StyleMuñoz-Gamarra, Jose Luis, Arantxa Uranga, and Nuria Barniol. 2016. "CMOS-NEMS Copper Switches Monolithically Integrated Using a 65 nm CMOS Technology" Micromachines 7, no. 2: 30. https://doi.org/10.3390/mi7020030

APA StyleMuñoz-Gamarra, J. L., Uranga, A., & Barniol, N. (2016). CMOS-NEMS Copper Switches Monolithically Integrated Using a 65 nm CMOS Technology. Micromachines, 7(2), 30. https://doi.org/10.3390/mi7020030