Marmote SDR: Experimental Platform for Low-Power Wireless Protocol Stack Research

Abstract

:1. Introduction

2. Background and Related Work

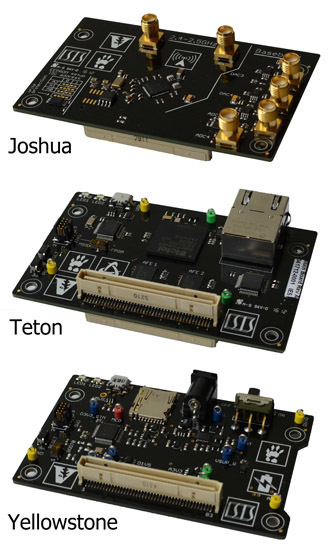

3. Hardware Design

3.1. 2.4 GHz Radio Front-End

3.2. Mixed-Signal Processing Module

3.3. Power Management Module

4. Hardware Evaluation

4.1. Development Framework

4.2. Power Consumption

| Component | Logic Utilization |

|---|---|

| APB interface | 1,469 (12.7%) |

| AFE interface | 52 (0.5%) |

| FSK application | 1,882 (16.3%) |

| Total | 3,403 (29.5%) |

5. Communication Protocol Design

- Collision-free multiple-access scheme that allows for simultaneous packet transmissions and reduced packet losses, due to multiple access interference

- Asynchronous, contention-free medium access that requires no synchronization (scheduling) between sensor nodes

- Asymmetric communication link shifts the processing burden from sensor nodes to the base station (simple transmitter and complex receiver architecture)

- Rejection of narrowband interference and jamming

5.1. PHY Layer Description

5.1.1. Frame Format

| PHY Header | PHY Payload | |||

|---|---|---|---|---|

| Sync pattern | Source address | Sequence number | Payload data | CRC 16 |

| 2 | 1 | 2 | 15 | 2 |

5.1.2. Spreading and Modulation

5.1.3. Transmitter Design

| Component | Logic Utilization |

|---|---|

| DSSS transmitter | 1,624 (14.1%) |

| Chip filter | 3,272 (28.4%) |

| Total | 4,896 (42.5%) |

5.1.4. Receiver Design

5.2. Evaluation

5.2.1. Experiment Setup

5.2.2. Results

6. Conclusions

Acknowledgments

Conflicts of Interest

References

- Crossbow. Crossbow MICAz (MPR2400) Radio Module. Available online: http://www.xbow.com (accessed on 1 June 2013).

- Polastre, J.; Szewczyk, R.; Culler, D. Telos: Enabling Ultra-Low Power Wireless Research. In Proceedings of the Fourth International Symposium on Information Processing in Sensor Networks (IPSN 2005), Los Angeles, CA, USA, 15 April 2005.

- Bachir, A.; Dohler, M.; Watteyne, T.; Leung, K.K. MAC essentials for wireless sensor networks. IEEE Commun. Surv. Tutor. 2010, 12, 222–248. [Google Scholar] [CrossRef]

- Texas Instruments. Chipcon AS, CC1000: Single Chip very Low Power RF transceiver. 2004. Available online: www.ti.com/lit/ds/symlink/cc1000.pdf (accessed on 1 June 2013).

- Texas Instruments. CC2420: 2.4 GHz IEEE 802.15.4 / ZigBee-Ready RF Transceiver. 2007. Available online: http://www.ti.com/lit/ds/symlink/cc2420.pdf (accessed on 1 June 2013).

- Ali, M.; Saif, U.; Dunkels, A.; Voigt, T.; Römer, K.; Langendoen, K.; Polastre, J.; Uzmi, Z.A. Medium access control issues in sensor networks. Comput. Commun. Rev. 2006, 36, 33–36. [Google Scholar] [CrossRef]

- Neufeld, M.; Fifield, J.; Doerr, C.; Sheth, A.; Grunwald, D. SoftMAC—Flexible Wireless Research Platform. In Proceedings of the Fourth Workshop on Hot Topics in Networks HotNetsIV, College Park, MD, USA, 14 November 2005.

- Blossom, E. GNU radio: Tools for exploring the radio frequency spectrum. Linux J. 2004, June 2004(122), 4. [Google Scholar]

- Ettus Research. USRP N210. Available online: https://www.ettus.com/product/details/UN210-KIT (accessed on 1 June 2013).

- Xilinx Inc. Xilinx System Generator for DSP. Available online: http://www.xilinx.com/tools/sysgen.htm (accessed on 1 June 2013).

- Ahola, T.; Korpinen, P.; Rakkola, J.; Ramo, T.; Salminen, J.; Savolainen, J. Wearable FPGA Based Wireless Sensor Platform. In Proceedings of the 29th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBS 2007), Lyon, France, 23–26 August 2007; pp. 2288–2291.

- Hayek, A.; Machmur, B.; Suna, Y.; Borcsok, J. FPGA-Based Wireless Sensor Network Platform for Safety Systems. In Proceedings of the IEEE 19th International Conference on Telecommunications (ICT), Jounieh, Lebanon, 23–25 April 2012; pp. 1–6.

- Völgyesi, P.; Balogh, G.; Nádas, A.; Nash, C.; Lédeczi, A. Shooter Localization and Weapon Classification with Soldier-Wearable Networked Sensors. In Proceedings of the 5th International Conference on Mobile Systems, Applications, and Services (MobiSys), San Juan, Puerto Rico, 11–14 June 2007.

- Valverde, J.; Otero, A.; Lopez, M.; Portilla, J.; de la Torre, E.; Riesgo, T. Using SRAM based FPGAs for power-aware high performance wireless sensor networks. Sensors 2012, 12, 2667–2692. [Google Scholar] [CrossRef] [PubMed]

- SDR4All. Flexible Radio Platform. Available online: http://www.flexible-radio.com/sdr4all (accessed on 1 June 2013).

- OSmoSDR. OsmoSDR Project. Available online: http://sdr.osmocom.org (accessed on 1 June 2013).

- Ledeczi, A.; Hay, T.; Volgyesi, P.; Hay, D.; Nadas, A.; Jayaraman, S. Wireless acoustic emission sensor network for structural monitoring. IEEE Sens. J. 2009, 9, 1370–1377. [Google Scholar] [CrossRef]

- Nylanden, T.; Janhunen, J.; Hannuksela, J.; Silven, O. FPGA Based Application Specific Processing for Sensor Nodes. In Proceedings of the IEEE 2011 International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation, Samos, Greece, 18–21 July 2011; pp. 118–123.

- Philipp, F.; Glesner, M. Mechanisms and Architecture for the Dynamic Reconfiguration of an Advanced Wireless Sensor Node. In Proceedings of the 2011 International Conference on Field Programmable Logic and Applications (FPL), Crete, Greece, 5–7 September 2011; pp. 396–398.

- Kuo, Y.S.; Pannuto, P.; Schmid, T.; Dutta, P. Reconfiguring the Software Radio to Improve Power, Price, and Portability. In Proceedings of the 10th ACM Conference on Embedded Networked Sensor Systems (Sensys’12), Toronto, ON, Canada, 6–9 November 2012.

- Szilvási, S.; Sallai, J.; Amundson, I.; Völgyesi, P.; Lédeczi, Á. Configurable Hardware-based Radio Interferometric Node Localization. In Proceedings of the 2010 IEEE Aerospace Conference, Big Sky, MT, USA, 6–13 March 2010.

- Microsemi. Total System Power. Available online: http://www.actel.com/documents/Power_PIB.pdf (accessed on 1 June 2013).

- Microsemi. IGLOO Low Power Flash FPGAs with Flash*Freeze Technology. Available online: http://www.actel.com/documents/IGLOO_DS.pdf (accessed on 1 June 2013).

- Simon, M.K.; Omura, J.K.; Sholtz, R.A.; Levitt, B.K. Spread Spectrum Communications Handbook; Electronic communications, McGraw-Hill Professional Publishing: New York, NY, USA, 1994; pp. 283–284. [Google Scholar]

- Geraniotis, E. Performance of noncoherent direct-sequence spread-spectrum multiple-access communications. IEEE J. Sel. Areas Commun. 1985, 3, 687–694. [Google Scholar] [CrossRef]

- Marmote SDR Platform. Marmote low-power FPGA-based platform. Available online: http://marmote.googlecode.com (accessed on 1 June 2013).

© 2013 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Szilvási, S.; Babják, B.; Völgyesi, P.; Lédeczi, Á. Marmote SDR: Experimental Platform for Low-Power Wireless Protocol Stack Research. J. Sens. Actuator Netw. 2013, 2, 631-652. https://doi.org/10.3390/jsan2030631

Szilvási S, Babják B, Völgyesi P, Lédeczi Á. Marmote SDR: Experimental Platform for Low-Power Wireless Protocol Stack Research. Journal of Sensor and Actuator Networks. 2013; 2(3):631-652. https://doi.org/10.3390/jsan2030631

Chicago/Turabian StyleSzilvási, Sándor, Benjámin Babják, Péter Völgyesi, and Ákos Lédeczi. 2013. "Marmote SDR: Experimental Platform for Low-Power Wireless Protocol Stack Research" Journal of Sensor and Actuator Networks 2, no. 3: 631-652. https://doi.org/10.3390/jsan2030631

APA StyleSzilvási, S., Babják, B., Völgyesi, P., & Lédeczi, Á. (2013). Marmote SDR: Experimental Platform for Low-Power Wireless Protocol Stack Research. Journal of Sensor and Actuator Networks, 2(3), 631-652. https://doi.org/10.3390/jsan2030631