Design of a Reduced SpaceFibre Interface: An Enabling Technology for Low-Cost Spacecraft High-Speed Data-Handling

Abstract

:1. Introduction

2. R-SpaceFibre Design: Features and Trade-Offs

- The Network layer is responsible for transferring both data and broadcast messages through the SpaceFibre network.

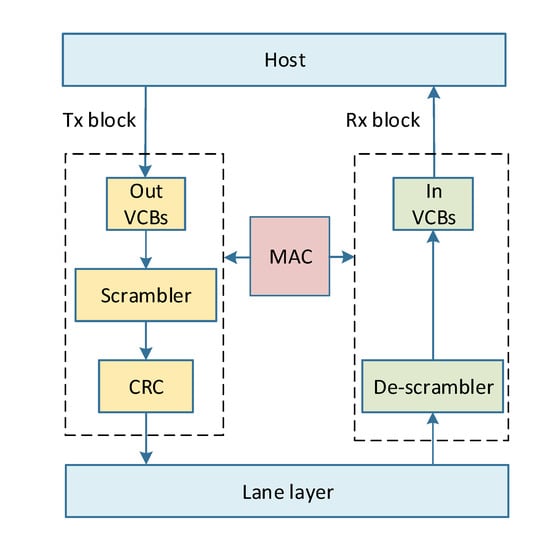

- The Data Link layer is responsible for the FDIR system that implements a retry mechanism to resend corrupted frames. Moreover, it handles independent flow of information through Virtual Channel Buffers (VCBs), and it manages the QoS, broadcast service and data scrambling.

- The Multi lane layer is responsible for synchronising a link composed by more than 1 lane (up to 16). This is an optional layer.

- The Lane layer is responsible for establishing the communication between two ends.

- The Physical layer is responsible for serialising, transmitting, receiving and de-serialising data.

2.1. SpaceFibre Data Link Layer

2.2. R-SpaceFibre Data Link Layer

- Retry buffers, from the Tx Block

- Broadcast service, from the entire Data link Layer

- CRC check block, from the Rx Block

- Several QoS mechanism, from the MAC

2.3. Fault Tolerance and Compatibility with Full SpaceFibre Interfaces

3. Hardware Implementation

3.1. Hardware Setup and Tests

- CODEC 0 is a R-SpaceFibre CODEC and CODEC 1 is a SpaceFibre CODEC (CONFIG1);

- CODEC 0 and CODEC 1 are both R-SpaceFibre CODECs (CONFIG2).

3.2. Resources Utilisation and Power Consumption

4. R-SpaceFibre Use Case Scenario: CubeSats

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| BC | broadcast |

| CDH | Command and Data handling |

| CIRES | CubeSat Imaging Radar for Earth Science |

| COTS | Commercial-Off-The-Shelf |

| CRC | Cyclic Redundancy Check |

| ECSS | European Cooperation for Space Standardization |

| EGSE | Electrical Ground Segment Equipments |

| ESA | European Space Agency |

| FCT | Flow Control Token |

| FDIR | Fault Detection Isolation and Recovery |

| FPGA | Field Programmable Gate Array |

| In BCB | In Broadcast Channel Buffer |

| InSAR | Interferometric SAR |

| IP | Intellectual Property |

| JAXA | Japan Aerospace eXploration Agency |

| JPL | Jet Propulsion Laboratory |

| LEO | Low Earth Orbit |

| LUT | Look-Up-Tables |

| MAC | Medium Access Controller |

| NASA | National Aeronautics and Space Administration |

| Out BCB | Out Broadcast Channel Buffer |

| QoS | Quality of Service |

| Reg | register |

| SAR | Synthetic Aperture Radars |

| VC | Virtual Channel |

| VCB | Virtual Channel Buffers |

References

- Parkes, S.; McClements, C.; McLaren, D.; Florit, A.F.; Villafranca, A.G. SpaceFibre: A multi-Gigabit/s interconnect for spacecraft onboard data handling. In Proceedings of the 2015 IEEE Aerospace Conference, Big Sky, MT, USA, 7–14 March 2015. [Google Scholar]

- SpaceFibre Standard, ECSS-E-ST-50-11C-DIR1. Available online: http://ecss.nl/standard/ecss-e-st-50-11c-dir1/ (accessed on 5 May 2019).

- Parkes, S.; Armbruster, P. SpaceWire A Spacecraft Onboard Network for Real-Time Communications. In Proceedings of the 14th IEEE-NPSS Real Time Conference, Stockholm, Sweden, 4–10 June 2005. [Google Scholar]

- Saponara, S.; Fanucci, L.; Tonarefli, M.; Petri, E. Radiation Tolerant SpaceWire Router for Satellite On-Board Networking. IEEE Aeros. Electron. Syst. Mag. 2017, 22, 3–12. [Google Scholar] [CrossRef]

- Mason, A.; Parkes, S. Using SpaceWire with LabVIEW. In Proceedings of the 2014 International SpaceWire Conference, Athens, Greece, 22–26 September 2014. [Google Scholar]

- Rivera, J.P.; Sabater, N.; Tenjo, C.; Vicen, J.; Alonso, L.; Moreno, J. Synthetic scene simulator for hyperspectral spaceborne passive optical sensors. Application to ESA’s FLEX/sentinel-3 tandem mission. In Proceedings of the 2014 6th Workshop on Hyperspectral Image and Signal Processing: Evolution in Remote Sensing (WHISPERS), Lausanne, Switzerland, 24–27 June 2014. [Google Scholar]

- Toan, T.L.; Chave, J.; Dall, J.; Papathanassiou, K.; Paillou, P.; Rechstein, M.; Quegan, S.; Saatchi, S.; Seipel, K.; Shugart, H.; et al. The Biomass Mission: Objectives and Requirements. In Proceedings of the 2018 IEEE International Geoscience and Remote Sensing Symposium, Valencia, Spain, 22–27 July 2018. [Google Scholar]

- Koga, R.; Yu, P.; George, J. Single Event Effects and Total Dose Test Results for TI TLK2711 Transceiver. In Proceedings of the 2008 IEEE Radiation Effects Data Workshop, Tucson, AZ, USA, 14–18 July 2008; pp. 69–75. [Google Scholar]

- Fuller, S.; Cox, T. Anatomy of a Forward-Looking Open Standard. Computer 2002, 35, 140–141. [Google Scholar] [CrossRef]

- Kopetz, H.; Ademaj, A.; Grillinger, P.; Steinhammer, K. The Time-Triggered Ethernet (TTE) Design. In Proceedings of the 8th IEEE International Symposium on Object-Oriented Real-Time Distributed Computing, Auckland, New Zealand, 13–17 April 2015. [Google Scholar]

- Davalle, D.; Leoni, A.; Dello Sterpaio, L.; Fanucci, L. Design and implementation of test equipment for SpaceFibre links: SpaceFibre. In Proceedings of the 7th International SpaceWire Conference, Yokohama, Japan, 25–27 October 2016; pp. 1–5. [Google Scholar]

- Siegle, F.; Habinc, S.; Both, J. SpaceFibre Port IP Core (GRSPFI): SpaceFibre, poster paper. In Proceedings of the 7th International SpaceWire Conference, Yokohama, Japan, 25–27 October 2016. [Google Scholar]

- Leoni, A.; Nannipieri, P.; Fanucci, L. VHDL Design of a SpaceFibre Routing Switch. IEICE Trans. Fundam. Electron. Commun. Comput. Sci. 2019, E102-A, 729–731. [Google Scholar] [CrossRef]

- Parkes, S.; Florit, A.F.; Villafranca, A.G.; McClements, C.; McLaren, D. SpaceFibre network and routing switch. In Proceedings of the 2017 IEEE Aerospace Conference, Big Sky, MT, USA, 4–11 March 2017; pp. 1–7. [Google Scholar]

- Leoni, A.; Nannipieri, P.; Davalle, D.; Fanucci, L.; Jameux, D. SHINe: Simulator for Satellite on-Board High-Speed Networks Featuring SpaceFibre and SpaceWire Protocols. Aerospace 2019, 6, 43. [Google Scholar] [CrossRef]

- CubeSat Design Specification Rev. 12. 2009. Available online: http://www.cubesat.org/resources/ (accessed on 5 May 2019).

- Rowlings, M.; Suess, M. An Experimental Evaluation of SpaceFibre Resource Requirements. In Proceedings of the 2014 International SpaceWire Conference, Athens, Greece, 22–26 September 2014. [Google Scholar]

- Nannipieri, P.; Dinelli, G.; Davalle, D.; Fanucci, L. A SpaceFibre multi lane codec System on a Chip: Enabling technology for low cost satellite EGSE. In Proceedings of the PRIME 2018—14th Conference on Ph.D. Research in Microelectronics and Electronics, Prague, Czech Republic, 2–5 July 2018; 8430317. pp. 173–176. [Google Scholar]

- Parkes, S.; McClements, C.; McLaren, D.; Youssef, B.; Ali, M.S.; Florit, A.F.; Villafranca, A.G. SpaceWire and SpaceFibre on the Microsemi RTG4 FPGA. In Proceedings of the 2016 IEEE Aerospace Conference, Big Sky, MT, USA, 5–12 March 2016; pp. 1–8. [Google Scholar]

- Koopman, P.; Chakravarty, T. Cyclic Redundancy Code (CRC) Polynomial Selection for Embedded Networks. In Proceedings of the International Conference on Dependable Systems and Networks, Florence, Italy, 28 June–1 July 2004; pp. 145–154. [Google Scholar]

- ZC706 Evaluation Board for the Zynq-7000 XC7Z045 All Programmable SoC User Guide. Available online: https://www.xilinx.com/support/documentation/boardsandkits/zc706/ug954-zc706-eval-board-xc7z045-ap-soc.pdf (accessed on 5 May 2019).

- FM-XM104 Connectivity Card User Guide. Available online: https://www.xilinx.com/support/documentation/boardsandkits/ug536.pdf (accessed on 5 May 2019).

- St. Louis University CubeSat Database. Available online: https://sites.google.com/a/slu.edu/swartwout/ home/cubesat-database#plots (accessed on 5 May 2019).

- Poghosyan, A.; Golkar, A. CubeSat evolution: Analyzing CubeSat capabilities for conducting science missions. Prog. Aerosp. Sci. 2017, 88, 59–83. [Google Scholar] [CrossRef]

- Kahn, P.; Imken, T.; Elliott, J.; Sherwood, B.; Frick, A.; Sheldon, D.; Lunine, J. Environmental design implications for two deep space SmallSats. Acta Astronaut. 2017, 139, 390–395. [Google Scholar] [CrossRef]

- Cohen, B.A.; Hayne, P.O.; Greenhagen, B.T.; Paige, D.A. Lunar Flashlight: Exploration and science at the moon with a 6U CubeSat. In Proceedings of the 2015 Annual Meeting of the Lunar Exploration Analysis Group, Columbia, MD, USA, 20–22 October 2015. [Google Scholar]

- McNutt, L.; Johnson, L.; Clardy, D.; Castillo-Rogez, J.; Frick, A.; Jones, L. Near-Earth Asteroid Scout. In Proceedings of the AIAA Space 2014 Conference and Exposition, San Diego, CA, USA, 4–7 August 2014. [Google Scholar]

- IngeniArs SpaceWire. Available online: https://www.ingeniars.com/ (accessed on 5 May 2019).

- StarDundee SpaceWire. Available online: https://www.star-dundee.com/ (accessed on 5 May 2019).

- SpaceWire Cable Datasheet. Available online: http://www.axon-cable.com/publications/HIGH-SPEED-LINKS.pdf (accessed on 5 May 2019).

- SpaceFibre Cable Datasheet. Available online: http://www.axon-cable.com/publications/High_Speed_Links-SPACEFIBRE.pdf (accessed on 5 May 2019).

- Wye, L.; Lee, S. SRI CubeSat imaging radar for earth science (SRI-CIRES). In Proceedings of the 2016 Earth Science Technology Forum, Annapolis, MD, USA, 14–16 June 2016. [Google Scholar]

- Capella CubeSat. Available online: https://www.capellaspace.com/ (accessed on 5 May 2019).

- Iceye CubeSat. Available online: https://www.iceye.com/resources/technology/ (accessed on 5 May 2019).

- Intuition CubeSat. Available online: https://www.fpspace.com/en (accessed on 5 May 2019).

- Hypercube CubeSat. Available online: https://www.harris.com/sites/default/files/downloads/ solutions/55493_hypercube_data_sheet_v2_2_final_.pdf (accessed on 5 May 2019).

- Waypoint CubeSat. Available online: http://www.spacefab.us/space-telescopes.html (accessed on 5 May 2019).

| FPGA | VC | LUT | util% LUT | DFF | util% DFF | BlockRAM-FIFO |

|---|---|---|---|---|---|---|

| Zynq-7000 | 1 | 1675 | 0.73% | 1791 | 0.4% | 1.5 |

| 2 | 2248 | 1% | 2345 | 0.5% | 2 | |

| Virtex 5 | 1 | 1682 | 2.05% | 1103 | 1.35% | 2 |

| 2 | 2662 | 3.25% | 1653 | 2.02% | 4 | |

| Microsemi RTG4 | 1 | 2561 | 2.07% | 1227 | 1.19% | 16 |

| 2 | 4122 | 3.47% | 1892 | 2.00% | 32 | |

| Microsemi RTAX2000 | 1 | 3479 | 16.18 % | 1530 | 14.23% | 4 |

| 2 | 5356 | 24.91% | 2641 | 24.56% | 8 |

| CODEC | RTAX2000 | RTG4 | Zynq-7000 | Virtex 5 | ||||

|---|---|---|---|---|---|---|---|---|

| LUT | util% | LUT | util% | LUT | util% | LUT | util% | |

| SpaceFibre | 5830 | 27.11% | 4632 | 3,98% | 2800 | 1.28% | 2919 | 3.56% |

| R-SpaceFibre | 3479 | 16.18% | 2561 | 2,07% | 1675 | 0.73% | 1682 | 2.05% |

| % Reduction | 2351 | 40.33% | 2071 | 44,71% | 1125 | 40.18% | 1237 | 42.39% |

| DFF | util% | DFF | util% | DFF | util% | DFF | util% | |

| SpaceFibre | 2605 | 24.23% | 1994 | 2,24% | 2441 | 0.56% | 1702 | 2.08% |

| R-SpaceFibre | 1530 | 14.23% | 1227 | 1,19% | 1791 | 0.4% | 1103 | 1.35% |

| % Reduction | 1075 | 41.27% | 767 | 38,46% | 650 | 26.63% | 599 | 35.20% |

| RAM | util% | RAM | util% | RAM | util% | RAM | util% | |

| SpaceFibre | 12 | 18.75% | 39 | 1,10% | 5.5 | 1.28% | 7 | 2.35% |

| R-SpaceFibre | 4 | 6.25% | 16 | 0,45% | 1.5 | 0.28% | 2 | 0.67% |

| % Reduction | 8 | 66.66% | 23 | 58,97% | 4 | 72.72% | 5 | 71.42% |

| CODEC | Dynamic Power (mW) | Static Power (mW) | Total Power (mW) |

|---|---|---|---|

| R-SpaceFibre | 49 | 199 | 248 |

| SpaceFibre | 55 | 199 | 254 |

| Resources | R-SpaceFibre | 4 SpW (IngeniArs) | 4 SpW (STAR-Dundee) |

|---|---|---|---|

| LUT | 16.18% | 11.88% | 7.16% |

| DFF | 14.23% | 14.12% | 17.22% |

| Block RAM | 4 | 8 | 8 |

| Solution | Number of Cables | Mass (g/m) |

|---|---|---|

| R-SpaceFibre | 1 | 15 |

| 4 SpaceWire | 4 | 168 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Dinelli, G.; Nannipieri, P.; Davalle, D.; Fanucci, L. Design of a Reduced SpaceFibre Interface: An Enabling Technology for Low-Cost Spacecraft High-Speed Data-Handling. Aerospace 2019, 6, 101. https://doi.org/10.3390/aerospace6090101

Dinelli G, Nannipieri P, Davalle D, Fanucci L. Design of a Reduced SpaceFibre Interface: An Enabling Technology for Low-Cost Spacecraft High-Speed Data-Handling. Aerospace. 2019; 6(9):101. https://doi.org/10.3390/aerospace6090101

Chicago/Turabian StyleDinelli, Gianmarco, Pietro Nannipieri, Daniele Davalle, and Luca Fanucci. 2019. "Design of a Reduced SpaceFibre Interface: An Enabling Technology for Low-Cost Spacecraft High-Speed Data-Handling" Aerospace 6, no. 9: 101. https://doi.org/10.3390/aerospace6090101

APA StyleDinelli, G., Nannipieri, P., Davalle, D., & Fanucci, L. (2019). Design of a Reduced SpaceFibre Interface: An Enabling Technology for Low-Cost Spacecraft High-Speed Data-Handling. Aerospace, 6(9), 101. https://doi.org/10.3390/aerospace6090101