A Complete EGSE Solution for the SpaceWire and SpaceFibre Protocol Based on the PXI Industry Standard †

Abstract

:1. Introduction

1.1. Background Knowledge

1.2. Satellite On-Board Data-Handling Electrical Ground Segment Equipment

- data processing, recording, and playback: to emulate a SpaceWire or SpaceFibre device, which will be interacting with the DUT;

- bandwidth saturation: producing and/or consuming data at a controllable rate;

- unobtrusive monitoring to watch over two nodes without meddling with the link;

- error-injection: to verify corner scenarios either of very circumstantial occurrences (i.e., radiation- induced Bit Error Rate (BER)) or hazardous scenarios for people or property.

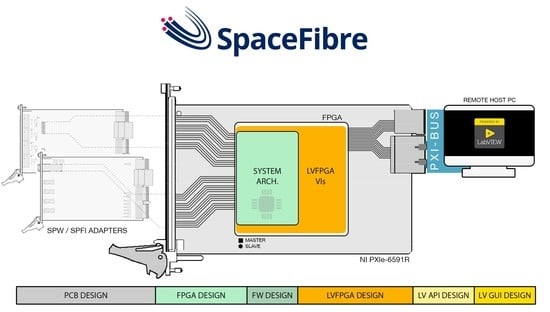

2. Proposed Architecture and Design

- up to four standard compliant SPW ports;

- up to eight standard compliant SPFI ports;

- eight SPFI Virtual-Channels (VC) per port;

- point-to-point codec interfaces or router IP configurations;

- real-time link status monitoring and control;

- real-time link protocol error report and counter by type;

- SPW/SPFI bridged communication;

- in-hardware packet generation/consumption;

- in-link error injection capabilities;

- word-replacement capabilities over traffic;

- Transmission/Reception (TX/RX) trace memory with triggerable events;

- unobtrusive low level link-analysis monitoring;

- real-time communication with remote-host PC via PXI connection;

- LabVIEW API library package;

- a ready-to-use general purpose LabVIEW Graphical User Interface (GUI) application.

2.1. Hardware Design

2.1.1. PCB Design

2.1.2. FPGA Design

- expose link related statuses and internal signals;

- SPFI/SPW traffic generation/consumption, forwarding, and recording;

- control/data character sniffing and trace back recording;

- low level and high level error injection capabilities (bit flips, control/data characters replacement, error packet termination);

- unobtrusive monitoring of a link between two ports.

2.2. Software Design

3. PXI Workflow

4. Results and Use Cases

4.1. Results

4.2. Testing

4.2.1. SPFI Validation Tests

4.2.2. SPW Real-Time CRC Calculation and Fly Back

4.2.3. SPW Real-Time Full Bandwidth Saturation and Data Logging

4.2.4. Device Emulation

4.2.5. SPFI/SPW Performance Test

4.2.6. SPFI/SPW Bridging Test

4.3. Real In-Field Use Case

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| API | Application Programming Interface |

| BD | Block Diagram |

| CLIP | Component-Level IP |

| COTS | Commercial-Off-The-Shelf |

| CRC | Cyclic Redundancy Check |

| CTX | Context |

| DMA | Direct Memory Access |

| ECSS | European Cooperation for Space Standardization |

| EDIF | Electronic Design Interchange Format |

| EGSE | Electrical Ground Segment Equipments |

| ESA | European Space Agency |

| FCT | Flow Control Token |

| FP | Front-Panel |

| FDIR | Fault Detection Isolation and Recovery |

| FPGA | Field Programmable Gate Array |

| GUI | Graphical User Interface |

| HDL | Hardware Description Language |

| HW | Hardware |

| IF | Interface |

| IP | Intellectual Property |

| JAXA | Japan Aerospace eXploration Agency |

| LUT | Look-Up-Tables |

| LV | LabVIEW |

| LVDS | Low-Voltage Differential Signaling |

| LVFPGA | LabVIEW FPGA |

| MAC | Medium Access Controller |

| NASA | National Aeronautics and Space Administration |

| PC | Personal Computer |

| PCB | Printed Circuit Board |

| OOC | Out Of Context |

| QoS | Quality of Service |

| RAM | Random Access Memory |

| Reg | Register |

| RX | Reception, received |

| SAR | Synthetic Aperture Radars |

| SckCLIP | Socketed CLIP |

| SPFI | SpaceFibre |

| SPW | SpaceWire |

| SW | Software |

| TX | Transmission, transmitter |

| VC | Virtual Channel |

| VCB | Virtual Channel Buffers |

| VI | Virtual Instrument |

References

- Dello Sterpaio, L.; Nannipieri, P.; Marino, A.; Fanucci, L. Design of a SpaceWire/SpaceFibre EGSE System Based on PXI Industry Standard. In Proceedings of the IEEE International Workshop on Metrology for AeroSpace (MetroAeroSpace), Turin, Italy, 19–21 June 2019. [Google Scholar]

- Space AVionics Open Interface aRchitecture (SAVOIR). SAVOIR On-Board Communication System Requirement Document. SAVOIR-GS-008; SAVOIR, ESA. Available online: http://savoir.estec.esa.int/SAVOIRDocuments.htm (accessed on 15 November 2019).

- Parkes, S.; Armbruster, P. SpaceWire A Spacecraft Onboard Network for Real-Time Communications. In Proceedings of the 14th IEEE-NPSS Real Time Conference, Stockholm, Sweden, 4–10 June 2005. [Google Scholar]

- SpaceWire Standard ECSS-E-ST-50-12C. Available online: https://ecss.nl/standard/ecss-e-st-50-12c-spacewire-links-nodes-routers-and-networks/ (accessed on 4 October 2019).

- Saponara, S.; Fanucci, L.; Tonarefli, M.; Petri, E. Radiation Tolerant SpaceWire Router for Satellite On-Board Networking. IEEE Aerosp. Electron. Syst. Mag. 2017, 22, 3–12. [Google Scholar] [CrossRef]

- SpaceFibre Standard, ECSS-E-ST-50-11C. Available online: http://ecss.nl/standard/ecss-e-st-50-11c-dir1/ (accessed on 4 October 2019).

- Dinelli, G.; Nannipieri, P.; Davalle, D.; Fanucci, L. Design of a reduced SpaceFibre interface: An enabling technology for low-cost spacecraft high-speed data-handling. Aerospace 2019, 6, 101. [Google Scholar] [CrossRef]

- Leoni, A.; Nannipieri, P.; Fanucci, L. VHDL Design of a SpaceFibre Routing Switch. IEICE Trans. Fundam. Electron. Commun. Comput. Sci. 2019, E102-A, 729–731. [Google Scholar] [CrossRef]

- Leoni, A.; Nannipieri, P.; Davalle, D.; Fanucci, L.; Jameux, D. SHINe: Simulator for Satellite on-Board High-Speed Networks Featuring SpaceFibre and SpaceWire Protocols. Aerospace 2019, 6, 43. [Google Scholar] [CrossRef]

- Eramo, V.; Lavacca, F.G.; Listanti, M.; Caporossi, S. Definition and performance evaluation of an Advanced Avionic TTEthernet Architecture for the support of Launcher Networks. IEEE Aerosp. Electron. Syst. Mag. 2018, 33, 30–43. [Google Scholar] [CrossRef]

- Eramo, V.; Lavacca, F.G.; Valente, F.; Pisculli, A.; Caporossi, S. Simulation and experimental evaluation of a flexible time triggered ethernet architecture applied in satellite Nano/Micro Launchers. Aerospace 2018, 5, 84. [Google Scholar] [CrossRef] [Green Version]

- PXISA. PXI-1 Hardware Specifications, Rav. 2.2; PXISA: Niwot, CO, USA, 2004. [Google Scholar]

- Marino, A.; Dello Sterpaio, L.; Fanucci, L. Design and implementation of a complete test equipment solution for SpaceWire links. In Proceedings of the 2018 14th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Prague, Czech Republic, 2–5 July 2018. [Google Scholar]

- Nannipieri, P.; Dello Sterpaio, L.; Marino, A.; Fanucci, L. A PXI based implementation of a TLK2711 equivalent interface. In Application in Electronics Pervading Industry, Environment and Society (ApplEPIES); Elsevier: Pisa, Italy, 2018. [Google Scholar]

- StarFire MK3. Available online: https://www.star-dundee.com/products/star-fire-mk3 (accessed on 7 October 2019).

- SpaceART. SpaceWire/SpaceFibre Analyser Real-Time. Available online: https://www.ingeniars.com/english/products/space/spaceart-en.html (accessed on 7 October 2019).

- Nannipieri, P.; Dinelli, G.; Davalle, D.; Fanucci, L. A SpaceFibre multi lane codec System on a Chip: Enabling technology for low cost satellite EGSE. In Proceedings of the PRIME 2018 14th Conference on Ph.D. Research in Microelectronics and Electronics, Prague, Czech Republic, 2–5 July 2018; pp. 173–176. [Google Scholar]

- Dello Sterpaio, L.; Marino, A.; Nannipieri, P.; Fanucci, L. Exploiting LabVIEW FPGA Socketed CLIP to Design and Implement Soft-Core Based Complex Digital Architectures on PXI FPGA Target Boards. In Proceedings of the 2019 International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Lausanne, Switzerland, 15–18 July 2019. [Google Scholar]

- AMBA AXI and ACE Protocol Specifications, Issue, D; ARM Holdings: Cambridge, UK, 2011.

- PXIe-6591. PXI High-Speed Serial Instrument. Available online: https://www.ni.com/en-us/support/model. pxie-6591.html (accessed on 7 October 2019).

- Dello Sterpaio, L.; Marino, A.; Nannipieri, P.; Dinelli, G.; Fanucci, L. AXI4LV: Design and Implementation of a Full-Speed AMBA AXI4-Burst DMA Interface for LabVIEW FPGA. In Proceedings of the 2019 Applications in Electronics Pervading Industry, Environment and Society (ApplePies), Pisa, Italy, 11–13 September 2019. [Google Scholar]

- LabVIEW Core 3. Available online: http://sine.ni.com/tacs/app/overview/p/ap/of/lang/en/pg/1/sn/n24:12754/id/1584/ (accessed on 7 October 2019).

| Resource | Usage | Availability | Ratio | Each SPW Codec | Each SPFI Codec |

|---|---|---|---|---|---|

| Block RAM | 420 | 795 | 52.83% | 32 (4.03%) | 40 (5.03%) |

| LUT | 85,380 | 254,200 | 33.59% | 3752 (1.48%) | 11,621 (4.57%) |

| GTX | 4 | 16 | 25.00% | 0 (0%) | 1 (6.25%) |

| FF Registers | 83,644 | 508,400 | 16.45% | 2416 (0.48%) | 8958 (1.76%) |

| EGSE System | SPFI/SPW Bandwidth | SPW Ports | SPFI Ports | Host IF | User Experience |

|---|---|---|---|---|---|

| Proposed SPFI/SPW EGSE | 6.25 Gbps/200 Mbps | Up to 4 | Up to 8 | PXI | LV API or GUI |

| IngeniArs SpaceART | 2.50 Gbps/400 Mbps | 4 | 0 or 2 | Ethernet or PCIe | Windows/Linux API or GUI |

| StarDubdee StarFire MK3 | 3.20 Gbps/400 Mbps | 2 | 2 | USB 3.0 | Windows/Linux GUI |

| EGSE System | HW Data Generator/Consumer | Host Reception and Play | SPW/SPFI Bridging | Error Injection | Trace Memory | External Triggers |

|---|---|---|---|---|---|---|

| Proposed SPFI/SPW EGSE | Yes | Yes | Yes | Yes | Yes | No * |

| IngeniArs SpaceART | Yes | Yes | Yes | Yes | Yes | Yes |

| StarDundee StarFire MK3 | Yes | Yes | Yes | Yes | No | Yes |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Dello Sterpaio, L.; Marino, A.; Nannipieri, P.; Dinelli, G.; Davalle, D.; Fanucci, L. A Complete EGSE Solution for the SpaceWire and SpaceFibre Protocol Based on the PXI Industry Standard. Sensors 2019, 19, 5013. https://doi.org/10.3390/s19225013

Dello Sterpaio L, Marino A, Nannipieri P, Dinelli G, Davalle D, Fanucci L. A Complete EGSE Solution for the SpaceWire and SpaceFibre Protocol Based on the PXI Industry Standard. Sensors. 2019; 19(22):5013. https://doi.org/10.3390/s19225013

Chicago/Turabian StyleDello Sterpaio, Luca, Antonino Marino, Pietro Nannipieri, Gianmarco Dinelli, Daniele Davalle, and Luca Fanucci. 2019. "A Complete EGSE Solution for the SpaceWire and SpaceFibre Protocol Based on the PXI Industry Standard" Sensors 19, no. 22: 5013. https://doi.org/10.3390/s19225013

APA StyleDello Sterpaio, L., Marino, A., Nannipieri, P., Dinelli, G., Davalle, D., & Fanucci, L. (2019). A Complete EGSE Solution for the SpaceWire and SpaceFibre Protocol Based on the PXI Industry Standard. Sensors, 19(22), 5013. https://doi.org/10.3390/s19225013