Analysis of Fault-Tolerant Operation Capabilities of an Isolated Bidirectional Current-Source DC–DC Converter

Abstract

:1. Introduction

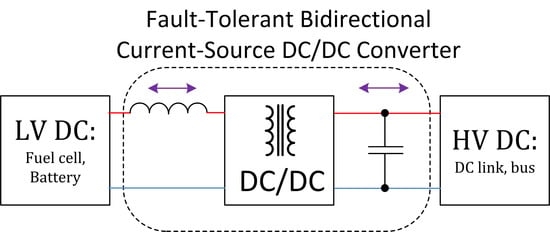

2. Analysis of Case Study Current Source Converter

2.1. Description of Topology

2.2. Analyzed Failure Modes

2.3. Failure Detection Methods

- Desaturation detection;

- Shunt resistor;

- Current scaling (“mirror”);

- Gate charge (voltage);

- Inductive current rate of change (di/dt) sensing;

- Rogowski coil;

- Other/combined.

2.4. Reconfiguration Possibilities and Post-Failure Modes

3. Multi-Mode Operation Strategy

3.1. Converter Design Specifications

- Wider regulation capability;

- Reduced energy circulation;

- Increased transformer utilization;

- Reduced voltage stress on CS semiconductors.

3.2. Determination of Mode Boundary

4. Results

4.1. Post-Failure Operation and Performance

4.2. Multi-Mode Control

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Falck, J.; Felgemacher, C.; Rojko, A.; Liserre, M.; Zacharias, P. Reliability of Power Electronic Systems: An Industry Perspective. IEEE Ind. Electron. Mag. 2018, 12, 24–35. [Google Scholar] [CrossRef]

- Ghimire, P.; Beczkowski, S.; Munk-Nielsen, S.; Rannestad, B.; Thogersen, P.B. A review on real time physical measurement techniques and their attempt to predict wear-out status of IGBT. In Proceedings of the 15th European Conference Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–10. [Google Scholar]

- Falck, J.; Andresen, M.; Liserre, M. Active methods to improve reliability in power electronics. In Proceedings of the 43rd Annual Conference IEEE Industrial Electronics Society, Beijing, China, 29 October–1 November 2017; pp. 7923–7928. [Google Scholar]

- Oh, H.; Han, B.; McCluskey, P.; Han, C.; Youn, B.D. Physics-of-Failure, Condition Monitoring, and Prognostics of Insulated Gate Bipolar Transistor Modules: A Review. IEEE Trans. Power Electron. 2015, 30, 2413–2426. [Google Scholar] [CrossRef]

- Wang, H.; Blaabjerg, F. Reliability of Capacitors for DC-Link Applications in Power Electronic Converters—An Overview. IEEE Trans. Ind. Appl. 2014, 50, 3569–3578. [Google Scholar] [CrossRef]

- Best Practices in Photovoltaic System Operations and Maintenance; Technical Report, NREL/TP-7A40-67553; National Renewable Energy Laboratory (NREL): Lakewood, CO, USA, 2016.

- Zhang, W.; Xu, D.; Enjeti, P.N.; Li, H.; Hawke, J.T.; Krishnamoorthy, H.S. Survey on Fault-Tolerant Techniques for Power Electronic Converters. IEEE Trans. Power Electron. 2014, 29, 6319–6331. [Google Scholar] [CrossRef]

- Jovanović, M.M.; Irving, B.T. On-the-Fly Topology-Morphing Control—Efficiency Optimization Method for LLC Resonant Converters Operating in Wide Input- and/or Output-Voltage Range. IEEE Trans. Power Electron. 2016, 31, 2596–2608. [Google Scholar] [CrossRef]

- Kumar, A.; Lu, J.; Afridi, K.K. Power Density and Efficiency Enhancement in ICN DC–DC Converters Using Topology Morphing Control. IEEE Trans. Power Electron. 2019, 34, 1881–1900. [Google Scholar] [CrossRef]

- Costa, L.; Buticchi, G.; Liserre, M. A Fault-Tolerant Series-Resonant DC–DC Converter. IEEE Trans. Power Electron. 2017, 32, 900–905. [Google Scholar] [CrossRef]

- Blinov, A.; Kosenko, R.; Chub, A.; Vinnikov, D. Bidirectional soft-switching dc–dc converter for battery energy storage systems. IET Power Electron. 2018, 11, 2000–2009. [Google Scholar] [CrossRef]

- Lutz, J.; Schlangenotto, H.; Scheuermann, U.; Doncker, R.D. Semiconductor Power Devices: Physics Characteristics Reliability; Springer: New York, NY, USA, 2011. [Google Scholar]

- Kosenko, R.; Chub, A.; Blinov, A. Full-soft-switching high step-up bidirectional isolated current-fed push-pull DC-DC converter for battery energy storage applications. In Proceedings of the 42nd Annual Conference IEEE Industrial Electronics Society, Florence, Italy, 24–27 October 2016; pp. 6548–6553. [Google Scholar]

- Dchar, I.; Buttay, C.; Morel, H. Avalanche Robustness of SiC Schottky Diode. Microelectronics Reliability. 2016. Available online: https://hal.archives-ouvertes.fr/hal-01373039 (accessed on 20 August 2019).

- Blinov, A.; Norrga, S.; Tibola, G. Operation of single-chip MOSFET and IGBT devices after failure due to repetitive avalanche. In Proceedings of the 17th European Conference on Power Electronics and Applications (EPE’15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015; pp. 1–9. [Google Scholar]

- Lu, J.; Tian, X.; Jin, L.; Lu, S.; Zhou, H.; Zhu, Y.; Han, Z. Dynamic avalanche behavior of power MOSFETs and IGBTs under unclamped inductive switching conditions. J. Semiconductors 2013, 34, 26–30. [Google Scholar] [CrossRef]

- IGBT Ruggedness. ON Semiconductor; Application Note AND9127/D; Semiconductor Components Industries, LLC: Aurora, CO, USA, 2016; Available online: https://www.onsemi.com/pub/Collateral/AND9127-D.pdf (accessed on 20 August 2019).

- Lu, B.; Sharma, S. A Literature Review of IGBT Fault Diagnostic and Protection Methods for Power Inverters. In Proceedings of the IEEE Industry Applications Society Annual Meeting, Edmonton, AB, Canada, 5–9 October 2008; pp. 1–8. [Google Scholar]

- Bertelshofer, T.; Maerz, A.; Bakran, M. Design Rules to Adapt the Desaturation Detection for SiC MOSFET Modules. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM Europe 2017), Nuremberg, Germany, 16–18 May 2017; pp. 1–8. [Google Scholar]

- Sadik, D.; Colmenares, J.; Tolstoy, G.; Peftitsis, D.; Bakowski, M.; Rabkowski, J.; Nee, H.-P. Short-Circuit Protection Circuits for Silicon-Carbide Power Transistors. IEEE Trans. Ind. Electron. 2016, 63, 1995–2004. [Google Scholar] [CrossRef]

- Wang, Z.; Shi, X.; Xue, Y.; Tolbert, L.M.; Blalock, B.J.; Wang, F. Design and performance evaluation of overcurrent protection schemes for silicon carbide (SiC) power MOSFETs. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 15–19 September 2013; pp. 5418–5425. [Google Scholar]

- Spang, M.; Hofstoetter, N. Evaluation of Current Measurement Accuracy for a Power Module with Integrated Shunt Resistors. In Proceedings of the PCIM Europe 2017 International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 10–12 May 2017; pp. 1–8. [Google Scholar]

- Jeong, J.; Lee, J.; Lee, S.; Tsukizawa, M. Effective resistor selection method for over current protection when using sense IGBT solution. In Proceedings of the International ECTI Northern Section Conference on Electrical, Electronics, Computer and Telecommunications Engineering (ECTI-NCON), Chiang Rai, Thailand, 25–28 February 2018; pp. 40–43. [Google Scholar]

- Fink, K.; Volke, A.; Wei, W.; Wiesner, E.; Thal, E. Gate-Driver with Full Protection for SiC-MOSFET Modules. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM Asia 2016), Shanghai, China, 28–30 June 2016; pp. 1–7. [Google Scholar]

- Horiguchi, T.; Kinouchi, S.; Nakayama, Y.; Oi, T.; Urushibata, H.; Okamo, S.; Tominaga, S.; Akagi, H. A high-speed protection circuit for IGBTs subjected to hard-switching faults. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition—APEC 2014, Fort Worth, TX, USA, 16–20 March 2014; pp. 2519–2525. [Google Scholar]

- Climaco-Arvizu, O.; Hernández-González, L.; Rodríguez-Blanco, M.A. Fault detection for SiC-Mosfet based on the behavior of gate signal. In Proceedings of the IEEE 10th International Symposium on Diagnostics for Electrical Machines, Power Electronics and Drives (SDEMPED), Guarda, Portugal, 1–4 September 2015; pp. 71–76. [Google Scholar]

- Huang, F.; Flett, F. IGBT Fault Protection Based on di/dt Feedback Control. In Proceedings of the IEEE Power Electronics Specialists Conference, Orlando, FL, USA, 17–21 June 2007; pp. 1478–1484. [Google Scholar]

- Oinonen, M.; Laitinen, M.; Kyyrä, J. Current measurement and short-circuit protection of an IGBT based on module parasitics. In Proceedings of the 16th European Conference on Power Electronics and Applications, Lappeenranta, Finland, 26–28 August 2014; pp. 1–9. [Google Scholar]

- Wang, J.; Shen, Z.; Burgos, R.; Boroyevich, D. Design of a high-bandwidth Rogowski current sensor for gate-drive shortcircuit protection of 1.7 kV SiC MOSFET power modules. In Proceedings of the IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; pp. 104–107. [Google Scholar]

- Velander, E.; Kruse, L.; Meier, S.; Löfgren, A.; Wiik, T.; Nee, H.-P.; Sadik, D.-P. Analysis of short circuit type II and III of high voltage SiC MOSFETs with fast current source gate drive principle. In Proceedings of the IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016; pp. 3392–3397. [Google Scholar]

- Hain, S.; Bakran, M. New Ultra Fast Short Circuit Detection Method Without Using the Desaturation Process of the Power Semiconductor. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM Europe 2016), Nuremberg, Germany, 10–12 May 2016; pp. 1–8. [Google Scholar]

- Kosenko, R.; Blinov, A.; Chub, A.; Vinnikov, D. Asymmetric Snubberless Current-Fed Full-Bridge Isolated DC-DC Converters. Electr. Control Commun. Eng. 2018, 14, 5–11. [Google Scholar] [CrossRef]

- Blinov, A.; Kosenko, R.; Chub, A.; Vinnikov, D. Bidirectional Soft Switching Current Source DC-DC Converter for Residential DC Microgrids. In Proceedings of the IECON 2018—44th Annual Conference of the IEEE Industrial Electronics Society, Washington, DC, USA, 21–23 October 2018; pp. 6059–6064. [Google Scholar]

- Kosenko, R.; Vinnikov, D. Soft-Switching Current-FED Flyback Converter with Natural Clamping for Low Voltage Battery Energy Storage Applications. In Technological Innovation for Smart Systems, Proceedings of the Doctoral Conference on Computing, Electrical and Industrial Systems, Lisbon, Portugal, 3–5 May 2017; Springer International Publishing: Basel, Switzerland, 2017. [Google Scholar]

- Xuewei, P.; Rathore, A.K. Novel Interleaved Bidirectional Snubberless Soft-Switching Current-Fed Full-Bridge Voltage Doubler for Fuel-Cell Vehicles. IEEE Trans. Power Electron. 2013, 28, 5535–5546. [Google Scholar] [CrossRef]

- Chen, R.Y.; Liang, T.J.; Chen, J.F.; Lin, R.L.; Tseng, K.C. Study and Implementation of a Current-Fed Full-Bridge Boost DC-DC Converter with Zero-Current Switching for High-Voltage Applications. IEEE Trans. Ind. Appl. 2008, 44, 1218–1226. [Google Scholar] [CrossRef]

- Iannello, C.; Luo, S.; Batarseh, I. Full bridge ZCS PWM converter for high-voltage high-power applications. IEEE Trans. Aerosp. Electron. Syst. 2002, 38, 515–526. [Google Scholar] [CrossRef]

- Blinov, A.; Kosenko, R.; Chub, A.; Vinnikov, D. Snubberless boost full-bridge converters: Analysis of soft switching performance and limitations. Int. J. Circuit Theor. Appl. 2019, 47, 884–908. [Google Scholar] [CrossRef]

- Mößlacher, C.; Guillemant, O. Improving Efficiency of Synchronous Rectification by Analysis of the MOSFET Power Loss Mechanism; Application Note AN 2012-03; Infineon Technologies Austria AG: Villach, Austria, 2012; Available online: https://www.infineon.com/dgdl/Infineon-MOSFET_OptiMOS_improving_efficiency_of_synchronous_rectification_by_analysis_of_the_MOSFET_power_loss_mechanism-AN-v03_00-EN.pdf?fileId=db3a304320d39d590121a671f2d90c38 (accessed on 20 August 2019).

| Transistor | PS-SMC | A-SMC | FBK-SMC | S-SMC | |||

|---|---|---|---|---|---|---|---|

| S1.1 | + | + | 1 | + | 0/- | + | + |

| S1.2 | + | 1 | 1 | + | 0/- | + | 1 |

| S2.1 | + | + | + | 1 | + | 0/- | + |

| S2.2 | + | + | + | 1 | + | 0/- | 1 |

| S3.1 | + | + | 0/- | + | 1 | + | + |

| S3.2 | + | 1 | 0/- | + | 1 | + | 1 |

| S4.1 | + | + | + | 0/- | + | 1 | + |

| S4.2 | + | + | + | 0/- | + | 1 | 1 |

| S5 | + | + | + | + | + | + | + |

| S6 | + | + | + | + | + | + | + |

| S7 | - | - | + | + | + | + | - |

| S8 | - | - | + | + | + | + | - |

| S9 | - | - | +/1 | +/1 | +/1 | +/1 | - |

| Parameter/Component | Symbol | Value |

|---|---|---|

| CS voltage | UCS | 16–32 VDC |

| VS voltage | UVS | 380–420 VDC |

| Power | Prated | 300 W |

| Operating frequency | fsw | 50 kHz |

| Transformer turns ratio | n | 5.5 |

| CS side Inductor | L1 | 100 μH |

| Equivalent switch capacitance | Cs | 500 pF |

| Equivalent inductance | Leq | 400 nH |

| CS MOSFETs | S1.x–S4.x | BSC035N10NS5 |

| VS MOSFETs | S5–S6 | IXFP22N65X2 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Blinov, A.; Kosenko, R.; Chub, A.; Ivakhno, V. Analysis of Fault-Tolerant Operation Capabilities of an Isolated Bidirectional Current-Source DC–DC Converter. Energies 2019, 12, 3203. https://doi.org/10.3390/en12163203

Blinov A, Kosenko R, Chub A, Ivakhno V. Analysis of Fault-Tolerant Operation Capabilities of an Isolated Bidirectional Current-Source DC–DC Converter. Energies. 2019; 12(16):3203. https://doi.org/10.3390/en12163203

Chicago/Turabian StyleBlinov, Andrei, Roman Kosenko, Andrii Chub, and Volodymyr Ivakhno. 2019. "Analysis of Fault-Tolerant Operation Capabilities of an Isolated Bidirectional Current-Source DC–DC Converter" Energies 12, no. 16: 3203. https://doi.org/10.3390/en12163203

APA StyleBlinov, A., Kosenko, R., Chub, A., & Ivakhno, V. (2019). Analysis of Fault-Tolerant Operation Capabilities of an Isolated Bidirectional Current-Source DC–DC Converter. Energies, 12(16), 3203. https://doi.org/10.3390/en12163203