An Overview about Si, Superjunction, SiC and GaN Power MOSFET Technologies in Power Electronics Applications

Abstract

:1. Introduction

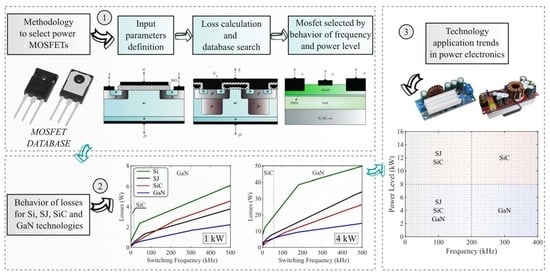

- A comparative analysis among four power MOSFET technologies: conventional Silicon (Si), Superjunction (SJ), Silicon Carbide (SiC) and Gallium Nitride (GaN) using a database with 91 part numbers from different manufacturers (Appendix A);

- A correlation of losses to physical characteristics of each technology, considering internal capacitances, internal gate resistances and drain-source on-state resistance as a function of junction temperature;

- A methodology for selecting power MOSFETs in power electronics applications;

- A definition of power and frequency ranges of the best performance for each technology, considering a drain-source voltage of 400 V, power levels from 1 kW to 16 kW (1 A–40 A) and frequency ranges from 1 kHz to 500 kHz.

2. Losses in Power MOSFETs

3. Analytical Model Experimental Validation

4. Impact of Internal Parameters on MOSFET Losses

4.1. Conduction Loss Evaluation

- Step 1: The initial RMS current of 1 and of 25 C and 125 C are defined.

- Step 2: The algorithm searches the database, selecting transistors that meet the current capacity criteria for the specified current.

- Step 3: The losses are calculated by Equation (1).

- Step 4: In each current iteration, the part number that presents the lowest losses for each technology is selected. This procedure is executed in steps of 1 A until the RMS current reaches 100 A. Thus, it is possible to select different part numbers for the same technology along the current range.

- Step 5: As the output, the behavior of the conduction losses with current variation is obtained.

4.2. Switching Loss Evaluation

- Step 1: Input parameters are set as = = = 2.5 A, = 400 V and starting frequency = 1 kHz.

- Step 2: The algorithm searches the database, selecting transistors that meet the current and voltage criteria.

- Step 3: The losses are calculated by Equation (2).

- Step 4: Only the transistor of each technology that presents lowest losses (for a set of parameters) is selected. Step 4 is performed in steps of 1 kHz until the switching frequency reaches 500 kHz, for current levels of 2.5 A until 80 A. The current loop is doubled in each iteration. It is possible to select different part numbers for the same technology along the frequency and current ranges.

- Step 5: As the output, the behavior of losses with variations in the switching frequency and current levels in scenario 1 (without including ) and scenario 2 (using ) are obtained.

4.2.1. Scenario 1: Influence of Internal Capacitances

4.2.2. Scenario 2: Influence of

4.3. Total Losses Evaluation

- Step 1: The input parameters are set as kHz, C and power level of 1 kW, which corresponds to an average current of 2.5 A.

- Step 2: The algorithm searches the database, selecting transistors that meet the current and voltage criteria.

- Step 3: The total losses are calculated by Equation (10).

- Step 4: Only the transistor of each technology that presents lowest losses (for a set of current and voltage) is selected. This procedure is performed in steps of 1 kHz for all power levels under analysis, until the switching frequency reaches 500 kHz, for power levels of 1 kW until 16 kW. The power loop is doubled in each iteration. It is possible to select different part numbers in each iteration.

- Step 5: As the output, the behavior of total losses as a function of the switching frequency and current/power levels are obtained.

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Appendix A

References

- Busquets-Monge, S.; Crebier, J.C.; Ragon, S.; Hertz, E.; Boroyevich, D.; Gurdal, Z.; Arpilliere, M.; Lindner, D.K. Design of a boost power factor correction converter using optimization techniques. IEEE Trans. Power Electron. 2004, 19, 1388–1396. [Google Scholar] [CrossRef]

- Biela, J.; Kolar, J.W.; Deboy, G. Optimal design of a compact 99.3% efficient single-phase PFC rectifier. In Proceedings of the 2010 Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 21–25 February 2010; pp. 1397–1404. [Google Scholar]

- Sartori, H.C.; Hey, H.L.; Pinheiro, J.R. An optimum design of PFC Boost Converters. In Proceedings of the 2009 13th European Conference on Power Electronics and Applications, Barcelona, Spain, 8–10 September 2009; pp. 1–10. [Google Scholar]

- Chen, B.; Gu, B.; Zhang, L.; Zahid, Z.U.; Lai, J.S.; Liao, Z.; Hao, R. A high-efficiency MOSFET transformerless inverter for nonisolated microinverter applications. IEEE Trans. Power Electron. 2014, 30, 3610–3622. [Google Scholar] [CrossRef]

- Sartori, H.C.; Baggio, J.E.; Hey, H.L.; Pinheiro, J.R.; Beltrame, F. Integrated methodology design to improve the efficiency and reduce volume of the CCM PFC boost converters with pre-sizing settings. In Proceedings of the 2015 IEEE 24th International Symposium on Industrial Electronics (ISIE), Buzios, Brazil, 3–5 June 2015; pp. 1378–1385. [Google Scholar]

- Bolsi, P.C.; Sartori, H.C.; Pinheiro, J.R. Comparison of Core Technologies Applied to Power Inductors. In Proceedings of the 2018 13th IEEE International Conference on Industry Applications (INDUSCON), Sao Paulo, Brazil, 12–14 November 2018; pp. 1100–1106. [Google Scholar]

- Bolsi, P.C.; Prado, E.O.; Sartori, H.C.; Lenz, J.M.; Pinheiro, J.R. LCL Filter Parameter and Hardware Design Methodology for Minimum Volume Considering Capacitor Lifetimes. Energies 2022, 15, 4420. [Google Scholar] [CrossRef]

- Kalantar, M. Posicast control within feedback structure for a DC–DC single ended primary inductor converter in renewable energy applications. Appl. Energy 2010, 87, 3110–3114. [Google Scholar] [CrossRef]

- Saravanan, S.; Babu, N.R. Analysis and implementation of high step-up DC-DC converter for PV based grid application. Appl. Energy 2017, 190, 64–72. [Google Scholar] [CrossRef]

- Ding, X.; Du, M.; Zhou, T.; Guo, H.; Zhang, C. Comprehensive comparison between silicon carbide MOSFETs and silicon IGBTs based traction systems for electric vehicles. Appl. Energy 2017, 194, 626–634. [Google Scholar] [CrossRef]

- Ding, X.; Lu, P.; Shan, Z. A high-accuracy switching loss model of SiC MOSFETs in a motor drive for electric vehicles. Appl. Energy 2021, 291, 116827. [Google Scholar] [CrossRef]

- Han, F.; Guo, H.; Ding, X. Design and optimization of a liquid cooled heat sink for a motor inverter in electric vehicles. Appl. Energy 2021, 291, 116819. [Google Scholar] [CrossRef]

- Biela, J.; Badstuebner, U.; Kolar, J.W. Impact of power density maximization on efficiency of DC–DC converter systems. IEEE Trans. Power Electron. 2009, 24, 288–300. [Google Scholar] [CrossRef]

- Sartori, H.; Beltrame, F.; Pinheiro, J. A static converter comparative study taking into account semiconductor tecnologies and swicth auxiliary circuits: Optimized design. In Proceedings of the XI Brazilian Power Electronics Conference, Natal, Brazil, 11–15 September 2011; pp. 280–285. [Google Scholar]

- Tiburski, M.j.; Bridi, É.; Sartori, H.C.; Pinheiro, J.R. Analysis and Design of a High Step-Up Boost Converter Applied to Fuel Cell. In Proceedings of the 2018 13th IEEE International Conference on Industry Applications (INDUSCON), Sao Paulo, Brazil, 12–14 November 2018; pp. 817–824. [Google Scholar]

- Prado, E.O.; Bolsi, P.C.; Sartori, H.C.; Pinheiro, J.R. Simple analytical model for accurate switching loss calculation in power MOSFETs using non-linearities of Miller capacitance. IET Power Electron. 2022, 15, 594–604. [Google Scholar] [CrossRef]

- Sartori, H.C.; Beltrame, F.; Martins, M.L.; Baggio, J.E.; Pinheiro, J.R. Evaluation of an optimal design for a single-phase boost PFC converter (CCM) considering different magnetic materials core. In Proceedings of the 2013 Brazilian Power Electronics Conference, Gramado, Brazil, 27–31 October 2013; pp. 1304–1310. [Google Scholar]

- Rashid, M.H. Power Electronics Handbook; Butterworth-Heinemann: Oxford, UK, 2017. [Google Scholar]

- Stuckler, F.; Abdel-Rahman, S.; Siu, K. 600 V CoolMOS C7 Design Guide; Infineon Technologies: Neubiberg, Germany, 2015. [Google Scholar]

- Chen, K.J.; Häberlen, O.; Lidow, A.; lin Tsai, C.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si power technology: Devices and applications. IEEE Trans. Electron Devices 2017, 64, 779–795. [Google Scholar] [CrossRef]

- Hilt, O.; Treidel, E.B.; Wolf, M.; Kuring, C.; Tetzner, K.; Yazdani, H.; Wentzel, A.; Würfl, J. Lateral and vertical power transistors in GaN and Ga2 O3. IET Power Electron. 2019, 12, 3919–3927. [Google Scholar] [CrossRef]

- Oonishi, Y.; Ooi, A.; Shimatou, T. Superjunction MOSFET. Fuji Electron. Rev. 2010, 56, 65–68. [Google Scholar]

- Steiner, A. 600 V CoolMOS P7. Infineon Technol. AG, Munich, Germany, Infineon Appl. Note AN_201703_PL52_015. 2019. Available online: https://www.infineon.com/600v-p7 (accessed on 10 April 2022).

- Udrea, F.; Deboy, G.; Fujihira, T. Superjunction power devices, history, development, and future prospects. IEEE Trans. Electron Devices 2017, 64, 713–727. [Google Scholar] [CrossRef]

- Wang, G.; Wang, F.; Magai, G.; Lei, Y.; Huang, A.; Das, M. Performance comparison of 1200V 100A SiC MOSFET and 1200 V 100A silicon IGBT. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 15–19 September 2013; pp. 3230–3234. [Google Scholar]

- Millan, J.; Godignon, P.; Perpiñà, X.; Pérez-Tomás, A.; Rebollo, J. A survey of wide bandgap power semiconductor devices. IEEE Trans. Power Electron. 2013, 29, 2155–2163. [Google Scholar] [CrossRef]

- Mantooth, H.A.; Peng, K.; Santi, E.; Hudgins, J.L. Modeling of wide bandgap power semiconductor devices Part I. IEEE Trans. Electron. Devices 2014, 62, 423–433. [Google Scholar] [CrossRef]

- She, X.; Huang, A.Q.; Lucia, O.; Ozpineci, B. Review of silicon carbide power devices and their applications. IEEE Trans. Ind. Electron. 2017, 64, 8193–8205. [Google Scholar] [CrossRef]

- Wang, F.F.; Zhang, Z. Overview of silicon carbide technology: Device, converter, system, and application. CPSS Trans. Power Electron. Appl. 2016, 1, 13–32. [Google Scholar] [CrossRef]

- Jones, E.A.; Wang, F.F.; Costinett, D. Review of commercial GaN power devices and GaN-based converter design challenges. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 707–719. [Google Scholar] [CrossRef]

- Baliga, B.J. Gallium nitride devices for power electronic applications. Semicond. Sci. Technol. 2013, 28, 074011. [Google Scholar] [CrossRef]

- Huang, X.; Liu, Z.; Li, Q.; Lee, F.C. Evaluation and application of 600 V GaN HEMT in cascode structure. IEEE Trans. Power Electron. 2013, 29, 2453–2461. [Google Scholar] [CrossRef]

- Huang, X.; Du, W.; Lee, F.C.; Li, Q.; Liu, Z. Avoiding Si MOSFET avalanche and achieving zero-voltage switching for cascode GaN devices. IEEE Trans. Power Electron. 2015, 31, 593–600. [Google Scholar] [CrossRef]

- Talikoti, N.; Rao, K.U.; Ghosh, R. GaN versus CoolMOS: A theoretical comparison of performances. In Proceedings of the Fifth International Conference on Advances in Recent Technologies in Communication and Computing (ARTCom 2013), Bangalore, India, 20–21 September 2013. [Google Scholar]

- Mitova, R.; Ghosh, R.; Mhaskar, U.; Klikic, D.; Wang, M.X.; Dentella, A. Investigations of 600-V GaN HEMT and GaN diode for power converter applications. IEEE Trans. Power Electron. 2013, 29, 2441–2452. [Google Scholar] [CrossRef]

- Avila, A.; Garcia-Bediaga, A.; Oñederra, O.; Ruias, A.; Rodriguez, A. Comparative analysis of GaN HEMT vs. Si CoolMOS for a high-frequency MMC topology. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. P.1–P.9. [Google Scholar]

- Ding, X.; Chen, F.; Du, M.; Guo, H.; Ren, S. Effects of silicon carbide MOSFETs on the efficiency and power quality of a microgrid-connected inverter. Appl. Energy 2017, 201, 270–283. [Google Scholar] [CrossRef]

- Prado, E.O.; Sartori, H.C.; Pinheiro, J.R. How to select power transistors for static converters applications? In Proceedings of the 2018 13th IEEE International Conference on Industry Applications (INDUSCON), Sao Paulo, Brazil, 12–14 November 2018; pp. 138–143. [Google Scholar]

- Buetow, S.; Herzer, R. Characterization of GaN-HEMT in cascode topology and comparison with state of the art-power devices. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 196–199. [Google Scholar]

- Alharbi, S.S.; Alharbi, S.S.; Matin, M. Effects of gallium nitride (GaN) cascode FETs on the efficiency of an interleaved DC-DC converter. In Proceedings of the 2018 IEEE International Conference on Electro/Information Technology (EIT), Rochester, MI, USA, 3–5 May 2018; pp. 384–389. [Google Scholar]

- Cha, K.H.; Ju, C.T.; Kim, R.Y. Analysis and evaluation of WBG power device in high frequency induction heating application. Energies 2020, 13, 5351. [Google Scholar] [CrossRef]

- Pellitteri, F.; Busacca, A.; Martorana, C.; Miceli, R.; Stivala, S.; Messina, A.A.; Calabretta, M.; Vinciguerra, V. Power losses comparison between Silicon Carbide and Silicon devices for an isolated DC-DC converter. In Proceedings of the 2021 IEEE 15th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), Florence, Italy, 14–16 July 2021; pp. 1–6. [Google Scholar]

- Shelton, E.; Ali, K.; Han, R.; Rogers, D.; Carter, J.; Louco, L.; Beadman, M.; Palmer, P. Comparison of Fast Switching High Current Power Devices. In Proceedings of the PCIM Europe Digital Days 2021; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Online, 3–7 May 2021; pp. 1–8. [Google Scholar]

- Siemieniec, R.; Mente, R.; Jantscher, W.; Kammerlander, D.; Wenzel, U. 600 V power device technologies for highly efficient power supplies. In Proceedings of the 2021 23rd European Conference on Power Electronics and Applications (EPE’21 ECCE Europe), Ghent, Belgium, 6–10 September 2021; pp. P.1–P.10. [Google Scholar]

- Marroqui, D.; Garrigós, A.; Torres, C.; Orts, C.; Blanes, J.M.; Gutierrez, R. Interleaved, Switched Inductor and High-Gain Wide Bandgap Based Boost Converter Proposal. Energies 2021, 14, 800. [Google Scholar] [CrossRef]

- Xiao, Y.; Shah, H.; Chow, T.; Gutmann, R. Analytical modeling and experimental evaluation of interconnect parasitic inductance on MOSFET switching characteristics. In Proceedings of the Nineteenth Annual IEEE Applied Power Electronics Conference and Exposition, Anaheim, CA, USA, 22–26 February 2004; Volume 1, pp. 516–521. [Google Scholar]

- Ren, Y.; Xu, M.; Zhou, J.; Lee, F.C. Analytical loss model of power MOSFET. IEEE Trans. Power Electron. 2006, 21, 310–319. [Google Scholar]

- de Paula, W.J.; Tavares, G.H.M.; Soares, G.M.; Almeida, P.S.; Braga, H.A.C. Switching losses prediction methods oriented to power MOSFETs–a review. IET Power Electron. 2020, 13, 2960–2970. [Google Scholar] [CrossRef]

- Piovesan, T.; Sartori, H.C.; Bender, V.C.; Pinheiro, J.R. Método para quantificação de perdas em semicondutores aplicados a conversores estáticos devido aos elementos parasitas da placa de circuito impresso. Eletrônica Potência 2021, 26, 42–52. [Google Scholar] [CrossRef]

- Prado, E.O.; Bolsi, P.C.; Sartori, H.C.; Pinhero, J.R. Modelo analítico de cálculo de perdas em MOSFETs de potência para aplicação em banco de dados. Eletrônica Potência 2021, 26, 388–398. [Google Scholar]

- Graovac, D.; Purschel, M.; Kiep, A. MOSFET Power Losses Calculation Using the Data-Sheet Parameters; Infineon Application Note; Infineon Technologies: Neubiberg, Germany, 2006. [Google Scholar]

- Brown, J. Modeling the switching performance of a MOSFET in the high side of a non-isolated buck converter. IEEE Trans. Power Electron. 2006, 21, 3–10. [Google Scholar] [CrossRef]

- Sartori, H.C.; Beltrame, F.; Figueira, H.H.; Baggio, J.E.; Pinheiro, J.R. Power density comparative analysis concerning to three transistor technologies applied to a CCM PFC BOOST converter using optimization techniques. In Proceedings of the 2013 Brazilian Power Electronics Conference, Gramado, Brazil, 27–31 October 2013; pp. 1317–1323. [Google Scholar]

- Beltrame, F.; Dupont, F.H.; Sartori, H.C.; Cancian, E.C.; Rech, C.; Pinheiro, J.R. Efficiency optimization of DC/DC boost converter applied to the photovoltaic system. In Proceedings of the IECON 2013-39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013; pp. 706–711. [Google Scholar]

- Guo, J.; Ge, H.; Ye, J.; Emadi, A. Improved method for MOSFET voltage rise-time and fall-time estimation in inverter switching loss calculation. In Proceedings of the 2015 IEEE Transportation Electrification Conference and Expo (ITEC), Vienna, Austria, 10–13 November 2015; pp. 1–6. [Google Scholar]

- Lakkas, G. MOSFET power losses and how they affect power-supply efficiency. Analog. Appl. 2016, 10, 22–26. [Google Scholar]

- Zhai, L.; Yang, S.; Hu, G.; Lv, M. Design method of wide-band high-current air-core inductor EMI filter for high voltage DC power of motor inverter of electric vehicle. IET Power Electron. 2022, 1–16. [Google Scholar] [CrossRef]

- Mahdizadeh, S.; Gholizadeh, H.; Shahrivar, R.S.; Afjei, E.; Mosallanejad, A. An ultra high step-up DC-DC converter based on VMC, POSLLC, and boost converter. IET Power Electron. 2015, 15, 901–918. [Google Scholar] [CrossRef]

- Roggia, L.; Schuch, L.; Baggio, J.E.; Rech, C.; Pinheiro, J.R. Integrated full-bridge-forward DC–DC converter for a residential microgrid application. IEEE Trans. Power Electron. 2012, 28, 1728–1740. [Google Scholar] [CrossRef]

- Rathore, A.K.; Patil, D.R.; Srinivasan, D. Non-isolated bidirectional soft-switching current-fed LCL resonant DC/DC converter to interface energy storage in DC microgrid. IEEE Trans. Ind. Appl. 2015, 52, 1711–1722. [Google Scholar] [CrossRef]

- Forouzesh, M.; Siwakoti, Y.P.; Gorji, S.A.; Blaabjerg, F.; Lehman, B. Step-up DC–DC converters: A comprehensive review of voltage-boosting techniques, topologies, and applications. IEEE Trans. Power Electron. 2017, 32, 9143–9178. [Google Scholar] [CrossRef]

- Melito, M.; Gaito, A.; Sorrentino, G. Thermal effects and junction temperature evaluation of Power MOSFETs. DocID028570 Rev. 2015, 1, 141. [Google Scholar]

- Fluke Corporation. Ti20 Thermal Imager; Fluke Corporation: Everett, WA, USA, 2006. [Google Scholar]

- Chen, H.; Ji, B.; Pickert, V.; Cao, W. Real-time temperature estimation for power MOSFETs considering thermal aging effects. IEEE Trans. Device Mater. Reliab. 2013, 14, 220–228. [Google Scholar] [CrossRef] [Green Version]

- On Semiconductor. Heat Sink Selection Guide for Thermally Enhaced SO8-FL; On Semiconductor: Phoenix, AZ, USA, 2015. [Google Scholar]

| MTW20N50E | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| 40% | 50% | 60% | |||||||

| Meas. | Calc. | Error | Meas. | Calc. | Error | Meas. | Calc. | Error | |

| 50 kHz | 0.56 | 0.58 | 3.45% | 0.86 | 0.92 | 6.52% | 1.41 | 1.40 | 0.71% |

| 150 kHz | 1.43 | 1.41 | 1.42% | 2.29 | 2.16 | 6.02% | 3.70 | 3.47 | 6.63% |

| IPW60R040C7 | |||||||||

| 50 kHz | 0.50 | 0.51 | 1.96% | 0.80 | 0.84 | 4.76% | 1.17 | 1.24 | 5.65% |

| 150 kHz | 1.75 | 1.66 | 5.42% | 2.46 | 2.33 | 5.58% | 3.59 | 3.48 | 3.16% |

| IMW65R072M1H | |||||||||

| 50 kHz | 0.35 | 0.33 | 6.06% | 0.39 | 0.38 | 2.63% | 0.54 | 0.58 | 6.90% |

| 150 kHz | 0.62 | 0.59 | 5.08% | 0.82 | 0.83 | 1.20% | 1.22 | 1.29 | 5.43% |

| I (A) | SJ | SiC | GaN | Si |

|---|---|---|---|---|

| 2.5 | IPU95R2K0P7 | IMW120R350M1H | TP65H150G4PS | IXFP20N50P3M |

| 5 | IPA95R1K2P7 | C3M0280090J | TP65H150G4PS | IXFP20N50P3M |

| 10 | IPA95R450P7 | IMW120R220M1H | TP65H150G4PS | IXFH16N50P3 |

| 20 | IPZ65R095C7 | C3M0120100K | TP65H070L | IXFR64N50P |

| 40 | IPP60R040C7 | SCT4026DE | TP65H035WSQA | IXFR80N50Q3 |

| 80 | IPZ60R017C7 | SCT4013DR | – | – |

| I (A) | Part Number | (pF) | (pF) | () |

|---|---|---|---|---|

| 2.5 | IPU95R2K0P7 | 330 | 1.6 | 2 |

| 5 | IPA95R1K2P7 | 478 | 2.1 | 1.2 |

| 10 | IPA95R450P7 | 1053 | 5 | 0.45 |

| 20 | IPZ65R095C7 | 2140 | 8 | 0.095 |

| 40 | IPP60R040C7 | 4340 | 19 | 0.04 |

| 80 | IPZ60R017C7 | 9890 | 40 | 0.017 |

| I (A) | Part Number | (pF) | (pF) | () |

|---|---|---|---|---|

| 2.5 | IMW120R350M1H | 182 | 1 | 0.35 |

| 5 | C3M0280090J | 150 | 2 | 0.28 |

| 10 | IMW120R220M1H | 289 | 2 | 0.22 |

| 20 | C3M0120100K | 350 | 3 | 0.12 |

| 40 | SCT4026DE | 2320 | 9 | 0.026 |

| 80 | SCT4013DR | 4580 | 10 | 0.013 |

| I (A) | Part Number | (pF) | (pF) | () |

|---|---|---|---|---|

| 2.5 | TP65H150G4PS | 307 | 1 | 0.15 |

| 5 | TP65H150G4PS | 307 | 1 | 0.15 |

| 10 | TP65H150G4PS | 307 | 1 | 0.15 |

| 20 | TP65H070L | 600 | 4 | 0.072 |

| 40 | TP65H035WSQA | 1500 | 14 | 0.035 |

| 80 | – | – | – | – |

| I (A) | Part Number | (pF) | (pF) | () |

|---|---|---|---|---|

| 2.5 | IXFP20N50P3M | 1800 | 7 | 0.3 |

| 5 | IXFP20N50P3M | 1800 | 7 | 0.3 |

| 10 | IXFH16N50P3 | 1515 | 7 | 0.3 |

| 20 | IXFR64N50P | 9700 | 30 | 0.095 |

| 40 | IXFR80N50Q3 | 10,000 | 115 | 0.05 |

| 80 | – | – | – | – |

| I (A) | Part Number | Technology | () |

|---|---|---|---|

| 5 | IPA95R1K2P7 | SJ | 1 |

| 20 | IPZ65R095C7 | SJ | 0.9 |

| 80 | IPZ60R017C7 | SJ | 0.45 |

| 5 | C3M0280090J | SiC | 26 |

| 20 | C3M0120100K | SiC | 9 |

| 80 | SCT4013DR | SiC | 1 |

| 5 | TP65H150G4PS | GaN | – |

| 20 | TP65HO70L | GaN | – |

| 80 | – | – | – |

| 5 | IXFP20N50P3M | Si | 2.3 |

| 20 | IXFR64N50P | Si | – |

| 80 | – | – | – |

| P (kW) | SiC | GaN | SJ | Si |

|---|---|---|---|---|

| 1 | Up to 14 kHz | 14–500 kHz | – | – |

| 2 | Up to 28 kHz | 28–500 kHz | – | – |

| 4 | Up to 55 kHz | 55–500 kHz | – | – |

| 8 | Up to 110 kHz | 110–500 kHz | – | – |

| 16 | 1–500 kHz | – | – | – |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Prado, E.O.; Bolsi, P.C.; Sartori, H.C.; Pinheiro, J.R. An Overview about Si, Superjunction, SiC and GaN Power MOSFET Technologies in Power Electronics Applications. Energies 2022, 15, 5244. https://doi.org/10.3390/en15145244

Prado EO, Bolsi PC, Sartori HC, Pinheiro JR. An Overview about Si, Superjunction, SiC and GaN Power MOSFET Technologies in Power Electronics Applications. Energies. 2022; 15(14):5244. https://doi.org/10.3390/en15145244

Chicago/Turabian StylePrado, Edemar O., Pedro C. Bolsi, Hamiltom C. Sartori, and José R. Pinheiro. 2022. "An Overview about Si, Superjunction, SiC and GaN Power MOSFET Technologies in Power Electronics Applications" Energies 15, no. 14: 5244. https://doi.org/10.3390/en15145244

APA StylePrado, E. O., Bolsi, P. C., Sartori, H. C., & Pinheiro, J. R. (2022). An Overview about Si, Superjunction, SiC and GaN Power MOSFET Technologies in Power Electronics Applications. Energies, 15(14), 5244. https://doi.org/10.3390/en15145244