Quantum Confinement Effect in Amorphous In–Ga–Zn–O Heterojunction Channels for Thin-Film Transistors

Abstract

:1. Introduction

2. Experimental Methods

3. Results and Discussion

3.1. Crystallinity of IGZO films

3.2. Band Alignment and Steepness at Heterojunction Interface

3.3. TFT Characteristics

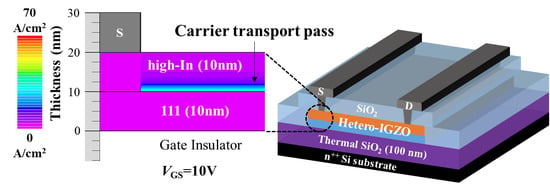

3.4. Device Simulation

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Conflicts of Interest

References

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef] [PubMed]

- Hirao, T.; Furuta, M.; Furuta, H.; Matsuda, T.; Hiramatsu, T.; Hokari, H.; Yoshida, M. 4.1: Distinguished Paper: High Mobility Top-Gate Zinc Oxide Thin-Film Transistors (ZnO-TFTs) for Active-Matrix Liquid Crystal Displays. SID Symp. Dig. Tech. Pap. 2006, 37, 18. [Google Scholar] [CrossRef]

- Jiang, J.; Toda, T.; Hung, M.P.; Wang, D.; Furuta, M. Highly stable fluorine-passivated In–Ga–Zn–O thin-film transistors under positive gate bias and temperature stress. Appl. Phys. Express 2014, 7, 114103. [Google Scholar] [CrossRef]

- Cho, S.H.; Ryu, M.K.; Kim, H.-O.; Kwon, O.S.; Park, E.-S.; Roh, Y.-S.; Hwang, C.-S.; Park, S.-H.K. Influence of gate dielectric/channel interface engineering on the stability of amorphous indium gallium zinc oxide thin-film transistors. Phys. Status solidi A 2014, 211, 2126–2133. [Google Scholar] [CrossRef]

- Wang, D.; Hung, M.P.; Jiang, J.; Toda, T.; Furuta, M. Suppression of Degradation Induced by Negative Gate Bias and Illumination Stress in Amorphous InGaZnO Thin-Film Transistors by Applying Negative Drain Bias. ACS Appl. Mater. Interfaces 2014, 6, 5713–5718. [Google Scholar] [CrossRef]

- Koretomo, D.; Toda, T.; Matsuda, T.; Kimura, M.; Furuta, M. Anomalous Increase in Field-Effect Mobility in In–Ga–Zn–O Thin-Film Transistors Caused by Dry-Etching Damage Through Etch-Stop Layer. IEEE Trans. Electron Devices 2016, 63, 2785–2789. [Google Scholar] [CrossRef]

- Magari, Y.; Makino, H.; Furuta, M. Carrier Generation Mechanism and Origin of Subgap States in Ar- and He-Plasma-Treated In–Ga–Zn–O Thin Films. ECS J. Solid State Sci. Technol. 2017, 6, Q101–Q107. [Google Scholar] [CrossRef]

- Aman, S.G.M.; Magari, Y.; Shimpo, K.; Hirota, Y.; Makino, H.; Koretomo, D.; Furuta, M. Low-temperature (150 °C) activation of Ar + O2 + H2-sputtered In–Ga–Zn–O for thin-film transistors. Appl. Phys. Express 2018, 11, 081101. [Google Scholar] [CrossRef]

- Kamiya, T.; Hosono, H. Material characteristics and applications of transparent amorphous oxide semiconductors. NPG Asia Mater. 2010, 2, 15–22. [Google Scholar] [CrossRef] [Green Version]

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances. Adv. Mater. 2012, 24, 2945–2986. [Google Scholar] [CrossRef]

- Raja, J.; Jang, K.; Nguyen, C.P.T.; Yi, J.; Balaji, N.; Hussain, S.Q.; Chatterjee, S. Improvement of Mobility in Oxide-Based Thin Film Transistors: A Brief Review. Trans. Electr. Electron. Mater. 2015, 16, 234–240. [Google Scholar] [CrossRef]

- Liao, C. Mobility impact on compensation performance of AMOLED pixel circuit using IGZO TFTs. J. Semicond. 2019, 40, 022403. [Google Scholar] [CrossRef]

- Arai, T.; Sasaoka, T. 49.1: Invited Paper: Emergent Oxide TFT Technologies for Next-Generation AM-OLED Displays. SID Symp. Dig. Tech. Pap. 2011, 42, 710–713. [Google Scholar] [CrossRef]

- Jang, Y.H.; Kim, D.H.; Choi, W.; Kang, M.-G.; Chun, K.I.; Jeon, J.; Ko, Y.; Choi, U.; Lee, S.-M.; Bae, J.U.; et al. 7-4: Invited Paper: Internal Compensation Type OLED Display Using High Mobility Oxide TFT. SID Symp. Dig. Tech. Pap. 2017, 48, 76–79. [Google Scholar] [CrossRef]

- Nomura, K.; Takagi, A.; Kamiya, T.; Ohta, H.; Hirano, M.; Hosono, H. Amorphous Oxide Semiconductors for High-Performance Flexible Thin-Film Transistors. Jpn. J. Appl. Phys. 2006, 45, 4303–4308. [Google Scholar] [CrossRef]

- Chong, E.; Chun, Y.S.; Lee, S.Y. Amorphous silicon–indium–zinc oxide semiconductor thin film transistors processed below 150 °C. Appl. Phys. Lett. 2010, 97, 102102. [Google Scholar] [CrossRef]

- Kizu, T.; Aikawa, S.; Mitoma, N.; Shimizu, M.; Gao, X.; Lin, M.F.; Nabatame, T.; Tsukagoshi, K. Low-Temperature Processable Amorphous In-WO Thin-Film Transistors with High Mobility and Stability. Appl. Phys. Lett. 2014, 104, 152103. [Google Scholar] [CrossRef]

- Koike, K.; Hama, K.; Nakashima, I.; Takada, G.-Y.; Ozaki, M.; Ogata, K.-I.; Sasa, S.; Inoue, M.; Yano, M. Piezoelectric Carrier Confinement by Lattice Mismatch at ZnO/Zn0.6Mg0.4O Heterointerface. Jpn. J. Appl. Phys. 2004, 43, L1372–L1375. [Google Scholar] [CrossRef]

- Taniguchi, S.; Yokozeki, M.; Ikeda, M.; Suzuki, T.-K. Transparent Oxide Thin-Film Transistors Using n-(In2O3)0.9(SnO2)0.1/InGaZnO4 Modulation-Doped Heterostructures. Jpn. J. Appl. Phys. 2011, 50, 04DF11. [Google Scholar] [CrossRef]

- Jeon, S.; Kim, S.I.; Park, S.; Song, I.; Park, J.; Kim, S.; Kim, C. Low-Frequency Noise Performance of a Bilayer InZnO–InGaZnO Thin-Film Transistor for Analog Device Applications. IEEE Electron Device Lett. 2010, 31, 1128–1130. [Google Scholar] [CrossRef]

- Chong, E.; Lee, S.Y. Influence of a highly doped buried layer for HfInZnO thin-film transistors. Semicond. Sci. Technol. 2011, 27, 12001. [Google Scholar] [CrossRef]

- Kim, H.-S.; Park, J.S.; Jeong, H.-K.; Son, K.S.; Kim, T.S.; Seon, J.-B.; Lee, E.; Chung, J.G.; Kim, D.H.; Ryu, M.; et al. Density of States-Based Design of Metal Oxide Thin-Film Transistors for High Mobility and Superior Photostability. ACS Appl. Mater. Interfaces 2012, 4, 5416–5421. [Google Scholar] [CrossRef] [PubMed]

- Jung, H.Y.; Kang, Y.; Hwang, A.Y.; Lee, C.K.; Han, S.; Kim, D.-H.; Bae, J.-U.; Shin, W.-S.; Jeong, J.K. Origin of the improved mobility and photo-bias stability in a double-channel metal oxide transistor. Sci. Rep. 2014, 4, 3765. [Google Scholar] [CrossRef] [Green Version]

- Yang, J.H.; Choi, J.H.; Cho, S.H.; Pi, J.E.; Kim, H.O.; Hwang, C.S.; Park, K.C.; Yoo, S. Highly Stable AlInZnSnO and InZnO Double-Layer Oxide Thin-Film Transistors With Mobility Over 50 cm2/V·s for High-Speed Operation. IEEE Electron Device Lett. 2018, 39, 508–511. [Google Scholar] [CrossRef]

- Park, J.C.; Lee, H.-N. Improvement of the Performance and Stability of Oxide Semiconductor Thin-Film Transistors Using Double-Stacked Active Layers. IEEE Electron Device Lett. 2012, 33, 818–820. [Google Scholar] [CrossRef]

- Saito, N.; Miura, K.; Ueda, T.; Tezuka, T.; Ikeda, K. High-Mobility and H2-Anneal Tolerant InGaSiO/InGaZnO/InGaSiO Double Hetero Channel Thin Film Transistor for Si-LSI Compatible Process. IEEE J. Electron Devices Soc. 2018, 6, 500–505. [Google Scholar] [CrossRef]

- Furuta, M.; Koretomo, D.; Magari, Y.; Aman, S.G.M.; Higashi, R.; Hamada, S.; Hamada, S. Heterojunction channel engineering to enhance performance and reliability of amorphous In–Ga–Zn–O thin-film transistors. Jpn. J. Appl. Phys. 2019, 58, 090604. [Google Scholar] [CrossRef]

- Suko, A.; Jia, J.; Nakamura, S.-I.; Kawashima, E.; Utsuno, F.; Yano, K.; Shigesato, Y. Crystallization behavior of amorphous indium–gallium–zinc-oxide films and its effects on thin-film transistor performance. Jpn. J. Appl. Phys. 2016, 55, 35504. [Google Scholar] [CrossRef]

- Ide, K.; Nomura, K.; Hiramatsu, H.; Kamiya, T.; Hosono, H. Structural relaxation in amorphous oxide semiconductor, a–In–Ga–Zn–O. J. Appl. Phys. 2012, 111, 073513. [Google Scholar] [CrossRef]

- Kim, J.; Bang, J.; Nakamura, N.; Hosono, H. Ultra-wide bandgap amorphous oxide semiconductors for NBIS-free thin-film transistors. APL Mater. 2019, 7, 022501. [Google Scholar] [CrossRef] [Green Version]

- Kim, J.; Hiramatsu, H.; Hosono, H.; Kamiya, T. Effects of sulfur substitution in amorphous InGaZnO4: Optical properties and first-principles calculations. J. Ceram. Soc. Jpn. 2015, 123, 537–541. [Google Scholar] [CrossRef] [Green Version]

- Kim, J.; Miyokawa, N.; Sekiya, T.; Ide, K.; Toda, Y.; Hiramatsu, H.; Hosono, H.; Kamiya, T. Ultrawide band gap amorphous oxide semiconductor, Ga–Zn–O. Thin Solid Films 2016, 614, 84–89. [Google Scholar] [CrossRef] [Green Version]

- Magari, Y.; Hashimoto, S.; Hamada, K.; Furuta, M. Low-Temperature Processed Metal-Semiconductor Field-Effect Transistor with In–Ga–Zn–O/AgOx Schottky Gate. ECS Trans. 2016, 75, 139–144. [Google Scholar] [CrossRef]

- Sze, S.M.; Ng, K.K. Physics of Semiconductor Devices, 3rd ed.; Wiley: New York, NY, USA, 2007. [Google Scholar]

- Lee, N.H.; Nomura, K.; Kamiya, T.; Hosono, H. Metal-Semiconductor Field-Effect Transistor Made Using Amorphous In-Ga-Zn-O Channel and Bottom Pt Schottky Contact Structure at 200 C. ECS Solid State Lett. 2012, 1, Q8–Q10. [Google Scholar] [CrossRef]

- Kamiya, T.; Hosono, H. (Invited) Roles of Hydrogen in Amorphous Oxide Semiconductor. ECS Trans. 2013, 54, 103–113. [Google Scholar] [CrossRef]

- Jeong, J.; Hong, Y. Debye Length and Active Layer Thickness-Dependent Performance Variations of Amorphous Oxide-Based TFTs. IEEE Trans. Electron Devices 2012, 59, 710–714. [Google Scholar] [CrossRef]

- Abe, K.; Sato, A.; Takahashi, K.; Kumomi, H.; Kamiya, T.; Hosono, H. Mobility- and temperature-dependent device model for amorphous In–Ga–Zn–O thin-film transistors. Thin Solid Films 2014, 559, 40–43. [Google Scholar] [CrossRef]

- Kamiya, T.; Nomura, K.; Hosono, H. Origins of High Mobility and Low Operation Voltage of Amorphous Oxide TFTs: Electronic Structure, Electron Transport, Defects and Doping. J. Disp. Technol. 2009, 5, 273–288. [Google Scholar] [CrossRef]

- Kim, Y.; Bae, M.; Kim, W.; Kong, D.; Jung, H.K.; Kim, H.; Kim, S.; Kim, D.M.; Kim, D.H. Amorphous InGaZnO Thin-Film Transistors—Part I: Complete Extraction of Density of States Over the Full Subband-Gap Energy Range. IEEE Trans. Electron Devices 2012, 59, 2689–2698. [Google Scholar] [CrossRef]

- Kim, S.; Jeon, Y.W.; Kim, Y.; Kong, D.; Jung, H.K.; Bae, M.-K.; Lee, J.-H.; Du Ahn, B.; Park, S.Y.; Park, J.-H.; et al. Impact of Oxygen Flow Rate on the Instability Under Positive Bias Stresses in DC-Sputtered Amorphous InGaZnO Thin-Film Transistors. IEEE Electron Device Lett. 2011, 33, 62–64. [Google Scholar] [CrossRef]

| IGZO-High-In Thickness | 2.5 nm | 5 nm | 10 nm | 15 nm | 20 nm |

|---|---|---|---|---|---|

| IGZO-111 Thickness | 10 nm | ||||

| μFE (cm2 V−1 s−1) | 9.9 | 17.2 | 19.6 | 21.8 | 21.3 |

| S.S. (V/dec.) | 0.10 | 0.10 | 0.10 | 0.12 | 0.15 |

| Vth (V) | 0 | −0.9 | −0.9 | −3.3 | −5.1 |

| VH (V) | 0.0 | 0.0 | 0.0 | 0.0 | 0.0 |

| Symbol | Value (IGZO) | Unit | Description | |

|---|---|---|---|---|

| −111 | -High-In | |||

| NC | 5.0 × 1018 | 5.0 × 1018 | cm−3 | Effective conduction band density of states |

| μd0 | 14 | 30 | cm2 V−1 s−1 | Intrinsic electron mobility |

| nCR | 1.0 × 1020 | 1.0 × 1020 | cm−3 | Critical electron density |

| Tγ | 178.4 | 178.4 | K | γ temperature |

| γ0 | −0.31 | −0.31 | — | Gamma at 1/T = 0 |

| Wga | 0.7 | 1.2 | eV | Decay energy of acceptor-like Gaussian trap |

| Wgd | 0.12 | 0.12 | eV | Decay energy of donor-like Gaussian trap |

| Ega | 0 | 0 | eV | Mean energy of Gaussian acceptor-like trap |

| Egd | 2.6 | 2.2 | eV | Mean energy of Gaussian donor-like trap |

| Nga | 1.5 × 1017 | 1.5 × 1017 | cm−3 ev−1 | Peak density of Gaussian acceptor-like trap |

| Ngd | 1.3 × 1017 | 1.3 × 1017 | cm−3 ev−1 | Peak density of Gaussian donor-like trap |

| Nta | 1.0 × 1019 | 1.0 × 1019 | cm−3 ev−1 | Acceptor-like tail trap density |

| Ntd | 3.0 × 1019 | 3.0 × 1019 | cm−3 ev−1 | Donor-like tail trap density |

| Wta | 0.01 | 0.01 | eV | Slope of acceptor-like tail trap |

| Wtd | 0.1 | 0.1 | eV | Slope of donor-like tail trap |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Koretomo, D.; Hamada, S.; Magari, Y.; Furuta, M. Quantum Confinement Effect in Amorphous In–Ga–Zn–O Heterojunction Channels for Thin-Film Transistors. Materials 2020, 13, 1935. https://doi.org/10.3390/ma13081935

Koretomo D, Hamada S, Magari Y, Furuta M. Quantum Confinement Effect in Amorphous In–Ga–Zn–O Heterojunction Channels for Thin-Film Transistors. Materials. 2020; 13(8):1935. https://doi.org/10.3390/ma13081935

Chicago/Turabian StyleKoretomo, Daichi, Shuhei Hamada, Yusaku Magari, and Mamoru Furuta. 2020. "Quantum Confinement Effect in Amorphous In–Ga–Zn–O Heterojunction Channels for Thin-Film Transistors" Materials 13, no. 8: 1935. https://doi.org/10.3390/ma13081935

APA StyleKoretomo, D., Hamada, S., Magari, Y., & Furuta, M. (2020). Quantum Confinement Effect in Amorphous In–Ga–Zn–O Heterojunction Channels for Thin-Film Transistors. Materials, 13(8), 1935. https://doi.org/10.3390/ma13081935