Improvement in Electrical Stability of a-IGZO TFTs Using Thinner Dual-Layer Dielectric Film

Abstract

:1. Introduction

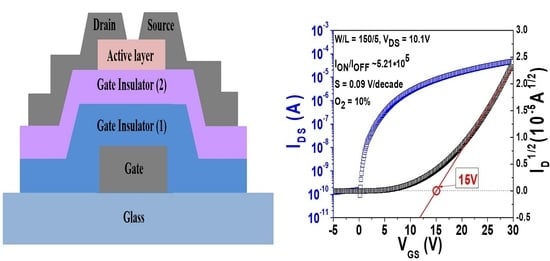

2. Materials and Methods

3. Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef]

- Hosono, H. Ionic amorphous oxide semiconductors: Material design, carrier transport, and device application. J. Non-Cryst. Solids 2006, 352, 851–858. [Google Scholar] [CrossRef]

- Yabuta, H.; Sano, M.; Abe, K.; Aiba, T.; Den, T.; Kumomi, H.; Nomura, K.; Kamiya, T.; Hosono, H. High-mobility thin-film transistor with amorphous In Ga Zn O4 channel fabricated by room temperature rf-magnetron sputtering. Appl. Phys. Lett. 2006, 89, 112123. [Google Scholar] [CrossRef]

- Nomura, K.; Kamiya, T.; Ohta, H.; Uruga, T.; Hirano, M.; Hosono, H. Local coordination structure and electronic structure of the large electron mobility amorphous oxide semiconductor In-Ga-Zn-O: Experiment and ab initio calculations. Phys. Rev. B 2007, 75, 035212. [Google Scholar] [CrossRef]

- Sheng, J.; Hong, T.; Lee, H.; Kim, K.; Sasase, M.; Kim, J.; Hosono, H.; Park, J. Amorphous IGZO TFT with High Mobility of ~70 cm2/(V s) via Vertical Dimension Control Using PEALD. ACS Appl. Mater. Interfaces 2019, 11, 40300–40309. [Google Scholar] [CrossRef]

- Lee, J.; Kim, D.; Yang, D.; Hong, S.; Yoon, K.; Hong, P.; Jeong, C.; Park, H.; Kim, S.Y.; Lim, S.K. 42.2: World’s Largest (15-inch) XGA AMLCD Panel Using IGZO Oxide TFT. SID Symp. Dig. Tech. Pap. 2008, 39, 625–628. [Google Scholar] [CrossRef]

- Hayashi, R.; Sato, A.; Ofuji, M.; Abe, K.; Yabuta, H.; Sano, M.; Kumomi, H.; Nomura, K.; Kamiya, T.; Hirano, M. 42.1: Invited Paper: Improved Amorphous In-Ga-Zn-O TFTs. SID Symp. Dig. Tech. Pap. 2008, 39, 621–624. [Google Scholar] [CrossRef]

- Park, S.K.; Ryu, M.; Hwang, C.; Yang, S.; Byun, C.; Lee, J.; Shin, J.; Yoon, S.M.; Chu, H.Y.; Cho, K.I. 42.3: Transparent ZnO thin film transistor for the application of high aperture ratio bottom emission AM-OLED display. SID Symp. Dig. Tech. Pap. 2008, 39, 629–632. [Google Scholar] [CrossRef]

- Takechi, K.; Nakata, M.; Eguchi, T.; Yamaguchi, H.; Kaneko, S. Temperature-dependent transfer characteristics of amorphous InGaZnO4 thin-film transistors. Jpn. J. Appl. Phys. 2009, 48, 11301. [Google Scholar] [CrossRef]

- Takechi, K.; Nakata, M.; Eguchi, T.; Yamaguchi, H.; Kaneko, S. Comparison of ultraviolet photo-field effects between hydrogenated amorphous silicon and amorphous InGaZnO4 thin-film transistors. Jpn. J. Appl. Phys. 2009, 48, 10203. [Google Scholar] [CrossRef]

- Kimura, M.; Nakanishi, T.; Nomura, K.; Kamiya, T.; Hosono, H. Trap densities in amorphous-In Ga Zn O 4 thin-film transistors. Appl. Phys. Lett. 2008, 92, 133512. [Google Scholar] [CrossRef]

- Kim, D.; Cho, W. Effects of Rapid Thermal Annealing on the Conduction of a-IGZO Films. J. Korean Inst. Electr. Electron. Mater. Eng. 2016, 29, 11–16. [Google Scholar]

- Park, J.; Kim, C.S.; Kim, Y.S.; Park, Y.C.; Park, H.J.; Bae, B.; Park, J.; Kim, H. The effect of ITO and Mo electrodes on the properties and stability of In-Ga-Zn-O thin film transistors. J. Electroceram. 2016, 36, 129–134. [Google Scholar] [CrossRef]

- Kong, H.; Cho, K.; Lee, H.; Lee, S.; Lim, J.; Kim, S. Bias-stress stability of top-gate coplanar a-ITGZO TFTs with HfO2 and HfAlO gate dielectrics. Mater. Sci. Semicond. Processing 2022, 143, 106527. [Google Scholar] [CrossRef]

- Carlos, E.; Branquinho, R.; Kiazadeh, A.; Barquinha, P.; Martins, R.; Fortunato, E. UV-Mediated Photochemical Treatment for Low-Temperature Oxide-Based Thin-Film Transistors. ACS Appl. Mater. Interfaces 2016, 8, 31100–31108. [Google Scholar] [CrossRef]

- Carlos, E.; Leppäniemi, J.; Sneck, A.; Alastalo, A.; Deuermeier, J.; Branquinho, R.; Martins, R.; Fortunato, E. Printed, Highly Stable Metal Oxide Thin-Film Transistors with Ultra-Thin High-k Oxide Dielectric. Adv. Electron. Mater. 2020, 6, 1901071. [Google Scholar] [CrossRef]

- Dong, C.; Liu, G.; Zhang, Y.; Feng, G.; Zhou, Y. Double-stacked gate insulators SiOx/TaOx for flexible amorphous InGaZnO thin film transistors. Mater. Sci. Semicond. Processing 2019, 96, 99–103. [Google Scholar] [CrossRef]

- Beom, K.; Yang, P.; Park, D.; Kim, H.J.; Lee, H.H.; Kang, C.J.; Yoon, T. Single- and double-gate synaptic transistor with TaOx gate insulator and IGZO channel layer. Nanotechnology 2018, 30, 025203. [Google Scholar] [CrossRef]

- Jauhari, I.M.; Bak, Y.G.; Noviyana, I.; Putri, M.A.; Lee, J.A.; Heo, Y.W.; Lee, H.Y. Electrical properties of amorphous indium zinc tin oxide thin film transistor with Y2O3 gate dielectric. J. Nanosci. Nanotechnol. 2021, 21, 1748–1753. [Google Scholar] [CrossRef]

- Choi, W.; Jeon, W.; Park, J. Nanoscale surface engineering of a high-k ZrO2/SiO2 gate insulator for a high performance ITZO TFT via plasma-enhanced atomic layer deposition. J. Mater. Chem. C 2020, 8, 13342–13348. [Google Scholar] [CrossRef]

- DiStefano, T.H.; Eastman, D.E. The band edge of amorphous SiO2 by photoinjection and photoconductivity measurements. Solid State Commun. 1971, 9, 2259–2261. [Google Scholar] [CrossRef]

- Green, M.L.; Sorsch, T.W.; Timp, G.L.; Muller, D.A.; Weir, B.E.; Silverman, P.J.; Moccio, S.V.; Kim, Y.O. Understanding the limits of ultrathin SiO2 and Si O N gate dielectrics for sub-50 nm CMOS. Microelectron. Eng. 1999, 48, 25–30. [Google Scholar] [CrossRef]

- Martins, J.; Kiazadeh, A.; Pinto, J.V.; Rovisco, A.; Goncalves, T.; Deuermeier, J.; Alves, E.; Martins, R.; Fortunato, E.; Barquinha, P. Ta2O5/SiO2 Multicomponent Dielectrics for Amorphous Oxide TFTs. Electron. Mater. 2021, 2, 1–16. [Google Scholar] [CrossRef]

- Hubbard, K.J.; Schlom, D.G. Thermodynamic stability of binary oxides in contact with silicon. J. Mater. Res. 1996, 11, 2757–2776. [Google Scholar] [CrossRef]

- Billman, C.A.; Tan, P.H.; Hubbard, K.J.; Schlom, D.G. Alternate gate oxides for silicon MOSFETs using high-K dielectrics. MRS Online Proc. Libr. 1999, 567, 409–414. [Google Scholar] [CrossRef]

- Wang, L.; Yoon, M.; Lu, G.; Yang, Y.; Facchetti, A.; Marks, T.J. High-performance transparent inorganic–organic hybrid thin-film n-type transistors. Nat. Mater. 2006, 5, 893–900. [Google Scholar] [CrossRef] [PubMed]

- Noh, S.H.; Choi, W.; Oh, M.S.; Hwang, D.K.; Lee, K.; Im, S. ZnO-based nonvolatile memory thin-film transistors with polymer dielectric/ferroelectric double gate insulators. Appl. Phys. Lett. 2007, 90, 253504. [Google Scholar] [CrossRef]

- Sasa, S.; Ozaki, M.; Koike, K.; Yano, M.; Inoue, M. High-performance Zn O∕Zn Mg O field-effect transistors using a hetero-metal-insulator-semiconductor structure. Appl. Phys. Lett. 2006, 89, 053502. [Google Scholar] [CrossRef]

- Lee, K.; Kim, J.H.; Im, S. Low-voltage-driven top-gate ZnO thin-film transistors with polymer/high-k oxide double-layer dielectric. Appl. Phys. Lett. 2006, 89, 133507. [Google Scholar] [CrossRef]

- Oh, M.S.; Hwang, D.K.; Kimoon, L.; Im, S. Low voltage complementary thin-film transistor inverters with pentacene-ZnO hybrid channels on AlO𝑥 dielectric. Appl. Phys. Lett. 2007, 90, 173511. [Google Scholar] [CrossRef]

- Dhananjay; Krupanidhi, S.B. Low threshold voltage ZnO thin film transistor with a Zn0.7Mg0.3O gate dielectric for transparent electronics. J. Appl. Phys. 2007, 101, 123717. [Google Scholar] [CrossRef]

- De Souza, M.M.; Jejurikar, S.; Adhi, K.P. Impact of aluminum nitride as an insulator on the performance of zinc oxide thin film transistors. Appl. Phys. Lett. 2008, 92, 093509. [Google Scholar] [CrossRef]

- Zhang, L.; Li, J.; Zhang, X.W.; Jiang, X.Y.; Zhang, Z.L. High-performance ZnO thin film transistors with sputtering SiO2/Ta2O5/SiO2 multilayer gate dielectric. Thin Solid Films 2010, 518, 6130–6133. [Google Scholar] [CrossRef]

- Carlos, E.; Branquinho, R.; Kiazadeh, A.; Martins, J.; Barquinha, P.; Martins, R.; Fortunato, E. Boosting Electrical Performance of High-k Nanomultilayer Dielectrics and Electronic Devices by Combining Solution Combustion Synthesis and UV Irradiation. ACS Appl. Mater. Interfaces 2017, 9, 40428–40437. [Google Scholar] [CrossRef] [PubMed]

- Shimura, Y.; Nomura, K.; Yanagi, H.; Kamiya, T.; Hirano, M.; Hosono, H. Specific contact resistances between amorphous oxide semiconductor In-Ga-Zn-O and metallic electrodes. Thin Solid Films 2008, 516, 5899–5902. [Google Scholar] [CrossRef]

- Verlaak, S.; Arkhipov, V.; Heremans, P. Modeling of transport in polycrystalline organic semiconductor films. Appl. Phys. Lett. 2003, 82, 745–747. [Google Scholar] [CrossRef]

- Völkel, A.R.; Street, R.A.; Knipp, D. Carrier transport and density of state distributions in pentacene transistors. Phys. Rev. B 2002, 66, 195336. [Google Scholar] [CrossRef]

- Valletta, A.; Mariucci, L.; Fortunato, G.; Brotherton, S.D. Surface-scattering effects in polycrystalline silicon thin-film transistors. Appl. Phys. Lett. 2003, 82, 3119–3121. [Google Scholar] [CrossRef]

| Gate Insulator | On/Off Ratio | SS (V/Decade) | μsat (cm2/Vs) |

|---|---|---|---|

| Ta2O5 | 8.77 × 106 | 1.6 | 8.4 |

| SiO2/Ta2O5 | 2.12 × 107 | 1.3 | 11.3 |

| SiO2 | 5.21 × 105 | 2.7 | 0.6 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, J.-W.; Seo, H.K.; Lee, S.Y.; Park, M.; Yang, M.K.; Ju, B.-K. Improvement in Electrical Stability of a-IGZO TFTs Using Thinner Dual-Layer Dielectric Film. Metals 2022, 12, 1663. https://doi.org/10.3390/met12101663

Kim J-W, Seo HK, Lee SY, Park M, Yang MK, Ju B-K. Improvement in Electrical Stability of a-IGZO TFTs Using Thinner Dual-Layer Dielectric Film. Metals. 2022; 12(10):1663. https://doi.org/10.3390/met12101663

Chicago/Turabian StyleKim, Jong-Woo, Hyun Kyu Seo, Su Yeon Lee, Minsoo Park, Min Kyu Yang, and Byeong-Kwon Ju. 2022. "Improvement in Electrical Stability of a-IGZO TFTs Using Thinner Dual-Layer Dielectric Film" Metals 12, no. 10: 1663. https://doi.org/10.3390/met12101663

APA StyleKim, J. -W., Seo, H. K., Lee, S. Y., Park, M., Yang, M. K., & Ju, B. -K. (2022). Improvement in Electrical Stability of a-IGZO TFTs Using Thinner Dual-Layer Dielectric Film. Metals, 12(10), 1663. https://doi.org/10.3390/met12101663